2024-07-11

한어Русский языкEnglishFrançaisIndonesianSanskrit日本語DeutschPortuguêsΕλληνικάespañolItalianoSuomalainenLatina

Hoc contentus fundaturJiangxie Technology STM32 videoContentus, constituto.

| type | serial numerus | bus | Officium |

|---|---|---|---|

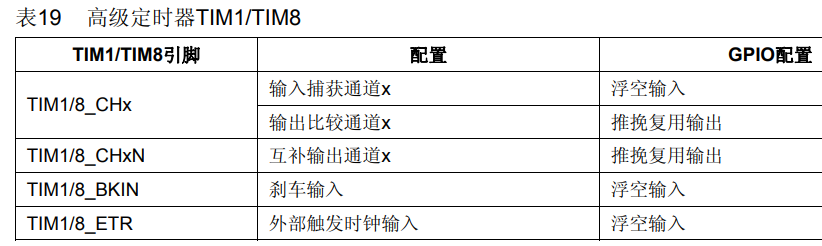

| Provecta timor | TIM1、TIM8 | APB2 | Habet omnia munera timoris generalis, ac praeterea functiones repetitionis calculo, zonae mortuae generationis, output complementarium, input fregit, etc. |

| universalis timor | TIM2、TIM3、TIM4、TIM5 | APB1 | Omnia functiones timoris fundamentalis habet, et habet functiones additas sicut fons horologii interni et externi delectu, inputa captio, output comparationis, encoder interface, modum felis domini-servi, etc. |

| basic timer | TIM6、TIM7 | APB1 | Munera habet scheduled interpellandi et magister modus excitato DAC |

Praecipuum munus:

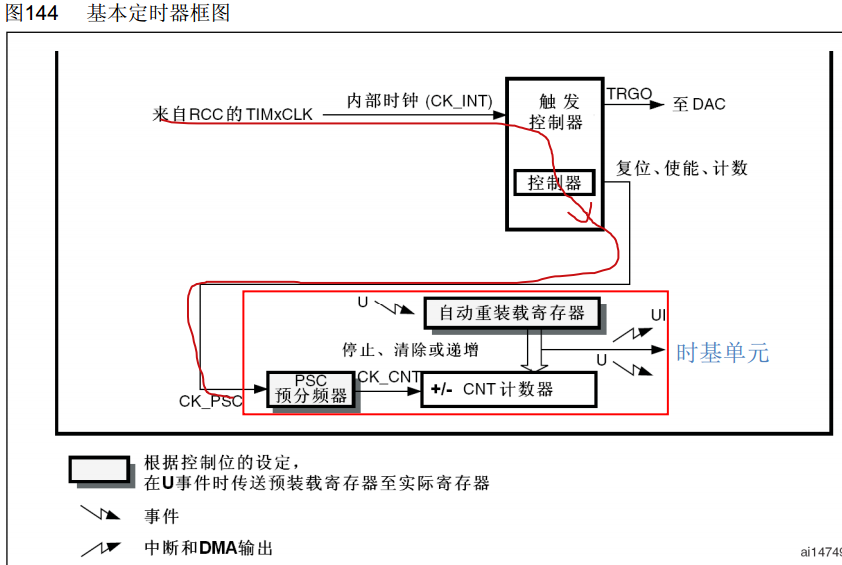

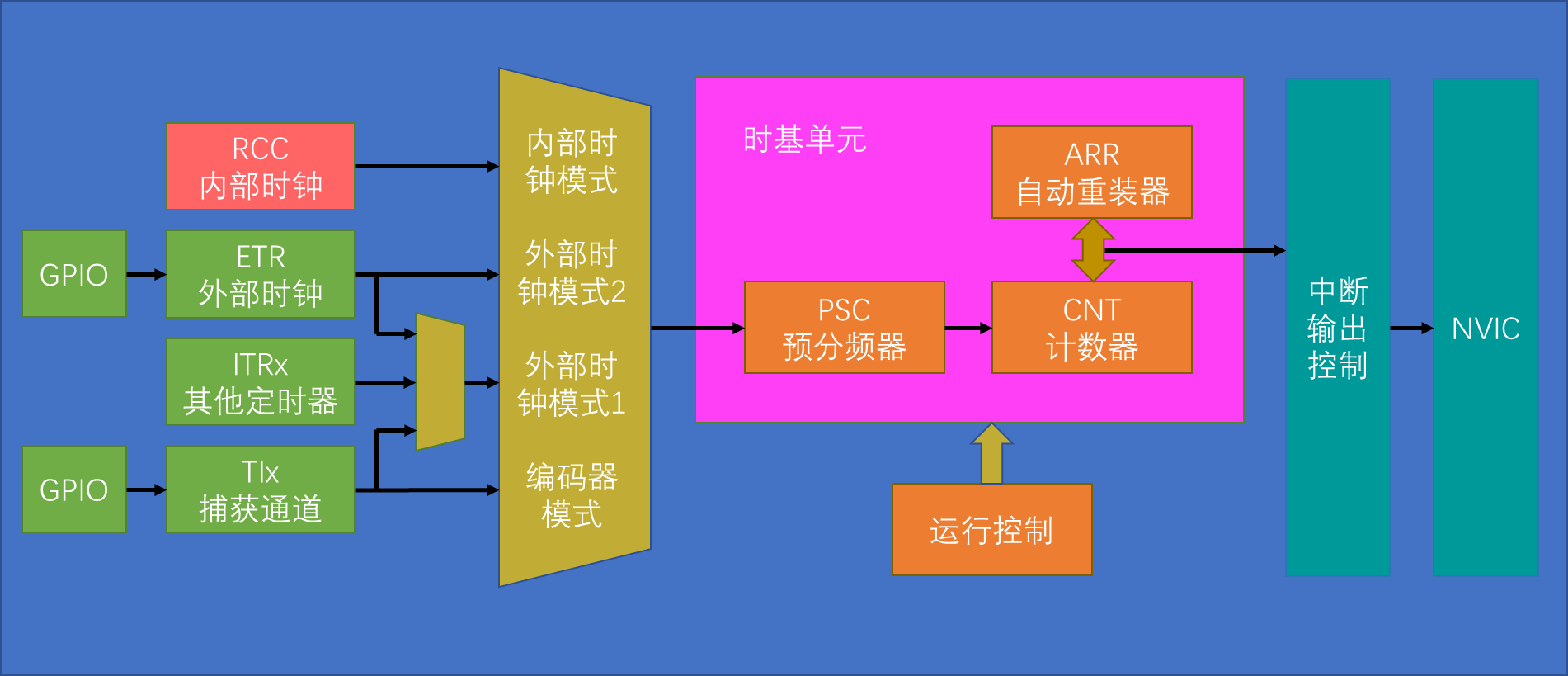

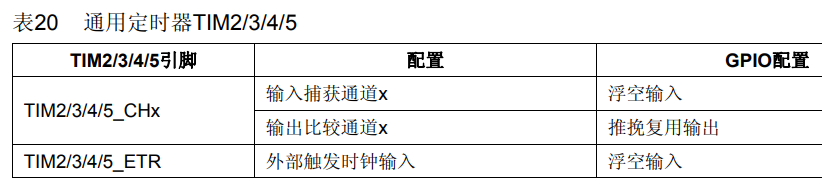

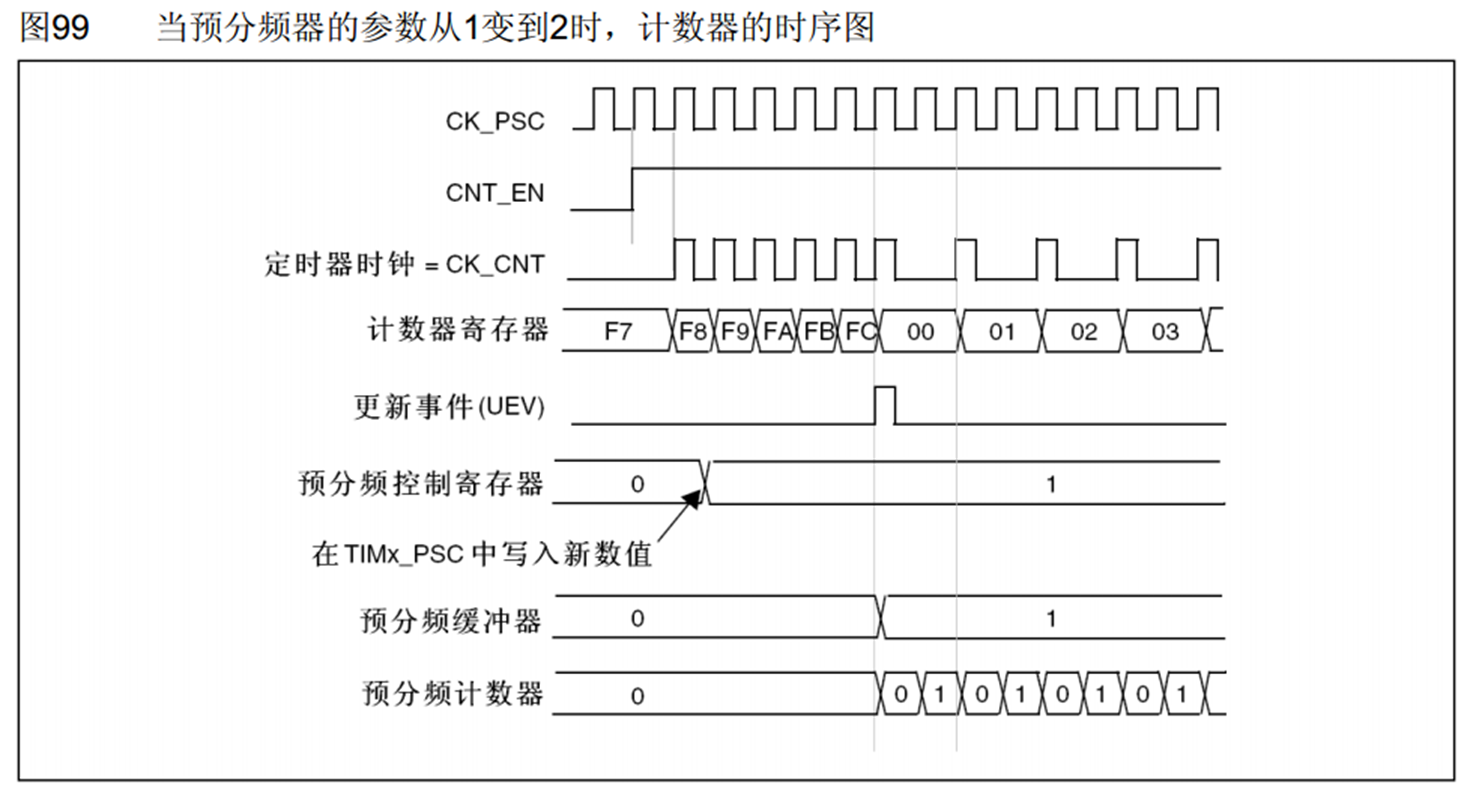

Prescaler PSC

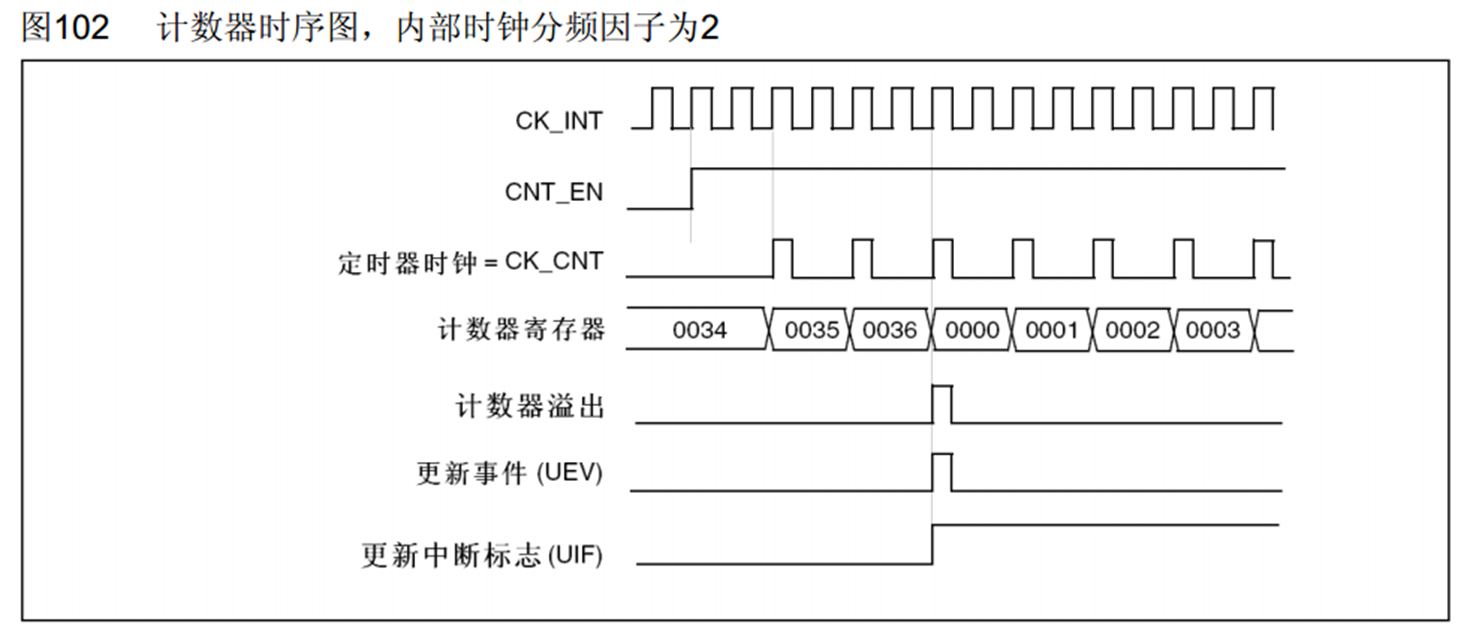

Inputatio relationis comitem horologii ante precatorem iungitur. Cum timor fundamentalis nonnisi horologium internum eligere potest, linea precatoris initus considerari potest cum horologio interno coniungi (CK_INT).

Fons horologii interni est RCC's TIMxCLK.

Scriptura 0 in presclator nullam frequentiam divisionem significat;

Scriptura 2 significat dividere per 3, et output = input/3. Ergo valor presclatoris differt ab actu frequentiae divisionis coefficientis per 1 , et actualis frequentia divisionis coefficientis = valor prescali 1 . Praescaler est 16 frusta, ergo maximi pretii pro 65535 scribi potest, qui dividitur per 65536 .

Contra CNT

Peripatetici potest computare ante horologii numerationem praedivisam. Quotiens horologium numerans ad marginem ascendentem venit, valorem calculo per 1 auget. Peripatetici etiam 16 frusta sunt, ergo valor intus ab 0 ad 65535 addi potest. Si plura addita sunt, occurro ad 0 revertetur et rursus incipiet. Ergo valor calculi perget incremento in processu numerando. Cum incrementum ad valorem scopum attingit, interruptio generabitur et opus horarium perficietur. Ideo opus est actis mandare ut scopum valorem reponat, quod est actis mandare reload automatic.

Lorem reload mandare

In registro auto- reload est etiam XVI frusta, et clypeum comiti scribendum reponit. In processu currit, valorem comitis augere pergit, et reload valor scopus fixum est. Tunc signum interruptionis generabit, calculum purgabis, et calculus tunc temporis numerans statim incipiet.

U et III sagittis

Sagitta sursum ducta in tabula significat quod signum interruptum hic generabitur. Haec renovatio interruptio ad NVIC ducet. Cum timerem canalem NVIC configuramus, renovatio interrumpere in CPU respondebitur. Sagitta prona significat eventum generari, et eventus hic congruens eventus appellatur "renovatio". Renovatio eventus non felis obloquitur, sed operari potest trigger aliorum circulorum internorum.

Praecipuum munus:

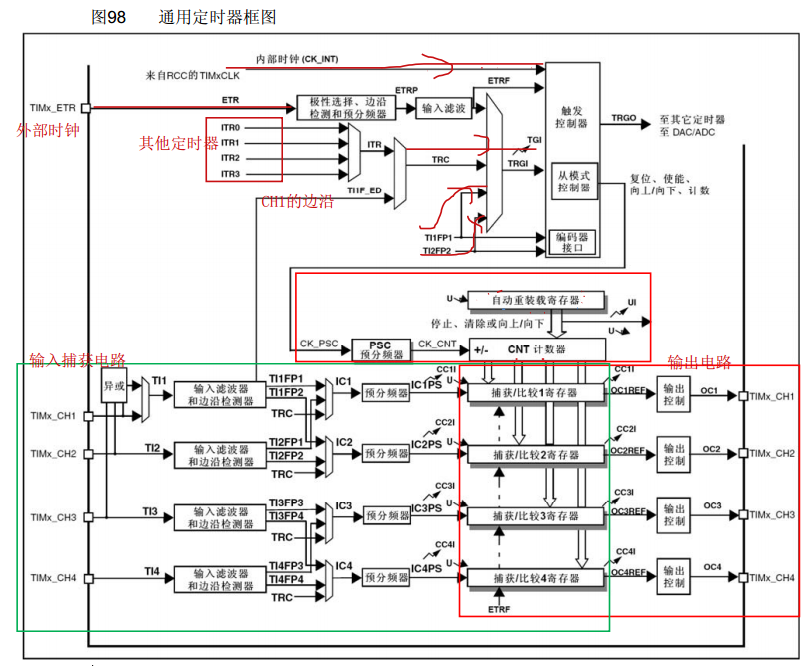

16-bit sursum, deorsum, sursum/sursum auto- reload accumulator counter

16-bit praescalarius programmabilis, horologium initus dividere solebat quavis valore inter 1 et 65536 .

4 canales independentes:

Synchronisation circuitus qui timers et timers controlant utentes significationibus externis

Interpellare / DMA generatur cum sequentia fiunt:

Sustinet incrementalem (quadraturam) encoder et aula sensorem circuitus pro positioning

Felis input ut extra horologium vel cyclum-by-cyclus current procuratio

CNT counter

CNT counter sustinet modum numerandi, descendendi modum numerandi, et alignment centrum modum. Modus numerandi deorsum incipit a reload valorem et decrementa deorsum. Modus centri-alignus incipit ab 0, primum incrementa sursum, valorem reload numerat, et interpellationem postulat, deinde decrementa deorsum ad 0, ac deinde pro interruptione adhibet.

horologium fons

Fons horologii generalis timoris non solum 72MHz horologium internum eligere potest, sed etiam horologium externum eligere potest.

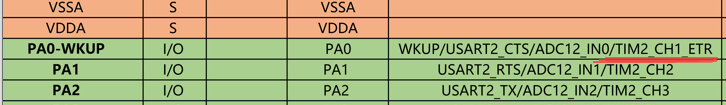

(1)Primum horologium externum est aHorologium externum in TIMx_ETR pin , hoc est, cum externam quadratam undam horologii AD ETR clavum TIM2, PA0 coniungere potes, ac deinde deprehensionem internam electionis, ora detectionis et circuii prescalatoris, necnon input colum circuli matione quadam. Quia externum clavum horologii est, necessario erit glitches quidam, ideo hi circuitus initus waveformi eliquare possunt. Signum colum in duos canales dividitur. Haec via etiam vocatur "Externi horologii modus 2”。

(2) TRGI etiam externum horologium praebere potest , maxime adhibitum ut felis input. Cum TRGI ad horologium externum adhibetur, haec via appellatur "Externi horologii modus 1". Quid sunt horologii externi per hunc canalem transeunte? Primum signum est acus ETR. Secundum est signum ITR. Haec pars horologii signum ab aliis timentibus venit. TRGO in mode magistro ducere potest. cum aliis timers coniungens, iungitur cum ITR paxillis aliorum timentium. CH1 paxillus, hoc est, horologium ex CH1 clavo obtinetur. Suffixum ED (Edge) hic significat in margine ad CH2 clavum.

Summarium: Initus ad horologii externi modum 1 potest esse ETR paxillus, alii timers, extrema CH1 paxillus, paxillus CH1, CH2 paxillus.

Comparatio circuitus output

Pars dextra infra ambitum comparationis output est. Quattuor canales sunt in total, pinis CH1 ad CH4 respondentes, qui possunt ad output PWM waveforms adhiberi et motores pellere.

Input captis circuit

A sinistra initus est prehensio circuitus, qui etiam quattuor canales habet, respondens fibulae CH1 ad CH4, quae frequentiam input quadratam undam metiri possunt, etc.

captis / compare mandare

Medium actis mandare est captio/compare registri, quod communicatur per input captionem et output circuitus comparationis. Quia input captio et output comparatio simul adhiberi non potest, libri hic communicantur et paxillos etiam communes sunt.

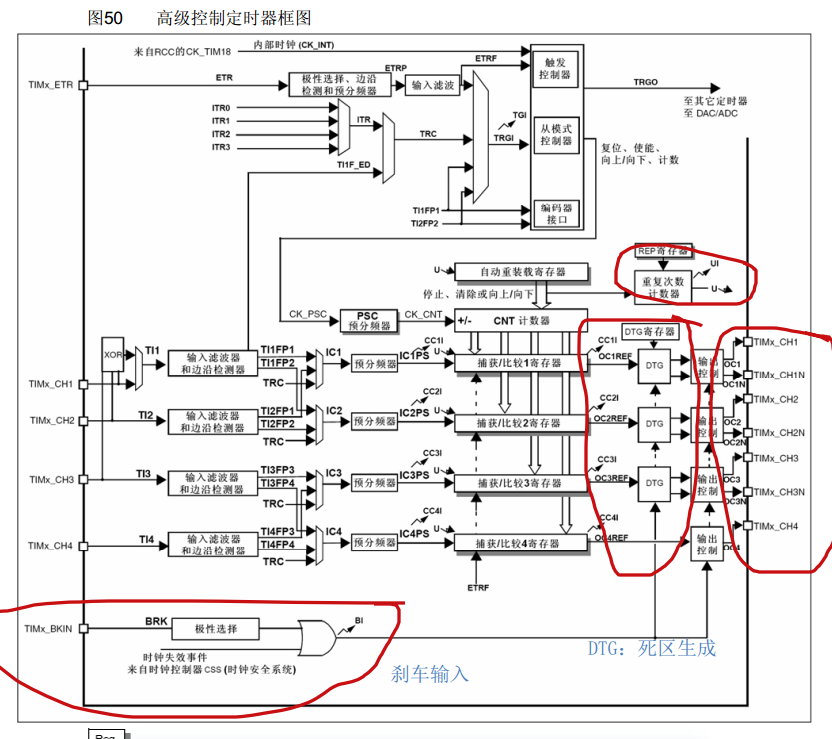

Praecipuum munus:

Repetere contra

Discrimen a timore generali: primum adde repetitionem dictioni ubi interpellatio adhibetur. Cum hoc calculo percipere potest quod renovatio eventus et renovatio interrumpuntur solum in omnibus paucis cyclis numerandis. Primigenia structura est quod renovatio fiet post unumquemque cyclum numerationem peractam, quae aequivalet signo renovationis extraordinario iterum dividendo.

DTG deadband generantis et complementaria output

Sequens est upgrade progressionis moduli comparationis per timer provectus. Output clavum in dextera ab originali una ad duas outputationes complementarias mutatum est, quae par PWM undis complementariis outputare possunt. vehicula, et terebras electrica. Quia in circuitu motoris tres phases setis motoriis plerumque 3 arma pontis requirit, uterque pons bracchium 2 summus potentiae mutandi tube refrenatur, ideo summa potentiae mutandi fistulae 6 summae requiruntur. Primae ergo tres output PWM fibulae hic fiunt outputs completiva. Praeterea, ne breve tempus surculus per phaenomenon per imperfectiones machinae causatur in momento mutandi, cum output PWM complementarium pontem bracchium agitet, zona generationis mortuae ambitus anteriori additur. In momento, cum transitum mutatur, zona mortua certae temporis generatur, permittens tum superiorem tum inferiorem fistulae pontis bracchii ne transversas averti.

fregit initus

Ultima pars munus inputationis fregit, quod praesidium motoris coegi praestare. Si paxillus externus BKIN (BKIN IN) signum fractum generat, vel horologium internum deficit et culpa incidit, imperium circuii sponte abscindet output motoris ad accidentia praecavenda.

Currite imperium: frena in registro regere, ut incipiunt et desinunt, numera sursum vel deorsum, etc.

Dextrum latus est ubi signum incedit post tempus leo et renovatio interrumpere generatur. Signum interpellandi primum frenum vexillum interruptum in statu actis mandabit. Hoc frenum vexillum per interpellationem output continebitur et interpellationem NVIC applicabit. Interrumpere output imperium est dare frenum pro interpellare output.

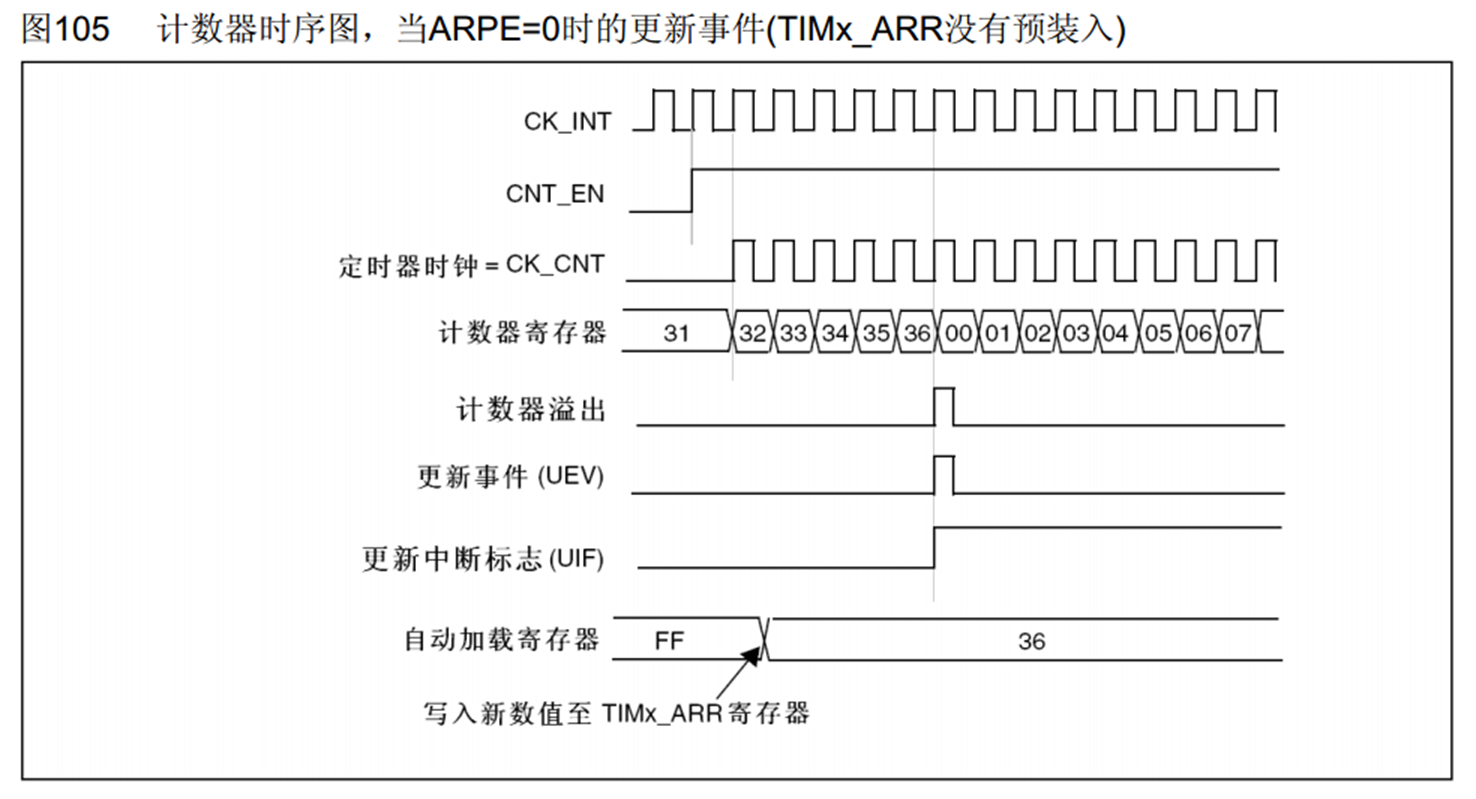

Mandatum auto- oneratione ab FF ad 36, mutatum est, et scopus valoris quantitatis comitis ab FF ad 36 mutatus est, ergo postquam 36 hic computatis, proxime renovabitur ut proximam numerandi rationem incipiet.

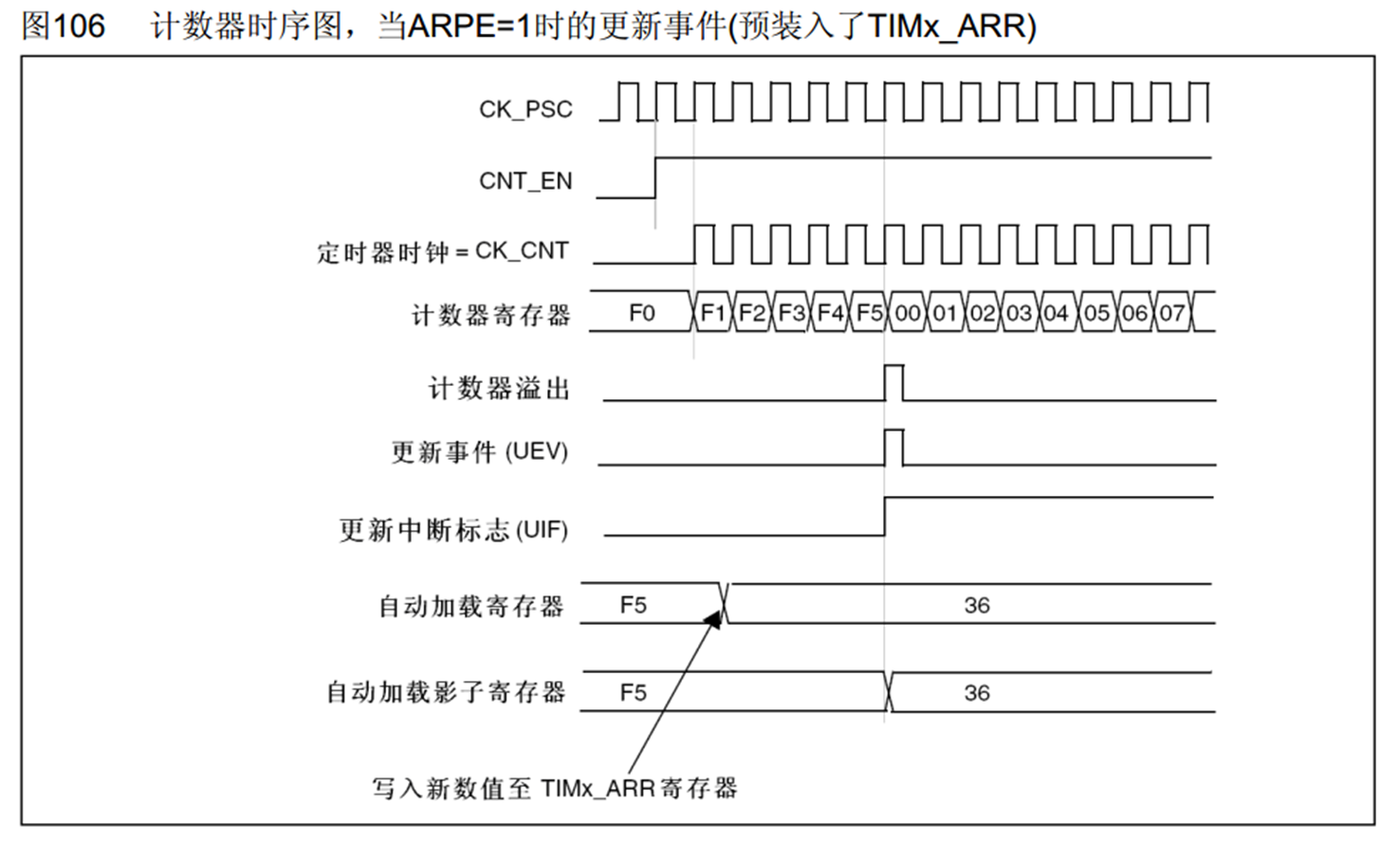

In medio numerandi, muta scopum valorem numerandi ab F5 ad 36 . Subcriptio umbrae subest. Haec umbra registri vere efficax est. Est adhuc F5, ergo iam numerus scopus adhuc F5 computat, eventum renovationis generans subcriptio, et in altera narratione Haec mutatio tantum valet, si cyclus est 36, ut finis introducendi umbram registri revera synchronisationi est, id est, ut valoris mutationes et renovatio eventus synchrone occurrant, ne errores ex mutationibus inducantur. in operatione.

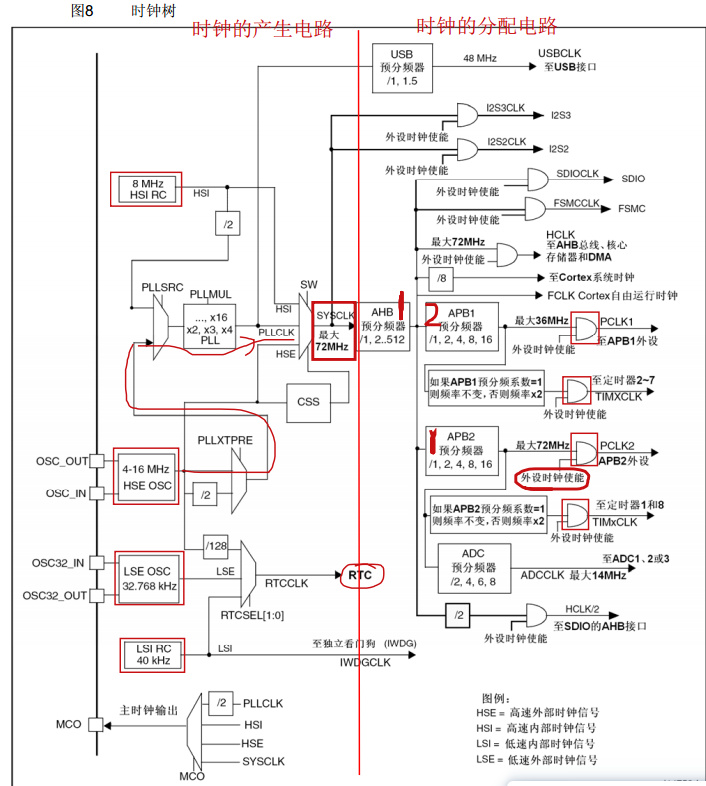

horologium fons

In circulo generationis horologii quatuor sunt fontes oscillationis;

(1) HSI: Internus 8MHz summus velocitatis RC oscillator;

(2) HSE: Externus 4~16MHz vicus crystallus summus velocitatis oscillator, qui etiam oscillator cristallinus notus, cum 8MHz coniungi solet;

(3) LSE: Externi 32.768KHz celeritas gravis crystalli oscillatoris, quae plerumque praebet horologium RTC;

(4) LSI: Denique internus 40KHz velocitas RC oscillator est humilis, qui horologium cani praebere potest.

Supra duo cristalli velocitatis oscillatores adhibentur ad systema horologiorum RC oscillator, ut vulgo oscillator crystalli externus utere.

Configuratio horologii ST

In munere SystemInit, ST horologium conformat: primum horologium internum HSI incipit, internum 8MHz ut horologii rationem deligit, et ad tempus cum interno 8MHz horologium decurrit. Tunc horologium externum incipe, horologium externum configurare ad ansam PLL Phase clausae frequentiae multiplicationis, 8MHz 9 vicibus multiplicatur, et 72MHz accipis output ut horologii systematis, ut horologii systema ab 8MHz ad 72MHz switched.

CSS Pro Securitatis System

CSS (ratio securitatis horologii): Horologii securitatis ratio etiam in commutatione horologiorum cavenda est. Potest monitorem statum currens externi horologii systematis horologii et ne programmatis adhaesit Mors per accidens.

horologium distribution circuitu

*2ac deinde separatim pro timers 2-7 aperitur, quia prescaler hic coefficiens est 2, ita hic frequentia esse debet.*2 sic horologium ad timers 2~7 est 72MHz. Sive ergo est timor provectus, timor generalis sive timor praecipuus, earum relatio interna horologii est 72MHz.*2 . Quia frequentia divisio coefficiens est 1, horologia timentium 1 et 8 sunt 72MHz.// 恢复缺省配置

void TIM_DeInit(TIM_TypeDef* TIMx);

// 时基单元初始化

void TIM_TimeBaseInit(TIM_TypeDef* TIMx, TIM_TimeBaseInitTypeDef* TIM_TimeBaseInitStruct);

// 结构体变量赋一个默认值

void TIM_TimeBaseStructInit(TIM_TimeBaseInitTypeDef* TIM_TimeBaseInitStruct);

// 使能计数器---运行控制

void TIM_Cmd(TIM_TypeDef* TIMx, FunctionalState NewState);

// 使能中断输出---中断输出控制

void TIM_ITConfig(TIM_TypeDef* TIMx, uint16_t TIM_IT, FunctionalState NewState);

/*-----------------时基单元的时钟选择---------*/

// 选择内部时钟

void TIM_InternalClockConfig(TIM_TypeDef* TIMx);

// 选择ITRx其他定时器的时钟

void TIM_ITRxExternalClockConfig(TIM_TypeDef* TIMx, uint16_t TIM_InputTriggerSource);

// 选择TIx捕获通道的时钟

void TIM_TIxExternalClockConfig(TIM_TypeDef* TIMx, uint16_t TIM_TIxExternalCLKSource,

uint16_t TIM_ICPolarity, uint16_t ICFilter);

// 选择ETR通过外部时钟模式1输入的时钟

void TIM_ETRClockMode1Config(TIM_TypeDef* TIMx, uint16_t TIM_ExtTRGPrescaler, uint16_t TIM_ExtTRGPolarity,

uint16_t ExtTRGFilter);

// 选择ETR通过外部时钟模式2输入的时钟

void TIM_ETRClockMode2Config(TIM_TypeDef* TIMx, uint16_t TIM_ExtTRGPrescaler,

uint16_t TIM_ExtTRGPolarity, uint16_t ExtTRGFilter);

/*--------------------------------------------------------*/

// 不是用来选择时钟的,单独用来配置ETR引脚的预分频器、极性、滤波参数的

void TIM_ETRConfig(TIM_TypeDef* TIMx, uint16_t TIM_ExtTRGPrescaler, uint16_t TIM_ExtTRGPolarity,

uint16_t ExtTRGFilter);

// 用来单独写预分频值的

void TIM_PrescalerConfig(TIM_TypeDef* TIMx, uint16_t Prescaler, uint16_t TIM_PSCReloadMode);

// 用来改变计数器的计数模式

void TIM_CounterModeConfig(TIM_TypeDef* TIMx, uint16_t TIM_CounterMode);

// 自动重装器预装功能配置

void TIM_ARRPreloadConfig(TIM_TypeDef* TIMx, FunctionalState NewState);

// 给计数器写入一个值

void TIM_SetCounter(TIM_TypeDef* TIMx, uint16_t Counter);

// 给自动重装器写入一个值

void TIM_SetAutoreload(TIM_TypeDef* TIMx, uint16_t Autoreload);

// 获取当前计数器的值

uint16_t TIM_GetCounter(TIM_TypeDef* TIMx);

// 获取当前的预分频器的值

uint16_t TIM_GetPrescaler(TIM_TypeDef* TIMx);

/*-------------获取标志位和清除标志位的------------*/

FlagStatus TIM_GetFlagStatus(TIM_TypeDef* TIMx, uint16_t TIM_FLAG);

void TIM_ClearFlag(TIM_TypeDef* TIMx, uint16_t TIM_FLAG);

ITStatus TIM_GetITStatus(TIM_TypeDef* TIMx, uint16_t TIM_IT);

void TIM_ClearITPendingBit(TIM_TypeDef* TIMx, uint16_t TIM_IT);