2024-07-11

한어Русский языкEnglishFrançaisIndonesianSanskrit日本語DeutschPortuguêsΕλληνικάespañolItalianoSuomalainenLatina

एषा सामग्री आधारिता अस्तिJiangxie प्रौद्योगिकी STM32 videoसामग्री, संगठित।

| प्रकारः | क्रमाङ्कः | बस | नियोग |

|---|---|---|---|

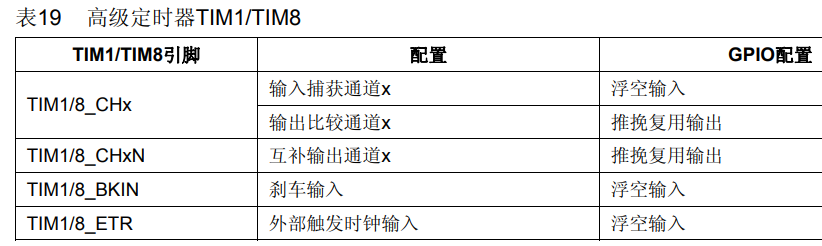

| उन्नत समयनिर्धारक | तिम्१、तिम्८ | APB2 | अस्मिन् सामान्यसमयनिर्धारकस्य सर्वाणि कार्याणि सन्ति, अतिरिक्तरूपेण पुनरावृत्तिगणकस्य, मृतक्षेत्रजननस्य, पूरकनिर्गमस्य, ब्रेकनिवेशस्य इत्यादीनां कार्याणि सन्ति |

| सार्वभौमिक समयनिर्धारक | टिम२、तिम३、तिम४、तिम५ | APB1 | अस्मिन् मूलभूतसमयनिर्धारकस्य सर्वाणि कार्याणि सन्ति, तथा च अतिरिक्तकार्यं भवति यथा आन्तरिकबाह्यघटिकास्रोतचयनं, इनपुट्-कॅप्चर्, आउटपुट्-तुलना, एन्कोडर-अन्तरफलकं, मास्टर-स्लेव्-ट्रिगर-मोड् इत्यादयः |

| मूलभूतसमयनिर्धारकः | तिम्६、तिम्७ | APB1 | DAC ट्रिगरिंग् कृत्वा scheduled interrupt तथा master mode इत्यस्य कार्याणि सन्ति |

मुख्यं कार्यम् : १.

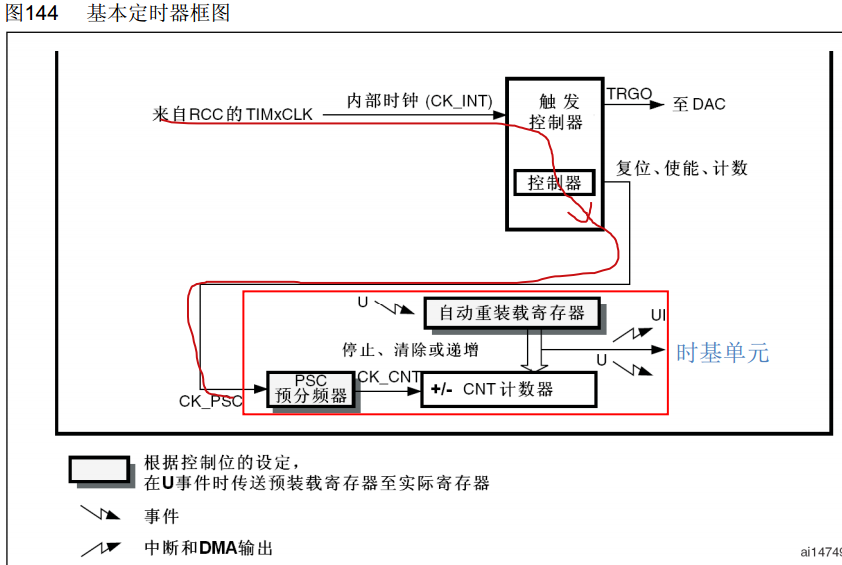

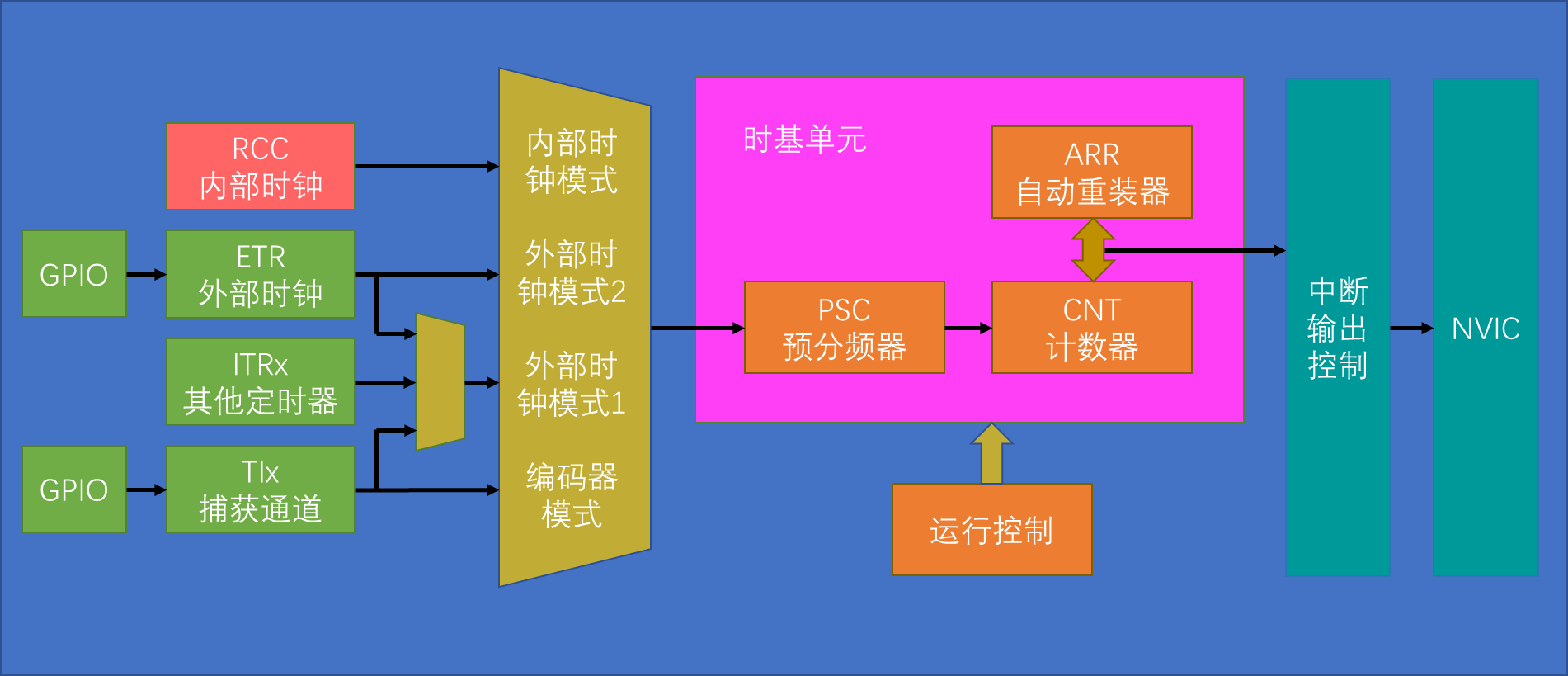

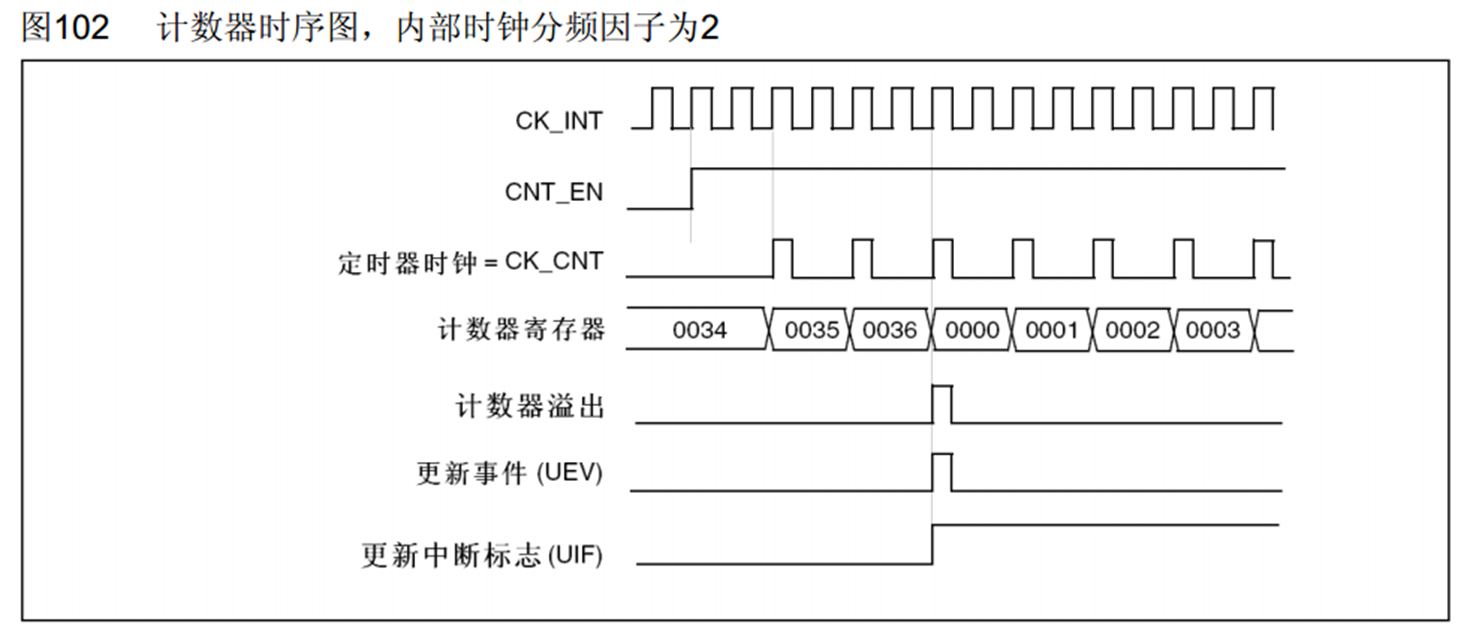

प्रीस्केलर पीएससी

सन्दर्भगणनाघटिकायाः निवेशः पूर्वस्केलर् इत्यस्मात् पूर्वं सम्बद्धः भवति । यतः मूलभूतसमयनिर्धारकः केवलं आन्तरिकघटिकायाः चयनं कर्तुं शक्नोति, पूर्वस्केलरस्य निवेशरेखा आन्तरिकघटिकायाः (CK_INT) सह सम्बद्धा इति गणयितुं शक्यते ।

आन्तरिकघटिकायाः स्रोतः RCC इत्यस्य TIMxCLK अस्ति अत्र आवृत्तिमूल्यं सामान्यतया 72MHz इत्यस्य प्रणाल्याः मुख्या आवृत्तिः भवति ।

प्रीस्केलरमध्ये 0 इति लेखनस्य अर्थः अस्ति यत् आवृत्तिविभाजनं नास्ति;

२ इति लेखनस्य अर्थः ३ इत्यनेन विभाजनं भवति, तथा च आउटपुट् = इनपुट्/३ । अतः पूर्वमापकस्य मूल्यं वास्तविक आवृत्तिविभाजनगुणांकात् १ द्वारा भिद्यते, तथा च वास्तविकः आवृत्तिविभागगुणकः = पूर्वमापकस्य मूल्यं १ भवति प्रीस्केलर १६ बिट् अस्ति, अतः अधिकतमं मूल्यं ६५५३५ इति लिखितुं शक्यते, यत् ६५५३६ इत्यनेन विभक्तम् अस्ति ।

काउंटर सीएनटी

गणकः पूर्वविभक्तगणनाघटिकां गणयितुं शक्नोति प्रत्येकं गणनाघटिका उदयमानधारं प्रति आगच्छति तदा गणकमूल्यं 1 वर्धते । गणकः अपि १६ बिट् अस्ति, अतः अन्तः मूल्यं ० तः ६५५३५ पर्यन्तं योजयितुं शक्यते । यदि अधिकानि योजिताः सन्ति तर्हि गणकः 0 प्रति आगत्य पुनः आरभेत । अतः गणनाप्रक्रियायाः समये गणकस्य मूल्यं निरन्तरं वर्धते यदा वृद्धिः लक्ष्यमूल्यं प्राप्नोति तदा व्यत्ययः उत्पद्यते, निर्धारितं कार्यं च सम्पन्नं भविष्यति अतः लक्ष्यमूल्यं संग्रहीतुं रजिस्टरस्य आवश्यकता भवति, यत् स्वचालितं पुनः लोड् रजिस्टर् अस्ति ।

स्वचालित पुनः लोड रजिस्टर

स्वतः-पुनर्भार-पञ्जिका अपि १६ बिट् भवति, तथा च एतत् लेखनीयं गणनालक्ष्यं संगृह्णाति । चालनप्रक्रियायाः समये गणनामूल्यं निरन्तरं वर्धते, स्वचालितपुनर्भारमूल्यं च नियतलक्ष्यं भवति यदा गणनामूल्यं स्वचालितपुनर्भारमूल्येन समानं भवति तदा समयसमयः समाप्तः भवति ततः एतत् व्यत्ययसंकेतं जनयिष्यति, गणकं स्वच्छं करिष्यति, गणकः स्वयमेव अग्रिमगणनासमयं आरभेत ।

U तथा UI बाणाः

चित्रे आकृष्टस्य ऊर्ध्वगामिनि छूटबाणस्य अर्थः अस्ति यत् अत्र व्यत्ययसंकेतः उत्पद्यते यस्य गणनामूल्यं स्वचालितपुनर्भारमूल्येन सह सामान्यतया "अद्यतनव्यत्ययः एतत् अपडेट् व्यत्ययं NVIC -पर्यन्तं नेष्यति एकवारं वयं NVIC इत्यस्य टाइमर-चैनल-विन्यस्तं कुर्मः तदा टाइमर्-इत्यस्य अपडेट्-व्यत्ययस्य प्रतिक्रिया CPU द्वारा भविष्यति । अधोगतिः बाणः दर्शयति यत् कश्चन घटना उत्पद्येत, अत्र तत्सम्बद्धं घटना "update event" इति उच्यते । अद्यतनघटनानि व्यत्ययं न प्रेरयन्ति, परन्तु अन्येषां आन्तरिकपरिपथानाम् कार्यं प्रेरयितुं शक्नुवन्ति ।

मुख्यं कार्यम् : १.

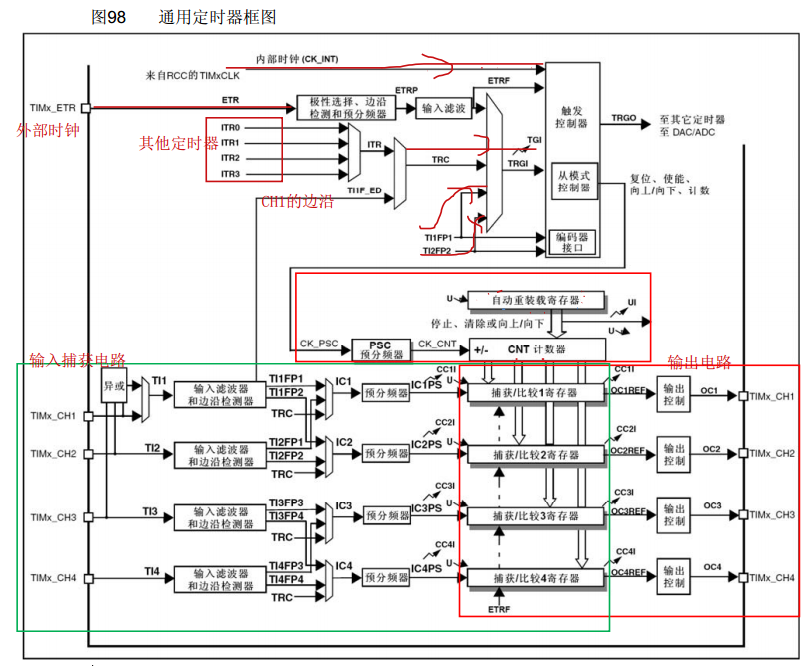

१६-बिट् उपरि, अधः, उपरि/ऊर्ध्वं स्वतः पुनः लोड् सञ्चयकगणकं

१६-बिट् प्रोग्रामेबल प्रीस्केलर, यस्य उपयोगः इनपुट् घण्टां १ तः ६५५३६ पर्यन्तं किमपि मूल्येन विभक्तुं भवति

४ स्वतन्त्रमार्गाः : १.

समन्वयनपरिपथाः ये बाह्यसंकेतानां उपयोगेन समयनिर्धारकाणां समयनिर्धारकाणां च परस्परसंयोजनानि नियन्त्रयन्ति

यदा निम्नलिखितघटनानि भवन्ति तदा Interrupt/DMA उत्पद्यते:

स्थितिनिर्धारणाय वृद्धिशील (द्विघात) एन्कोडर तथा हॉल संवेदक परिपथानाम् समर्थनं करोति

बाह्यघटिका अथवा चक्र-चक्र-वर्तमान-प्रबन्धनरूपेण निवेशं प्रवर्तयन्तु

सीएनटी काउण्टर

CNT counter up counting mode, down counting mode, center alignment mode च समर्थयति । अधः गमनविधिः पुनः लोड् मूल्यात् आरभ्य अधः न्यूनीभवति ततः परं पुनः लोड् मूल्यं प्रति आगच्छति तथा च व्यत्ययस्य कृते प्रवर्तते । केन्द्र-संरेखितः मोडः 0 तः आरभ्यते, प्रथमं ऊर्ध्वं वर्धयति, पुनः भारमूल्यं गणयति, व्यत्ययस्य कृते प्रयोजयति, ततः अधः 0 यावत् न्यूनीकरोति, ततः व्यत्ययस्य कृते प्रवर्तते

घड़ी स्रोतः

सामान्यसमयनिर्धारकस्य घण्टास्रोतः न केवलं आन्तरिकं 72MHz घण्टां चिन्वितुं शक्नोति, अपितु बाह्यघटिकां अपि चिन्वितुं शक्नोति ।

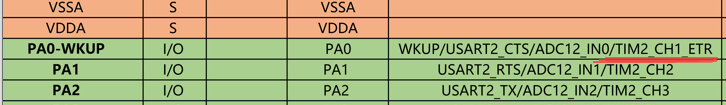

(1)प्रथमा बाह्यघटिका तः अस्तिTIMx_ETR पिन इत्यत्र बाह्यघटिका , अर्थात्, भवान् TIM2, PA0 इत्यस्य ETR पिन इत्यनेन सह बाह्यवर्गतरङ्गघटिकां संयोजयितुं शक्नोति, ततः आन्तरिकध्रुवताचयनं, धारपरिचयः, पूर्वस्केलरपरिपथं च विन्यस्तुं शक्नोति, तथैव इनपुट्-छिद्रपरिपथं च The clock undergoes निश्चित आकारः । यतः एषा बाह्यपिनघटिका अस्ति, अतः अनिवार्यतया केचन त्रुटिः भविष्यति, अतः एते परिपथाः निवेशतरङ्गरूपं छानयितुं शक्नुवन्ति । फ़िल्टर कृतः संकेतः द्वयोः चैनलयोः विभक्तः भवति । अयं मार्गः " " इति अपि उच्यते ।बाह्यघटिकाविधिः २”。

(2) TRGI बाह्यघटिका अपि प्रदातुं शक्नोति , मुख्यतया ट्रिगर इनपुट् इत्यस्य रूपेण उपयुज्यते एतत् ट्रिगर इनपुट् टाइमर् इत्यस्य स्लेव् मोड् ट्रिगर कर्तुं शक्नोति । यदा TRGI बाह्यघटिकारूपेण उपयुज्यते तदा एषः मार्गः " " इति उच्यते ।बाह्यघटिकाविधिः १". अस्मिन् मार्गे बाह्यघटिकाः कानि गच्छन्ति? प्रथमं ETR पिनस्य संकेतः अस्ति। द्वितीयः ITR संकेतः अस्ति। घण्टासंकेतस्य एषः भागः अन्येभ्यः समयनिर्धारकेभ्यः आगच्छति। मास्टर मोड् मध्ये TRGO इत्यनेन भवितुं शक्नोति अन्ये टाइमर्-इत्यनेन सह सम्बद्धं भवति चेत्, अन्यचतुर्णां टाइमर्-इत्यस्य TRGO-निर्गमात् ITR0-पर्यन्तं सम्बद्धं भवति, यत् अत्र इनपुट्-कॅप्चर-यूनिट्-सङ्गतम् अस्ति । CH1 पिन अर्थात् CH1 पिनतः घण्टा प्राप्ता भवति अत्र ED (Edge) इति प्रत्ययस्य अर्थः TI1FP1 इत्यस्य माध्यमेन अपि प्राप्तुं शक्यते तथा च TI1FP1 CH1 पिन इत्यनेन सह सम्बद्धा घड़ी अस्ति the CH2 pin.

सारांशः - बाह्यघटिकाविधाने 1 निवेशः ETR पिनः, अन्यसमयनिर्धारकः, CH1 पिनस्य धारः, CH1 पिनः, CH2 पिनः च भवितुम् अर्हति ।

आउटपुट तुलना परिपथ

अधोलिखितः दक्षिणः भागः आउटपुट् तुलनापरिपथः अस्ति, कुलम् चत्वारि चैनल्स् सन्ति, ये CH1 तः CH4 पर्यन्तं पिनस्य अनुरूपाः सन्ति, येषां उपयोगेन PWM तरङ्गरूपं आउटपुट् कर्तुं, मोटर् चालयितुं च शक्यते

इनपुट कैप्चर सर्किट

वामे इनपुट् कैप्चर सर्किट् अस्ति, यस्य चत्वारः चैनल्स् अपि सन्ति, ये CH1 तः CH4 पर्यन्तं पिन्स् इत्यस्य अनुरूपाः सन्ति, येषां उपयोगेन इनपुट् वर्गतरङ्गस्य आवृत्तिः इत्यादीनां मापनं कर्तुं शक्यते

capture/compare रजिस्टर

मध्यपञ्जिका कैप्चर/तुलना रजिस्टरः भवति, यः इनपुट् कैप्चर तथा आउटपुट् तुलना परिपथैः साझा भवति यतः इनपुट् कैप्चर तथा आउटपुट् तुलना एकस्मिन् समये उपयोक्तुं न शक्यते, अत्र रेजिस्टराः साझाः भवन्ति तथा च पिनः अपि साझाः भवन्ति

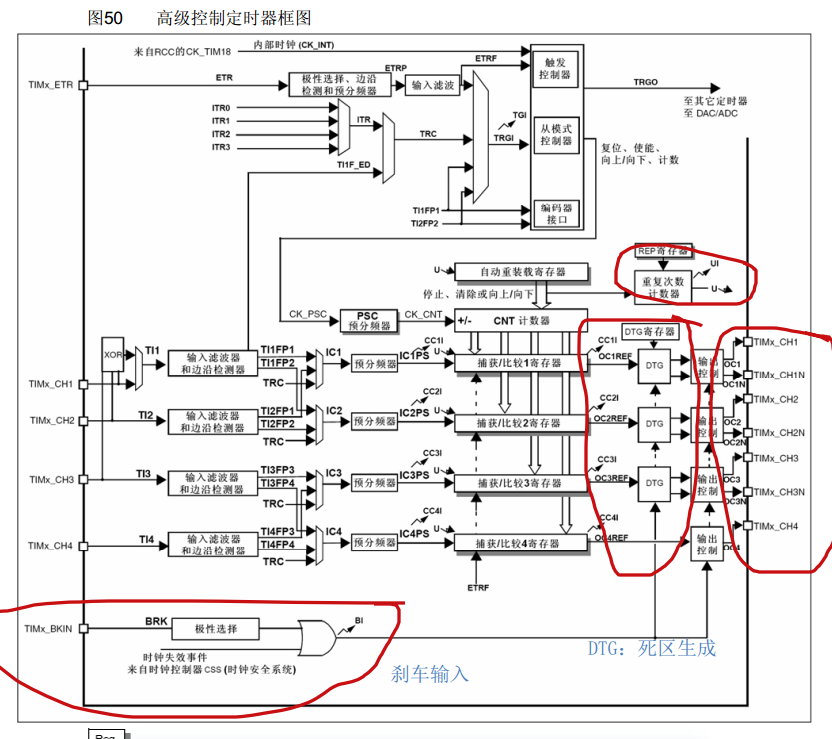

मुख्यं कार्यम् : १.

गणकं पुनः कुर्वन्तु

सामान्यसमयनिर्धारकात् भेदः : प्रथमं पुनरावृत्तिगणकं योजयितुं यत्र व्यत्ययः प्रयुक्तः भवति एतेन गणकेन एतत् अवगन्तुं शक्यते यत् अद्यतनघटनानि अद्यतनव्यवधानं च केवलं प्रत्येकं कतिपयेषु गणनाचक्रेषु भवन्ति मूलसंरचना अस्ति यत् प्रत्येकं गणनाचक्रस्य समाप्तेः अनन्तरं अद्यतनं भविष्यति, यत् पुनः आउटपुट् अपडेट् संकेतस्य विभाजनस्य बराबरम् अस्ति ।

DTG डेडबैण्ड जनरेटर तथा पूरक उत्पादन

निम्नलिखितम् उन्नतसमयनिर्धारकेण आउटपुट् तुलनामॉड्यूलस्य उन्नयनम् अस्ति DTG (dead time generate) इति मृतक्षेत्रजननपरिपथः अस्ति । दक्षिणतः आउटपुट् पिनः मूल एकतः पूरकनिर्गमद्वयं यावत् परिवर्तितः अस्ति, यत् पूरकपीडब्ल्यूएम तरङ्गयोः युग्मं निर्गन्तुं शक्नोति एतेषां परिपथानाम् उपयोगः त्रिचरणीय-ब्रश-रहित-मोटराणां चालनार्थं भवति, यथा क्वाडकॉप्टर-विमानं, विद्युत्-पृष्ठचक्राणि वाहनानि, विद्युत्-अभ्यासाः च प्रतीक्ष्यताम्, एतत् त्रिचरणीयं ब्रशरहितं मोटरं भवितुम् अर्हति । यतो हि त्रिचरणीयस्य ब्रशरहितस्य मोटरस्य चालनपरिपथस्य सामान्यतया ३ सेतुबाहुः आवश्यकः भवति, प्रत्येकं सेतुबाहुः २ उच्चशक्तियुक्तैः स्विचिंग् ट्यूबैः नियन्त्रितः भवति, अतः कुलम् ६ उच्चशक्तियुक्ताः स्विचिंग् ट्यूबाः आवश्यकाः भवन्ति अतः अत्र प्रथमत्रयस्य आउटपुट् PWM पिनस्य पूरकनिर्गमः भवति । तदतिरिक्तं, पूरकनिर्गमः PWM सेतुबाहुं चालयति चेत् स्विचिंग्-क्षणे यन्त्रस्य अपूर्णतायाः कारणेन अल्पकालीनशूट-थ्रू-घटनायाः निवारणाय अग्रे मृतक्षेत्रजननपरिपथः योजितः भवति यस्मिन् क्षणे स्विचः स्विच् भवति तस्मिन् क्षणे निश्चितकालस्य मृतक्षेत्रं उत्पद्यते, येन सेतुबाहुस्य उपरितनं च नलिकां निष्क्रियं कृत्वा शूट्-थ्रू निवारयितुं शक्यते

ब्रेक इनपुट

अन्तिमः भागः ब्रेक इनपुट् कार्यम् अस्ति, यत् मोटरड्राइवस्य सुरक्षायाः गारण्टीं दातुं भवति । यदि बाह्यपिन् BKIN (Break IN) ब्रेकसंकेतं जनयति, अथवा आन्तरिकघटिका विफलः भवति तथा च दोषः भवति तर्हि नियन्त्रणपरिपथः स्वयमेव दुर्घटनानिवारणाय मोटरस्य उत्पादनं कटयिष्यति

संचालननियन्त्रणम् : रजिस्टर् मध्ये केचन बिट् नियन्त्रयन्तु, यथा आरम्भः स्थगितश्च, उपरि वा अधः वा गणना इत्यादयः ।

दक्षिणभागः अस्ति यत्र समयसमयस्य समाप्तेः अनन्तरं संकेतः गच्छति तथा च अद्यतनव्यत्ययः उत्पद्यते यदि उन्नतसमयनिर्धारकः अस्ति तर्हि अतिरिक्तः पुनरावृत्तिगणकः भविष्यति । व्यत्ययसंकेतः प्रथमं स्थितिपञ्जिकायां व्यत्ययध्वजबिटं सेट् करिष्यति एषः ध्वजबिटः व्यत्ययनिर्गमस्य माध्यमेन नियन्त्रितः भविष्यति तथा च NVIC मध्ये व्यत्ययस्य कृते आवेदनं करिष्यति । Interrupt output control इति interrupt output कृते enable bit अस्ति यदि भवतः interrupt इत्यस्य आवश्यकता अस्ति तर्हि तस्य अनुमतिं दातुं स्मर्यताम् ।

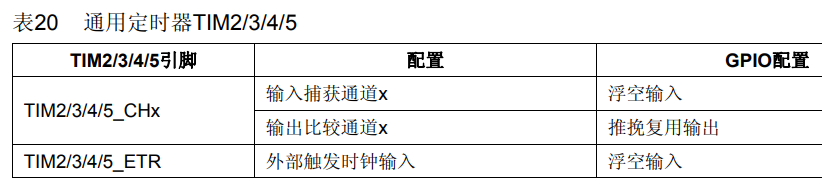

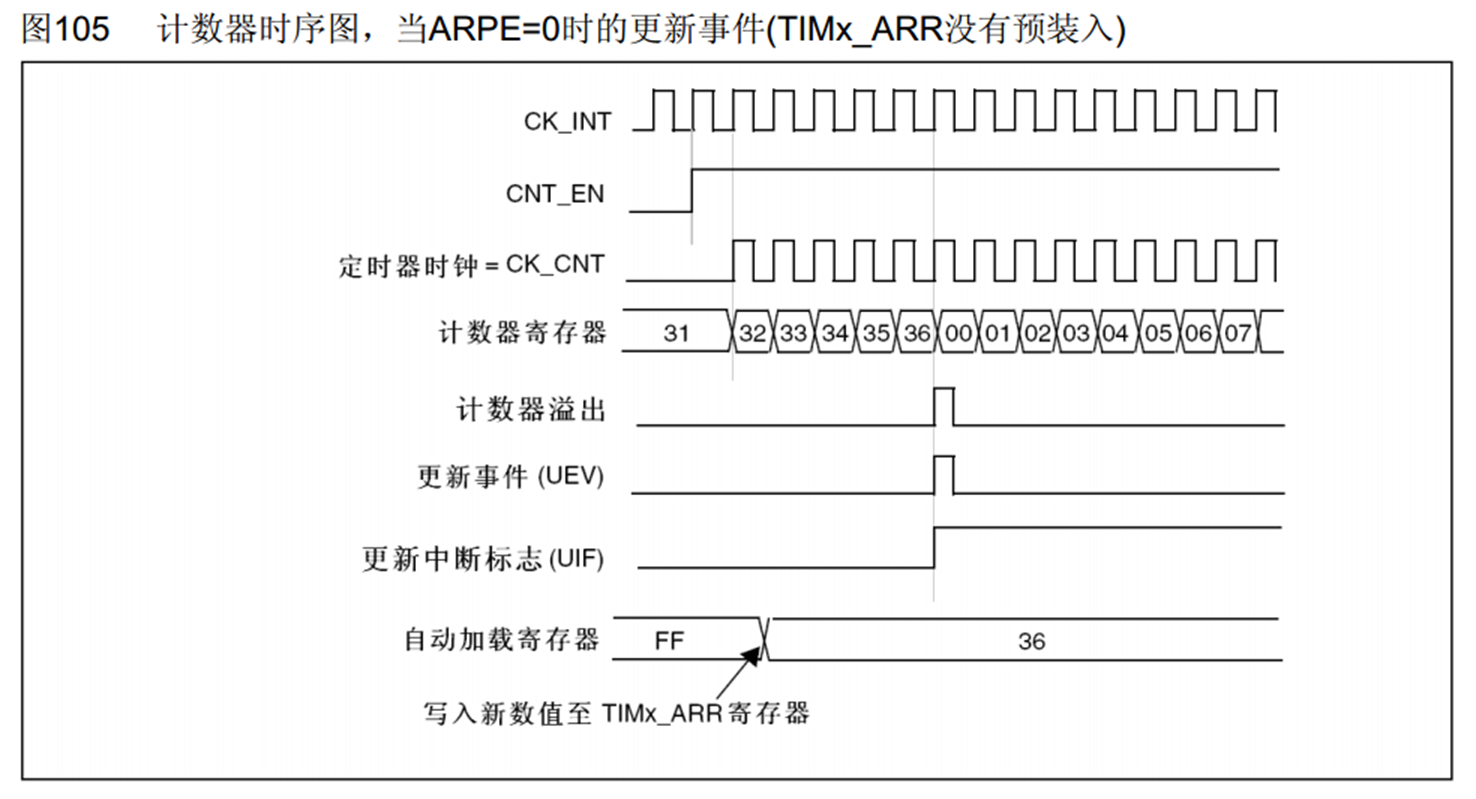

स्वतः-भार-पञ्जिका FF तः 36 यावत् परिवर्तिता अस्ति, तथा च गणनामूल्यस्य लक्ष्यमूल्यं FF तः 36 यावत् परिवर्तितम् अस्ति, अतः अत्र 36 गणयित्वा, गणनायाः अग्रिमपरिक्रमं आरभ्य प्रत्यक्षतया अद्यतनं भविष्यति

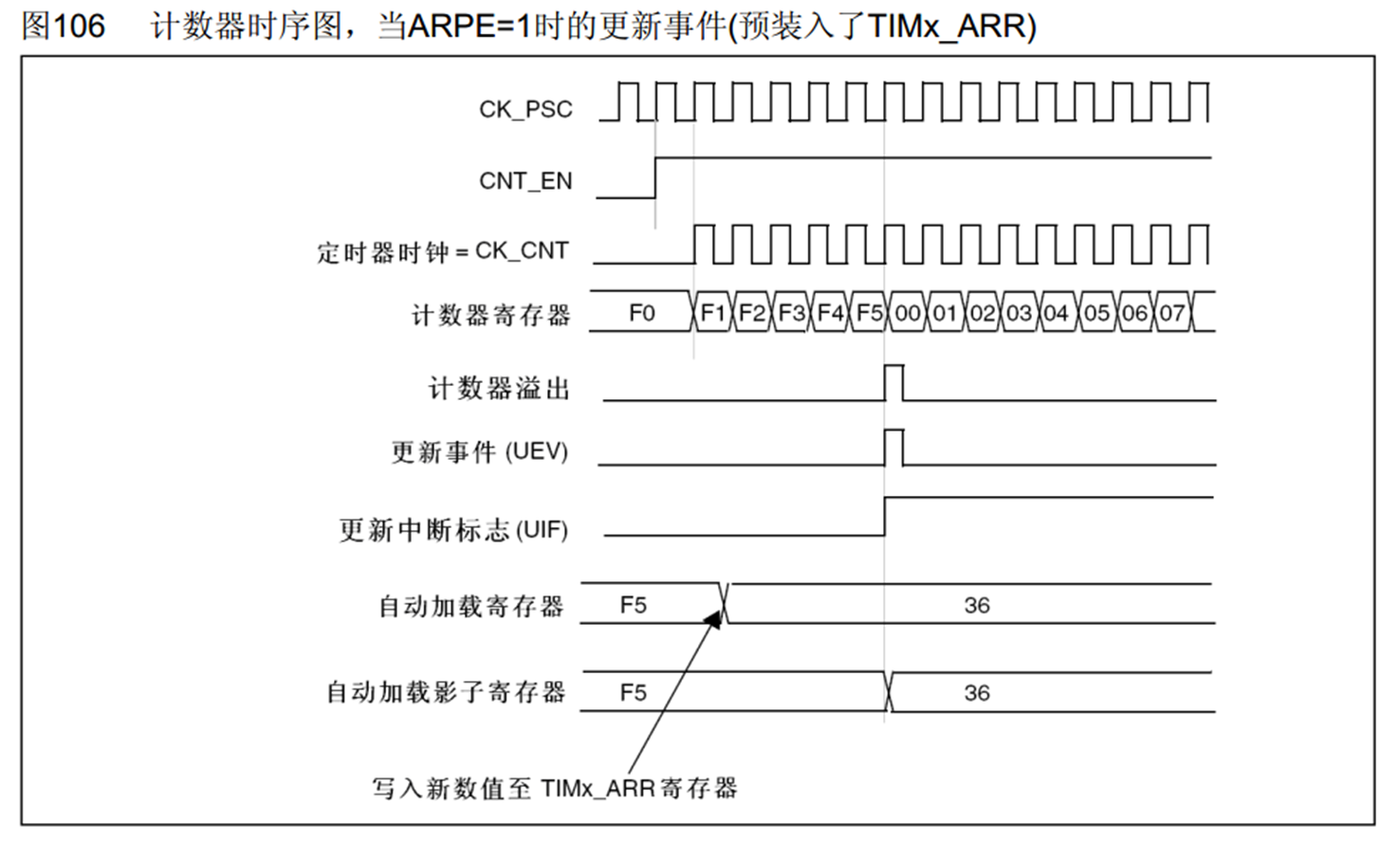

गणनायाः मध्ये गणनालक्ष्यमूल्यं F5 तः 36 यावत् परिवर्तयन्तु । अधः छायापञ्जिका अस्ति register, and in the next count इदं परिवर्तनं केवलं तदा मान्यं भवति यदा चक्रं 36 भवति, अतः छायापञ्जिकायाः परिचयस्य उद्देश्यं वस्तुतः समन्वयनार्थं भवति, अर्थात् परिवर्तनजन्यदोषाणां निवारणाय मूल्यपरिवर्तनानि अद्यतनघटनानि च समन्वयेन भवितुं अनुमतिं दातुं संचालनस्य समये।

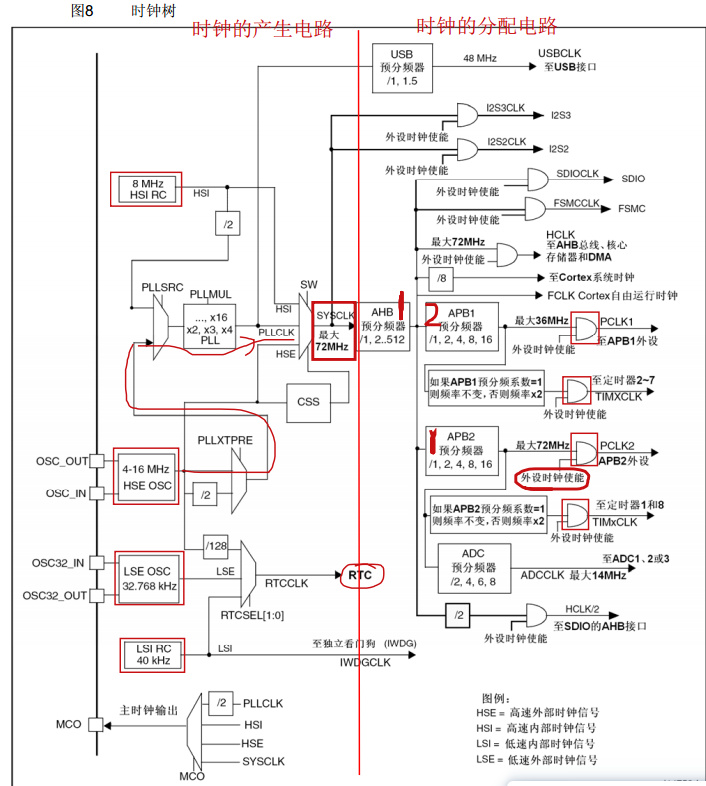

घड़ी स्रोतः

घण्टाजननपरिपथे चत्वारः दोलनस्रोताः सन्ति : १.

(1) HSI: आन्तरिक 8MHz उच्च गति आरसी दोलक;

(2) HSE: बाह्य 4 ~ 16MHz उच्च-गति क्वार्ट्ज स्फटिक दोलक, स्फटिक दोलक इति अपि ज्ञायते, सामान्यतया 8MHz सह सम्बद्धः भवति;

(3) LSE: बाह्यः 32.768KHz न्यूनगतिः स्फटिकदोलकः, यः सामान्यतया RTC कृते घण्टां प्रदाति;

(4) LSI: अन्ते आन्तरिकः 40KHz न्यूनगतिः RC दोलकः अस्ति, यः निगरानीयकुक्कुरस्य कृते घण्टां प्रदातुं शक्नोति ।

उपर्युक्तौ उच्चगतिस्फटिकदोलकौ प्रणालीघटिकां प्रदातुं उपयुज्यते AHB, APB2, APB1 इत्येतयोः घण्टाः सर्वे एतयोः उच्चगतिस्फटिकदोलकयोः व्युत्पन्नाः सन्ति internal RC oscillator, so it is generally बाह्यस्फटिकदोलकस्य उपयोगं कुर्वन्तु।

ST विन्यासघटिका

SystemInit कार्ये ST घण्टां विन्यस्यति: प्रथमं आन्तरिकघटिकां HSI आरभते, आन्तरिकं 8MHz प्रणालीघटिकारूपेण चयनं करोति, अस्थायीरूपेण च आन्तरिकं 8MHzघटिका सह चालयति ततः बाह्यघटिकाम् आरभत, आवृत्तिगुणनार्थं PLL चरण-लॉक्ड् लूप् प्रविष्टुं बाह्यघटिकां विन्यस्यताम्, 8MHz 9 गुणा भवति, ततः भवन्तः 72MHz प्राप्नुवन्ति चरण-लॉक्ड् लूप् आउटपुट् स्थिरं भवति ततः परं फेज-लॉक्ड् लूप् चिनोतु आउटपुट् सिस्टम् क्लॉक् इत्यस्य रूपेण, येन सिस्टम् क्लॉक् 8MHz तः 72MHz यावत् स्विच् अभवत् ।

CSS घड़ी सुरक्षा प्रणाली

CSS (घटिका सुरक्षा प्रणाली): घण्टासुरक्षाप्रणाली अपि घण्टानां परिवर्तनस्य उत्तरदायी भवति of the system clock and prevent program stuck दुर्घटनाजन्य मृत्युः।

घड़ी वितरण परिपथ

*2, ततः दक्षिणभागे, टाइमर् २-७ कृते पृथक् उद्घाट्यते, यतः अत्र प्रीस्केलर गुणांकः २ अस्ति, अतः अत्र आवृत्तिः भवितुम् आवश्यकी अस्ति*2 , अतः टाइमर् 2~7 प्रति गच्छन्ती घण्टा 72MHz भवति । अतः उन्नतसमयनिर्धारकः, सामान्यसमयनिर्धारकः वा मूलभूतसमयनिर्धारकः वा, तेषां आन्तरिकसन्दर्भघटिका ७२MHz भवति ।*2 . यतः आवृत्तिविभागगुणकः १ भवति, तस्मात् समयनिर्धारकाणां १, ८ च घण्टाः ७२MHz भवन्ति ।// 恢复缺省配置

void TIM_DeInit(TIM_TypeDef* TIMx);

// 时基单元初始化

void TIM_TimeBaseInit(TIM_TypeDef* TIMx, TIM_TimeBaseInitTypeDef* TIM_TimeBaseInitStruct);

// 结构体变量赋一个默认值

void TIM_TimeBaseStructInit(TIM_TimeBaseInitTypeDef* TIM_TimeBaseInitStruct);

// 使能计数器---运行控制

void TIM_Cmd(TIM_TypeDef* TIMx, FunctionalState NewState);

// 使能中断输出---中断输出控制

void TIM_ITConfig(TIM_TypeDef* TIMx, uint16_t TIM_IT, FunctionalState NewState);

/*-----------------时基单元的时钟选择---------*/

// 选择内部时钟

void TIM_InternalClockConfig(TIM_TypeDef* TIMx);

// 选择ITRx其他定时器的时钟

void TIM_ITRxExternalClockConfig(TIM_TypeDef* TIMx, uint16_t TIM_InputTriggerSource);

// 选择TIx捕获通道的时钟

void TIM_TIxExternalClockConfig(TIM_TypeDef* TIMx, uint16_t TIM_TIxExternalCLKSource,

uint16_t TIM_ICPolarity, uint16_t ICFilter);

// 选择ETR通过外部时钟模式1输入的时钟

void TIM_ETRClockMode1Config(TIM_TypeDef* TIMx, uint16_t TIM_ExtTRGPrescaler, uint16_t TIM_ExtTRGPolarity,

uint16_t ExtTRGFilter);

// 选择ETR通过外部时钟模式2输入的时钟

void TIM_ETRClockMode2Config(TIM_TypeDef* TIMx, uint16_t TIM_ExtTRGPrescaler,

uint16_t TIM_ExtTRGPolarity, uint16_t ExtTRGFilter);

/*--------------------------------------------------------*/

// 不是用来选择时钟的,单独用来配置ETR引脚的预分频器、极性、滤波参数的

void TIM_ETRConfig(TIM_TypeDef* TIMx, uint16_t TIM_ExtTRGPrescaler, uint16_t TIM_ExtTRGPolarity,

uint16_t ExtTRGFilter);

// 用来单独写预分频值的

void TIM_PrescalerConfig(TIM_TypeDef* TIMx, uint16_t Prescaler, uint16_t TIM_PSCReloadMode);

// 用来改变计数器的计数模式

void TIM_CounterModeConfig(TIM_TypeDef* TIMx, uint16_t TIM_CounterMode);

// 自动重装器预装功能配置

void TIM_ARRPreloadConfig(TIM_TypeDef* TIMx, FunctionalState NewState);

// 给计数器写入一个值

void TIM_SetCounter(TIM_TypeDef* TIMx, uint16_t Counter);

// 给自动重装器写入一个值

void TIM_SetAutoreload(TIM_TypeDef* TIMx, uint16_t Autoreload);

// 获取当前计数器的值

uint16_t TIM_GetCounter(TIM_TypeDef* TIMx);

// 获取当前的预分频器的值

uint16_t TIM_GetPrescaler(TIM_TypeDef* TIMx);

/*-------------获取标志位和清除标志位的------------*/

FlagStatus TIM_GetFlagStatus(TIM_TypeDef* TIMx, uint16_t TIM_FLAG);

void TIM_ClearFlag(TIM_TypeDef* TIMx, uint16_t TIM_FLAG);

ITStatus TIM_GetITStatus(TIM_TypeDef* TIMx, uint16_t TIM_IT);

void TIM_ClearITPendingBit(TIM_TypeDef* TIMx, uint16_t TIM_IT);