私の連絡先情報

郵便メール:

2024-07-12

한어Русский языкEnglishFrançaisIndonesianSanskrit日本語DeutschPortuguêsΕλληνικάespañolItalianoSuomalainenLatina

著者: 太った魚の水槽 (イン・ハイウェン)

Oracle ACE Pro: データベース(OracleとMySQL)

PostgreSQL ACE パートナー

データベース業界で10年の経験があり、現在は主にデータベースサービスに従事

OCM 11g/12c/19c、MySQL 8.0 OCP、Exadata、CDP、およびその他の認定を取得しています。

Mo Tianlun MVP、Moli Star of the Year、ITPUB 認定エキスパート、100 人のエキスパート グループのメンバー、OCM 講師、PolarDB オープンソース コミュニティ技術コンサルタント、HaloDB 外部技術コンサルタント、OceanBase 観察グループ メンバー、青少年協会 MOP テクノロジー コミュニティ (青少年データベース)学習互助会)技術顧問

サークル内では「ディレクター」「セキュリティ」「国内データベースの最大の敵」などの肩書きを持ち、有名な社会的テロリスト(社会的テロリスト)ではない

公開アカウント: 太った魚の水槽、CSDN: 太った魚の水槽 (イン ハイウェン)、ITPUB: yhw1809。

許可を得て転載し、出典を明示しない限り、すべて「違法」盗作です

CPU、SSD、ネットワークなどのサーバーに関わるハードウェアについては以前に説明しましたが、上記のコンポーネントを搭載するマザーボードに加えて、一般的なデスクトップレベル(一般的な家庭用PC)と比較して非常に重要なコンポーネントもあります。 ) メモリ、サーバー メモリには独自のエラー訂正機能があり、ECC (エラー チェックおよび訂正) メモリとも呼ばれます。

この号では、ECC メモリがどのように機能するかを簡単に説明します。

メモリはコンピュータの重要なコンポーネントであり、CPU 内で計算データを一時的に保存したり、ハードディスクなどの外部メモリとデータをやり取りしたりするために使用されます。外部メモリと CPU の間のブリッジです。コンピュータ内のすべてのプログラムはメモリ内で実行されます。コンピュータが動作を開始すると、オペレーティング システムは計算が必要なデータをメモリから CPU に転送し、計算が完了すると CPU が結果を送信します。

メモリの登場は主に、外部ストレージと CPU の内蔵キャッシュ (つまり、L1、L2、L3) の間の大きな帯域幅と遅延の違いを補うことです。本質的には、メモリは CPU の内蔵キャッシュよりも大きいですが、一般に。中間データ転送デバイスは、低速な外部ストレージからのデータの準備を事前に高速化し、CPU がデータを取得するまでの待ち時間を短縮または排除できます。

現在サーバーで主に使用されているメモリは DDR メモリです。DDR が何であるかについてはここでは詳しく説明しません。主流のメモリ世代は DDR4 と DDR5 です。一般的なメモリに加えて、メモリ インターフェイス (または PCIe インターフェイス) (Intel Optane を例にします) に基づく不揮発性メモリ PMEM もあります。これは、メモリと外部ストレージ間でより大きなデータを提供し、キャッシュ領域の速度。

一般に、サーバーには重要なビジネス システムが搭載されており、電子機器の動作中に多くの電磁干渉が発生し、メモリとデータのやり取り中にビット フリッピング (つまり、0 と 1 の交換) が発生する可能性があります。このように、一般的な PC ソフトウェアやプログラムであれば、エラーが発生したり、クラッシュしたりする可能性があります。ただし、この問題が重要なシステムで発生すると、より深刻な結果を引き起こす可能性があります。 (結局のところ、銀行はあなたの資産が理由もなく増加することを望んでいません。0がいくつかある場合、あなたはあなたの資産が減少することを望んでいません)。

その後、データ内のデータ エラーを積極的に検出して修正する ECC メモリが登場しました。

以下に 2 つの比較的原始的な解決策を示します。

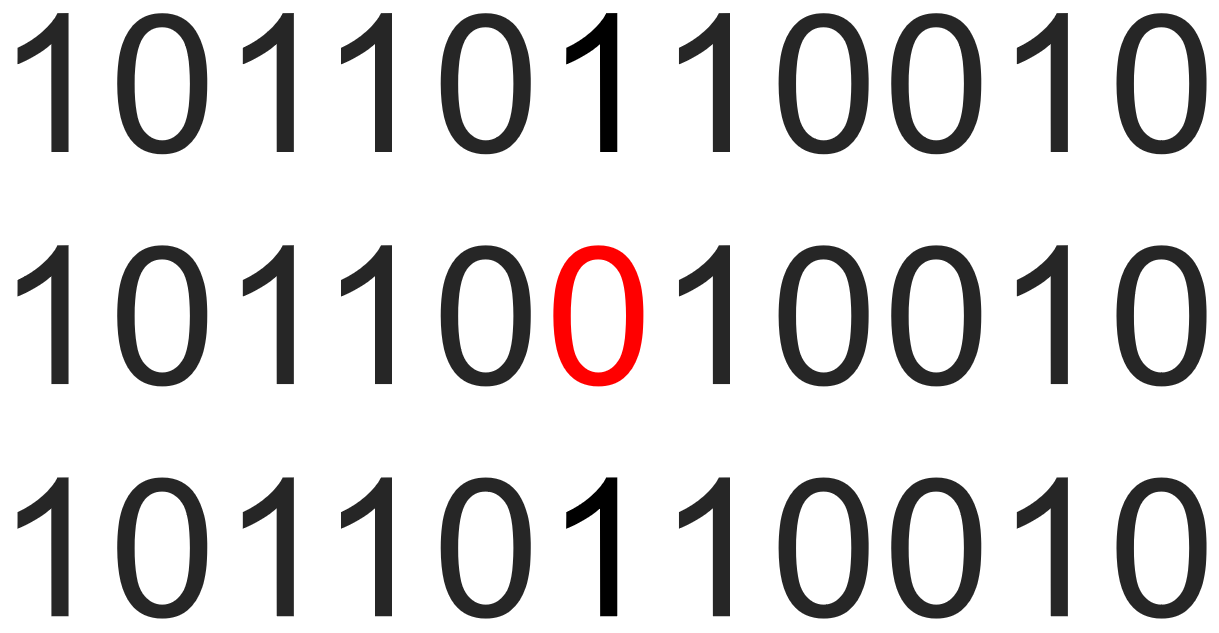

つまり、1 つのデータが 3 つのコピーで送信され、特定のコピーのどこかに問題がある場合、それを修正できます。

しかし、発生確率は非常に低いですが、2 つのデータの同じ位置にビット反転がある場合、データの検証とエラー訂正に問題が発生することもあります。

この方法を使用する場合の最大の問題は、IO 帯域幅の浪費です。

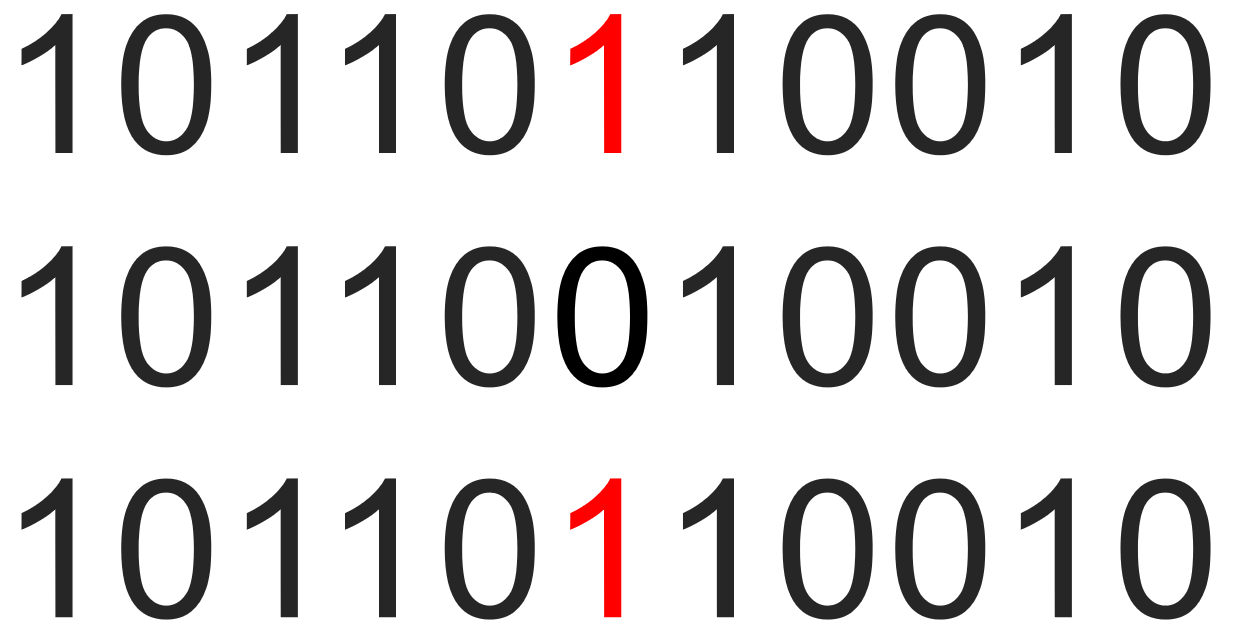

このように、データの先頭に誤り訂正符号が付加されます。つまり、データ内の「1」の数が偶数の場合、誤り訂正符号が付加されます。 0、奇数の場合は誤り訂正符号は1となります。

エラー訂正コードが 1 の数と一致しない場合、データは再送信されます。

また、各検証では理論的にはデータ全体が正常かどうかしか判断できないため、再送信すると遅延が増加します。

同時に 2 つのデータエラーが発生した場合でも、検証の目的は達成できません。

ハミング コードは、現在 ECC メモリで使用されている主な検証およびエラー訂正方法です。

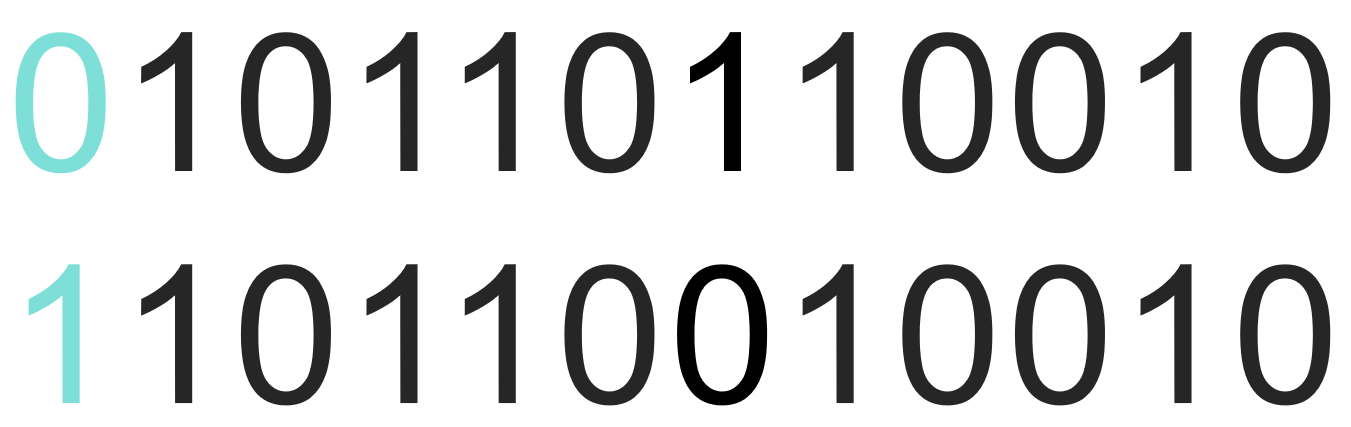

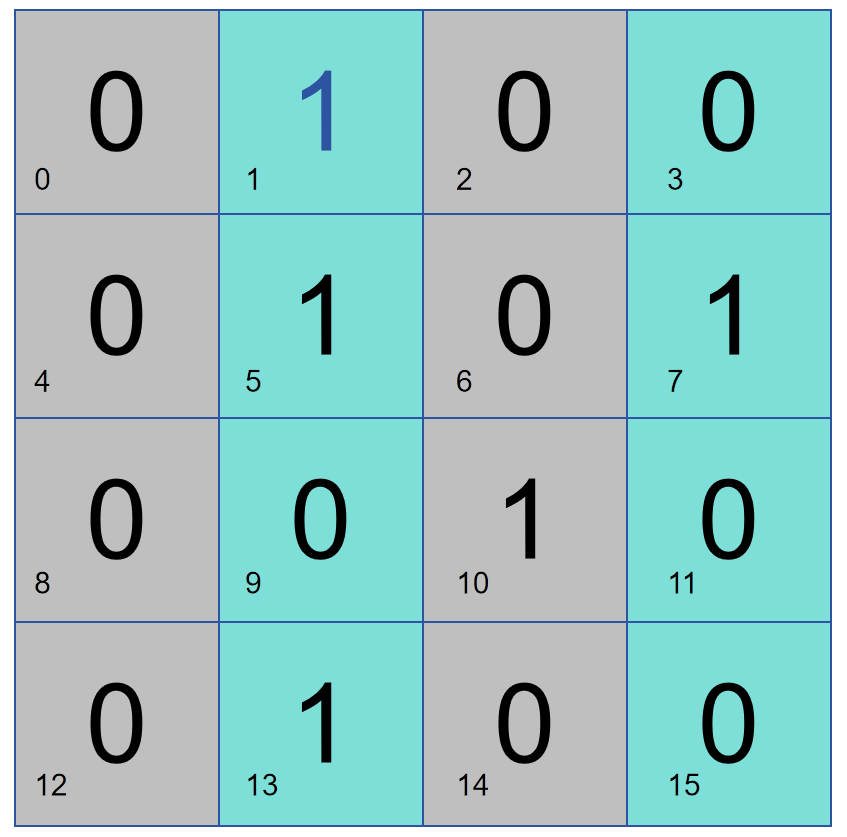

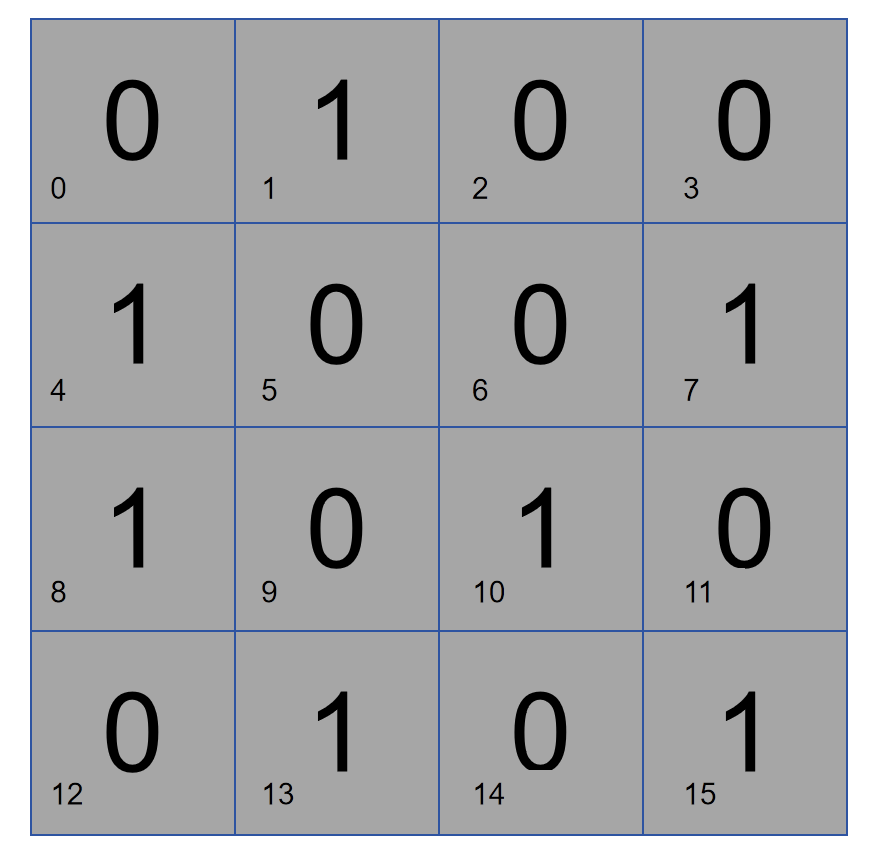

ここでは、次のように 16 ビットのデータを配置していきます。このデータには 2 つの 1 があり、ビット 2 は 0 であると仮定します。データにエラーがあり、パリティ チェックで右半分に問題がないと判断された場合は左半分に問題があり、そうでない場合は右半分に問題があります。

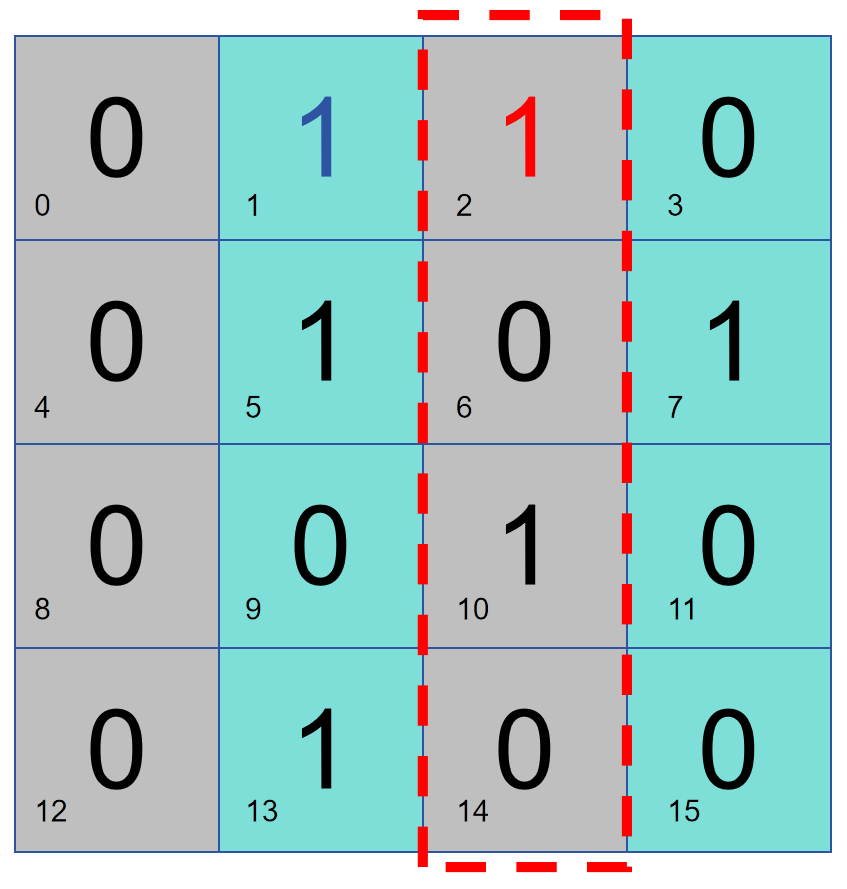

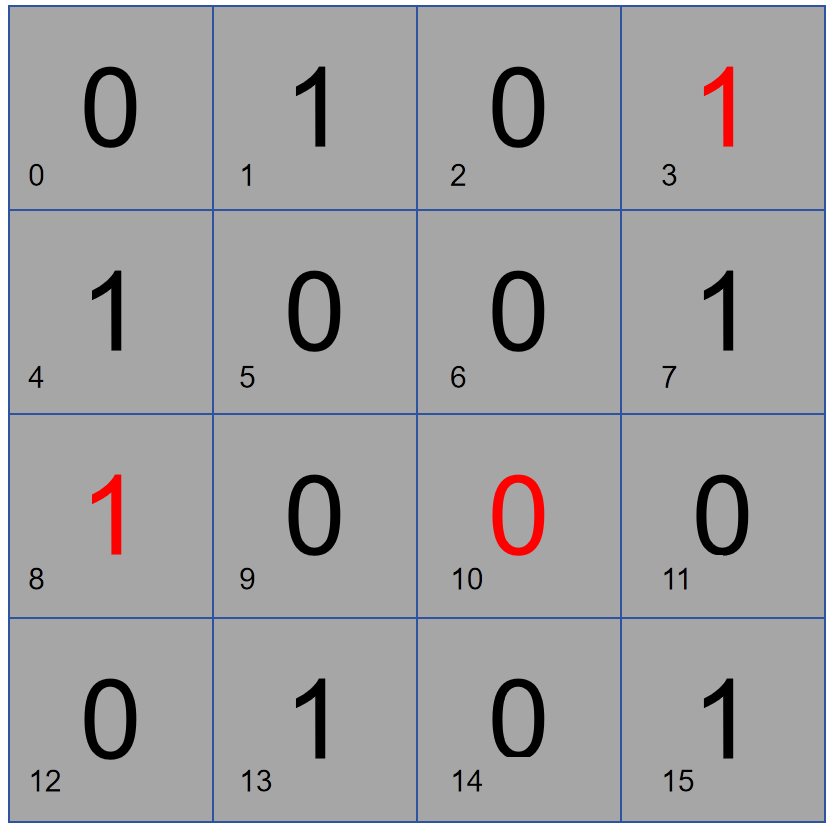

次の図に示すように、ビット 1 は列 2 と 4 でパリティ チェックを実行し、その後ビット 1 に 1 が格納されます。カラム 2 と 4 のパリティ チェックに問題がある場合は、カラム 2 と 4 に問題があり、そうでない場合はカラム 1 と 3 に問題があります。

上記 2 つの方法を組み合わせると、データのどの列に問題があるかを簡単に確認できます。

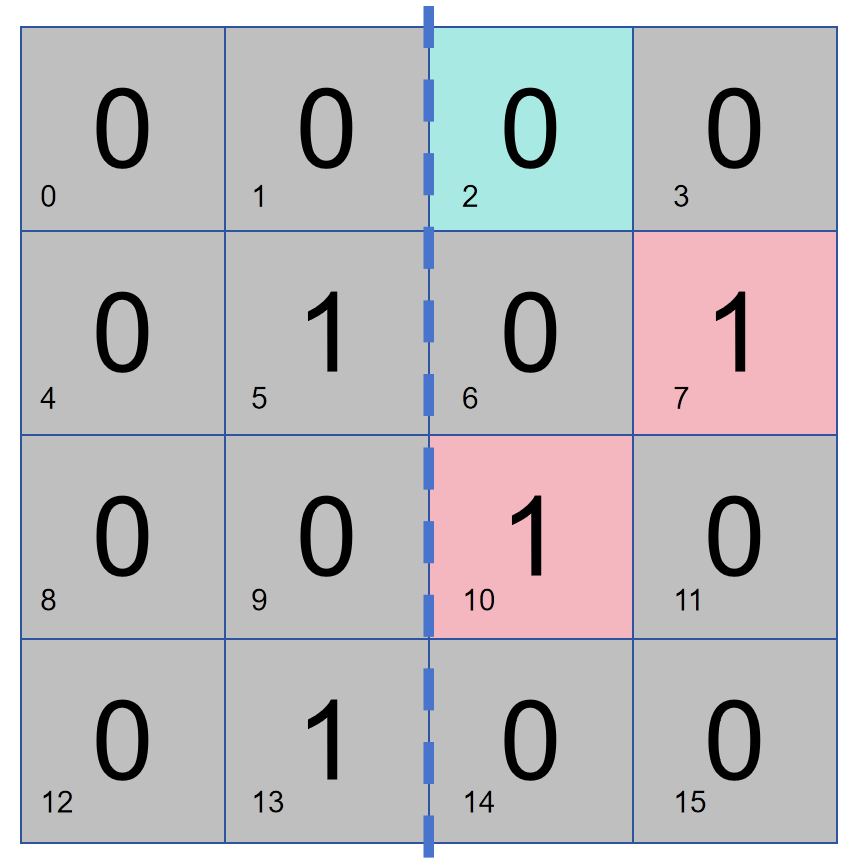

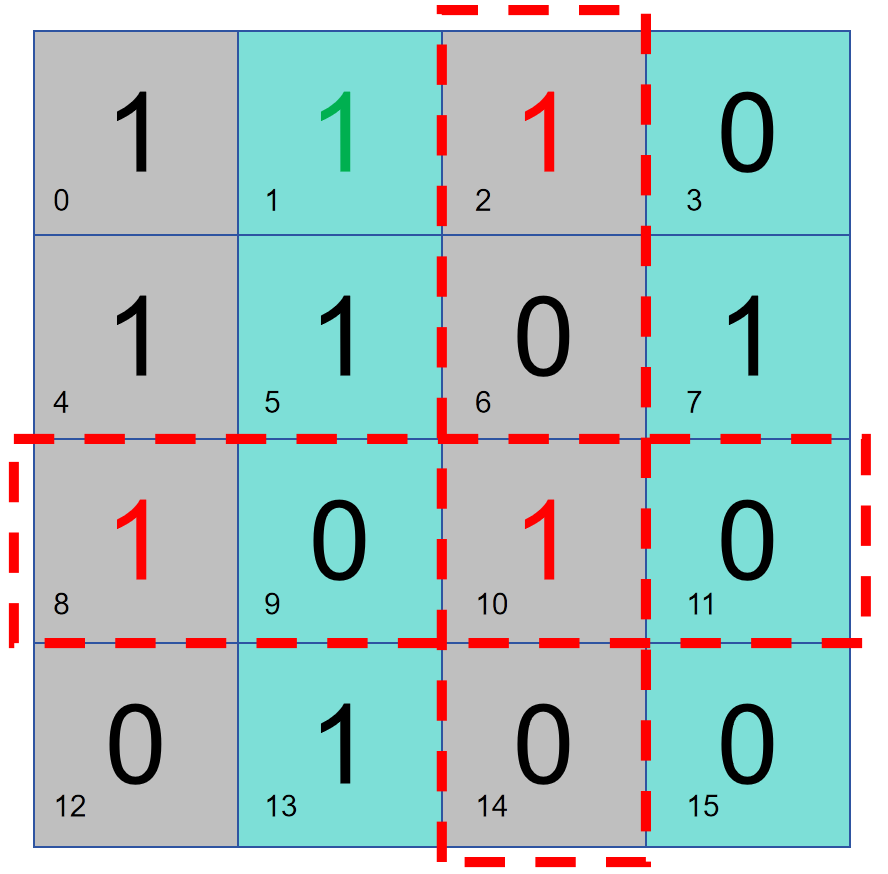

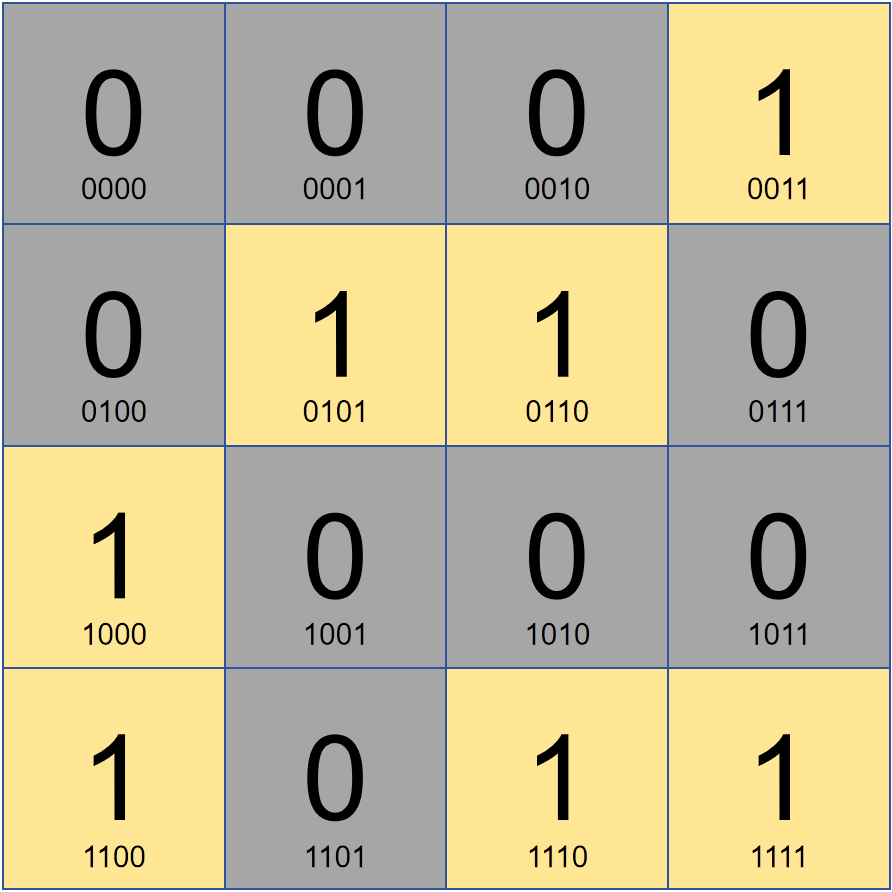

次に、同様の方法を使用して、ビット 4 を使用して行 2 と 4 をチェックし、ビット 8 を使用して下位半分をチェックします。行分離とパーティション パリティ チェックを通じて、エラーの特定の位置を見つけてエラー訂正 (反転) を実行できます。それでおしまい。

ただし、上記の判定はデフォルトのデータに問題があることが前提であり、上記の方法で判定した場合、データビット番号0は誤っているかどうかは関係ありません。上記パリティチェック結果。したがって、ビット 0 を使用して、3.2 の方法を使用してデータのブロック全体を検証します。

この場合、エラーが 2 つある場合、ディスク全体のパリティ チェックとパーティション パリティ チェックの結果が矛盾します。エラーの場所を特定することはできませんが、データ ブロック全体が異常であると判断できます。データを再送信するだけです。

しかし、データエラーが3つあると判断できなくなります。

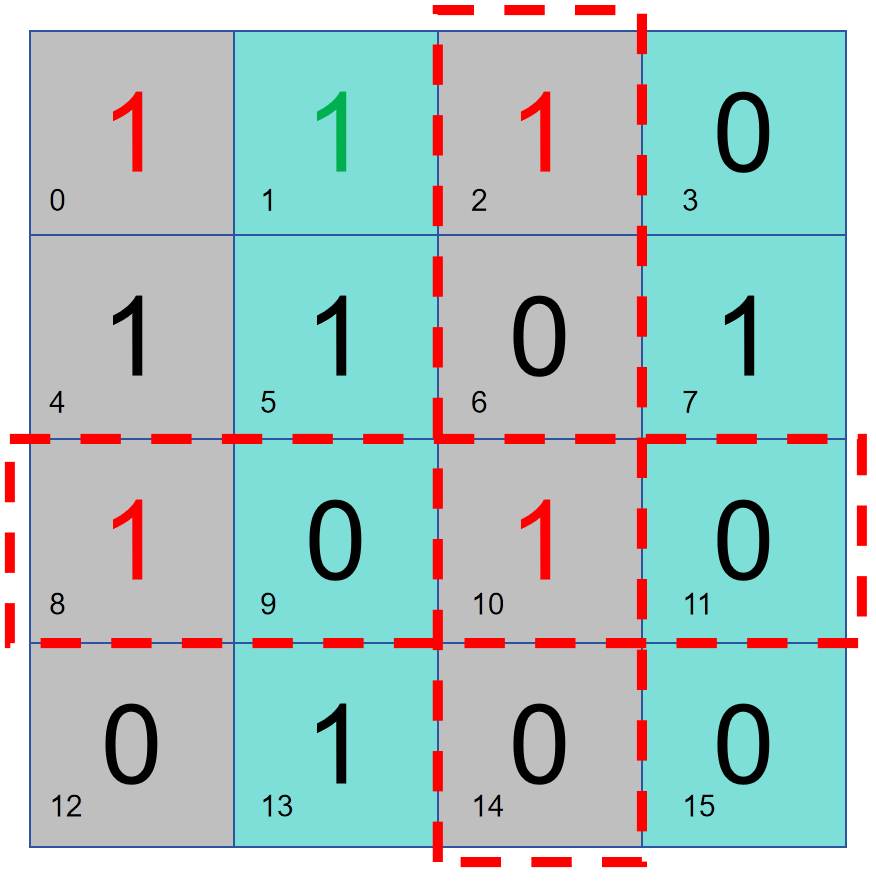

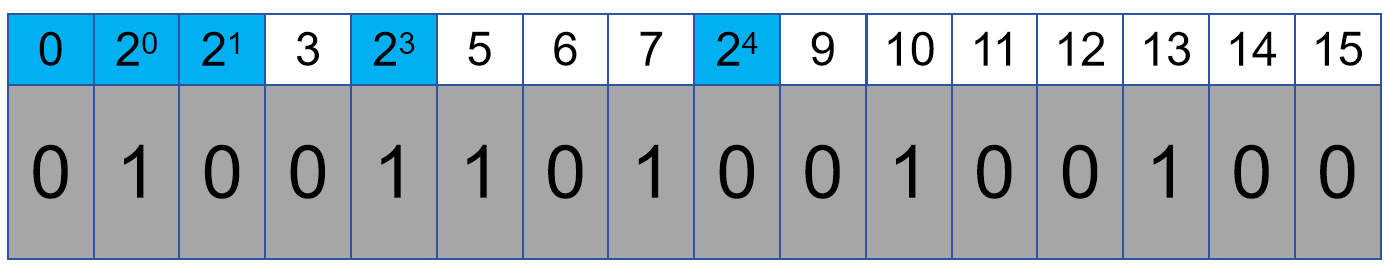

別の方法では、チェック コードの位置がすべて 2 の N 乗であることがわかります。

チェック コードは 2 の N 乗に配置するだけで済みます。ブロックが大きくなるほど、エラー訂正コードが占める内容は少なくなりますが、複数のビット 反転が発生する可能性が高くなります。一般的な ECC 伝送ブロック サイズは 72 ビットで、64 ビットがデータ、8 ビットがエラー訂正コードです。したがって、一般に、8G の容量のメモリには 1G のメモリ パーティクルが 8 つ必要ですが、8G の容量の ECC メモリには 1G のメモリ パーティクルが 9 つ必要です。余分な 1G は、追加のエラー訂正コード容量を格納するために使用されます。

ただし、コンピューターのエラー修正では、通常の「ばかばかしい」方法ではエラー位置を計算しません。ここでは、バイナリの魅力を利用して、位置をバイナリで表現します。

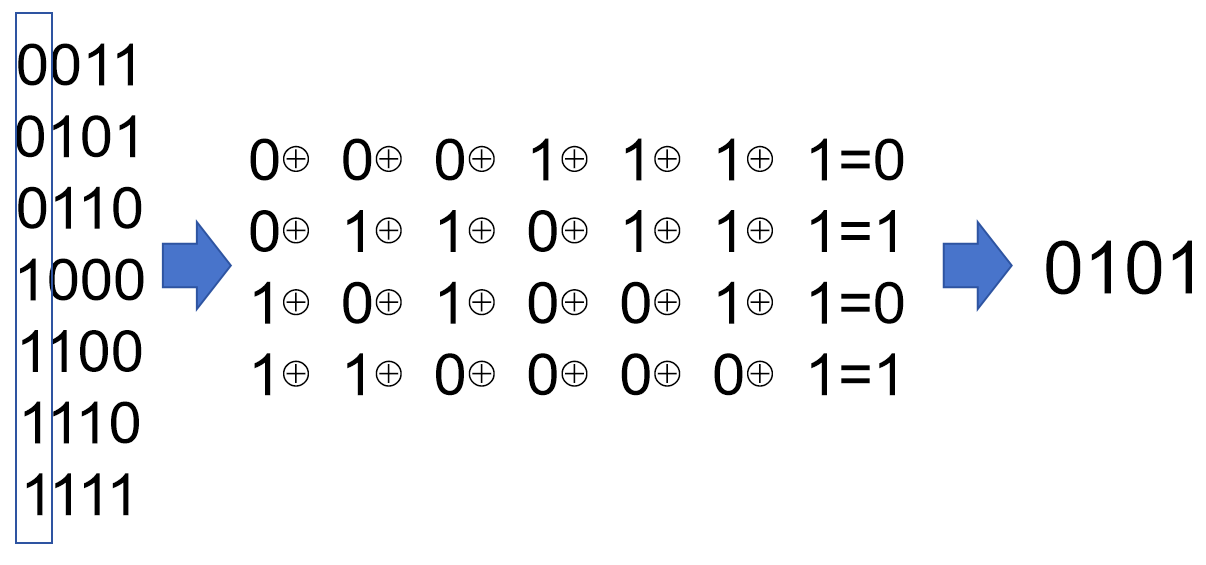

1 であるすべての位置を取り出し、垂直方向のバイナリ OR 演算を実行して、問題のある位置を直接取得します。

添付: 低密度パリティ チェック コードである、LDPC (Low Density Parity-Check Code) もあります。この方法では、マルチビット フリッピングの問題を特定できるため、ここでは具体的な実装原理については説明しません。 SSDの検証に使用されます。メモリの高速性と実装コストのため、ECC の実装には今でもハミング コードが使用されています。

この号では、ECC メモリがエラー訂正を実装する方法を簡単に紹介します。

何が書かれているかを知るのが古いルールです。