2024-07-08

한어Русский языкEnglishFrançaisIndonesianSanskrit日本語DeutschPortuguêsΕλληνικάespañolItalianoSuomalainenLatina

Um Block Desgin bequem für das Design zu verwenden, können Sie im Vivado-Design den Code, den Sie geschrieben haben, in einen IP-Kern kapseln. Der gekapselte IP-Kern hat die gleichen Funktionen wie der Originalcode. In diesem Artikel wird die Implementierung der 24-Bit-DA-Konvertierung (einschließlich Parallel-Seriell-Konvertierung, der verwendete Digital-Analog-Konverter ist CL4660) als Beispiel verwendet, um die Methode und Aufrufmethode des VIVADO-Paket-IP-Kerns vorzustellen den detaillierten FPGA-Designprozess der DAC-Konvertierung und stellt seinen verifizierten detaillierten Code bereit (unter Verwendung der Verilog-Sprache).

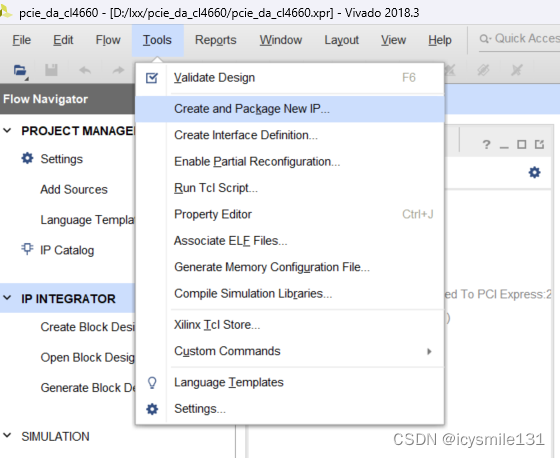

Erstellen Sie ein neues Projekt oder öffnen Sie ein vorhandenes Projekt, klicken Sie auf „Extras – Neue IP erstellen und verpacken …“

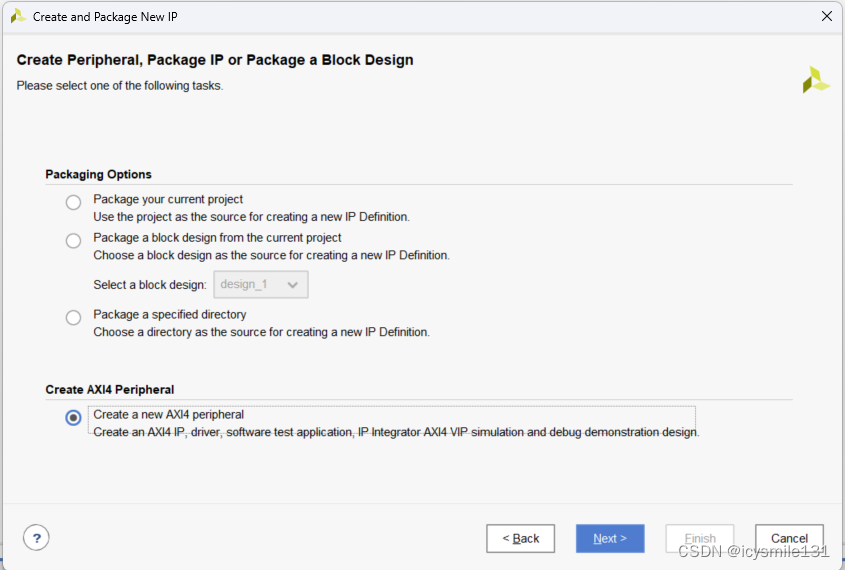

Das folgende Dialogfeld wird angezeigt:

Klicken Sie auf „Weiter“, wählen Sie „Neues AXI4-Peripheriegerät erstellen“ und klicken Sie auf „Weiter“.

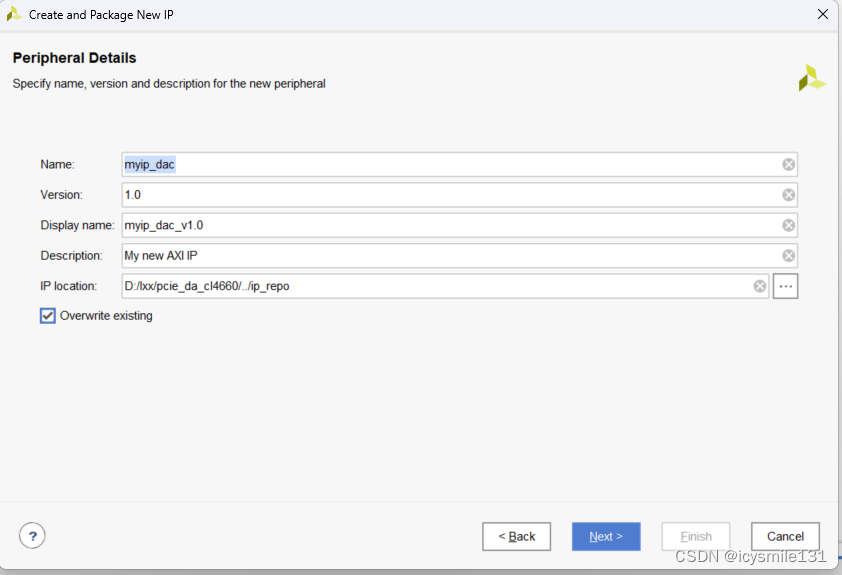

Geben Sie unter Name den Namen des zu generierenden IP-Kerns ein und wählen Sie „Vorhandene überschreiben“. Wenn die IP neu generiert werden muss, wird das ursprüngliche Design automatisch überschrieben.

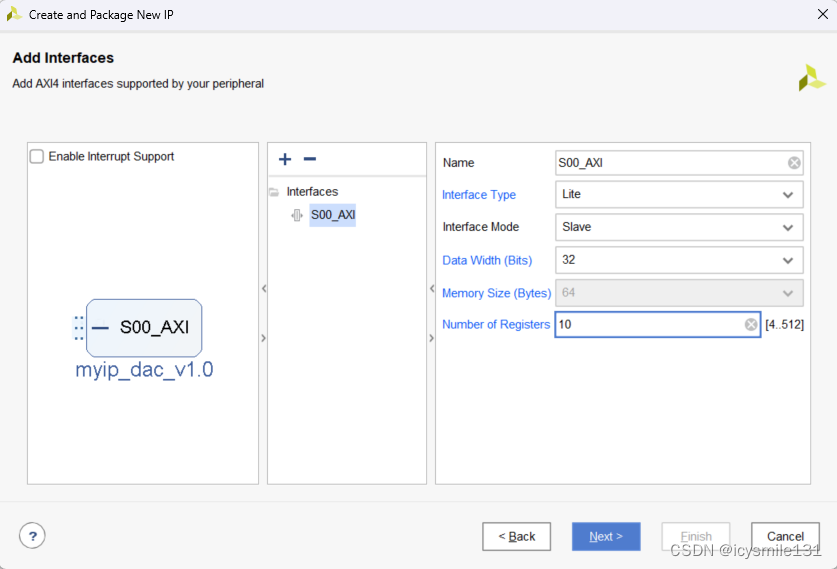

Klicken Sie auf „Weiter“, „Datenbreite (Bits)“ ist die Datenbreite, „Anzahl der Register“ ist die Anzahl der Register. Hier müssen Sie Parameter eingeben, die den Designanforderungen entsprechen. Klicken Sie auf „Weiter“.

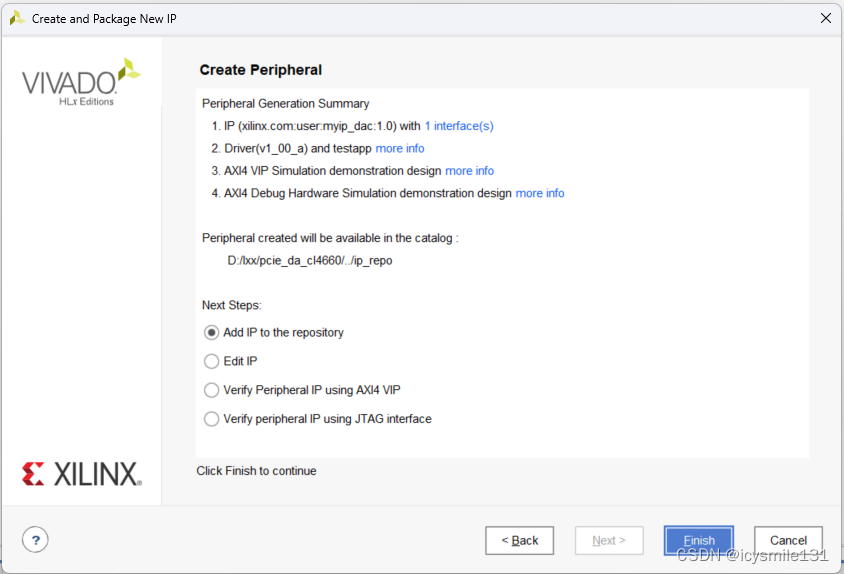

Klicken Sie auf Fertig stellen.

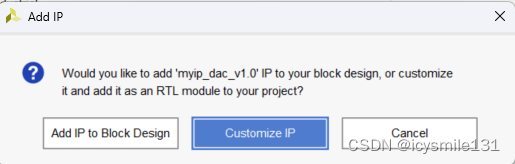

Doppelklicken Sie im PROJEKTMANAGER auf den IP-Katalog und doppelklicken Sie rechts im IP-Katalog auf den neu generierten IP-Kern myip_dac_v1.0.

Klicken Sie im neuen Popup-Menü auf „IP zum Blockdesign hinzufügen“.

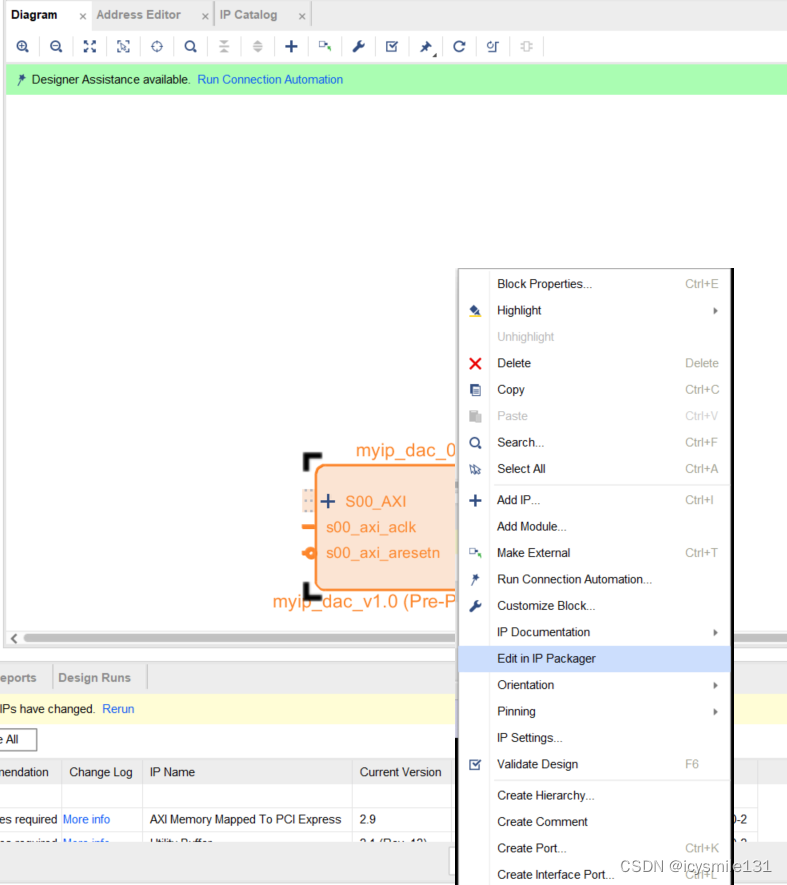

Wählen Sie den IP-Core myip_dac_v1.0 aus, klicken Sie mit der rechten Maustaste und wählen Sie im Popup-Menü „Im IP-Packager bearbeiten“.

Wählen Sie im Popup-Menü OK aus, um mit der Bearbeitung des neu generierten benutzerdefinierten IP-Cores zu beginnen.