informasi kontak saya

Surat[email protected]

2024-07-08

한어Русский языкEnglishFrançaisIndonesianSanskrit日本語DeutschPortuguêsΕλληνικάespañolItalianoSuomalainenLatina

Dalam desain vivado, agar mudah menggunakan Block Desgin untuk desain, Anda dapat menggunakan perangkat lunak vivado untuk merangkum kode yang Anda tulis ke dalam inti IP. Inti IP yang dienkapsulasi memiliki fungsi yang sama dengan kode aslinya. Artikel ini mengambil implementasi konversi DA 24-bit (termasuk konversi paralel-ke-serial, konverter digital-ke-analog yang digunakan adalah CL4660) sebagai contoh untuk memperkenalkan metode dan metode pemanggilan inti IP pengemasan VIVADO, serta proses desain FPGA terperinci dari konversi DAC, dan menyediakan kode Terperinci yang terverifikasi (menggunakan bahasa Verilog).

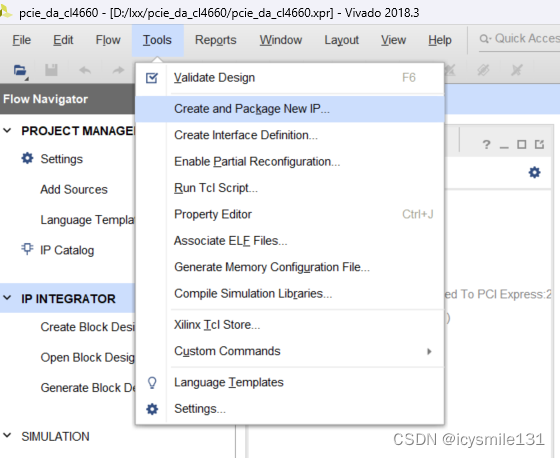

Buat proyek baru, atau buka proyek yang sudah ada, klik Alat - Buat dan Kemas IP Baru...

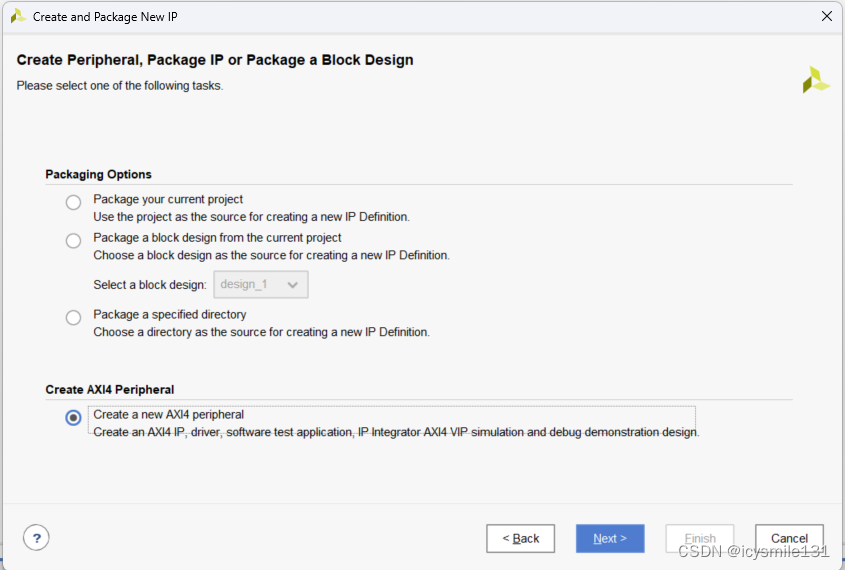

Kotak dialog berikut muncul,

Klik Berikutnya, pilih Buat periferal AXI4 baru, klik Berikutnya,

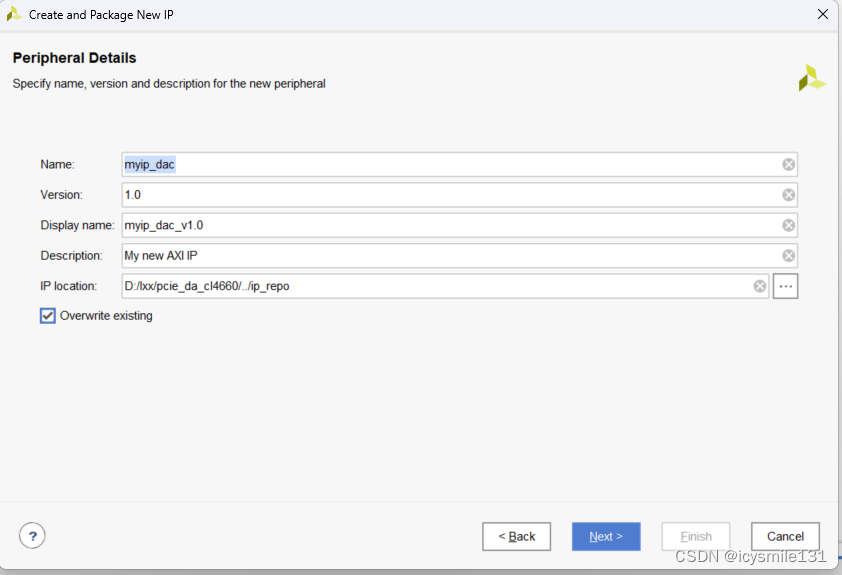

Masukkan nama inti IP yang akan dibuat di Nama dan pilih Timpa yang ada. Ketika IP perlu dibuat ulang, desain asli akan otomatis ditimpa.

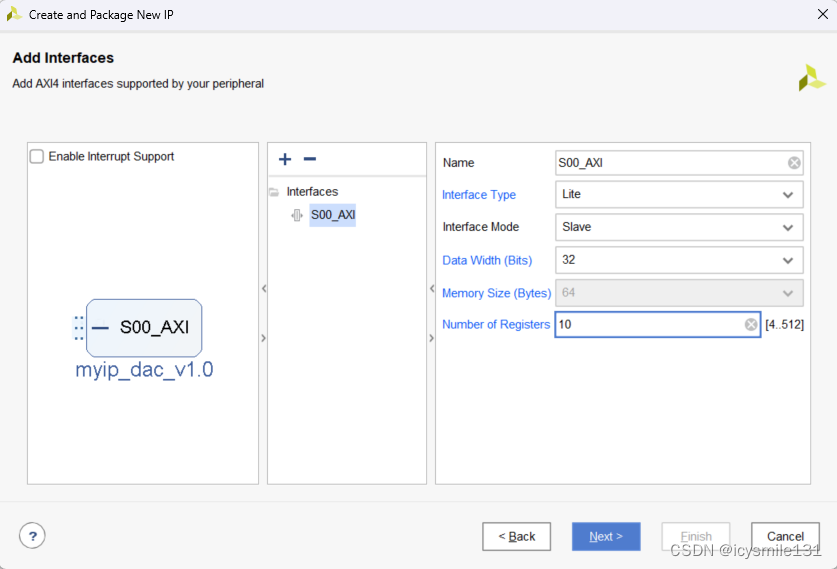

Klik Berikutnya, Lebar Data (Bits) adalah lebar data, Jumlah Register adalah jumlah register, di sini Anda perlu memasukkan parameter yang memenuhi persyaratan desain, klik Berikutnya,

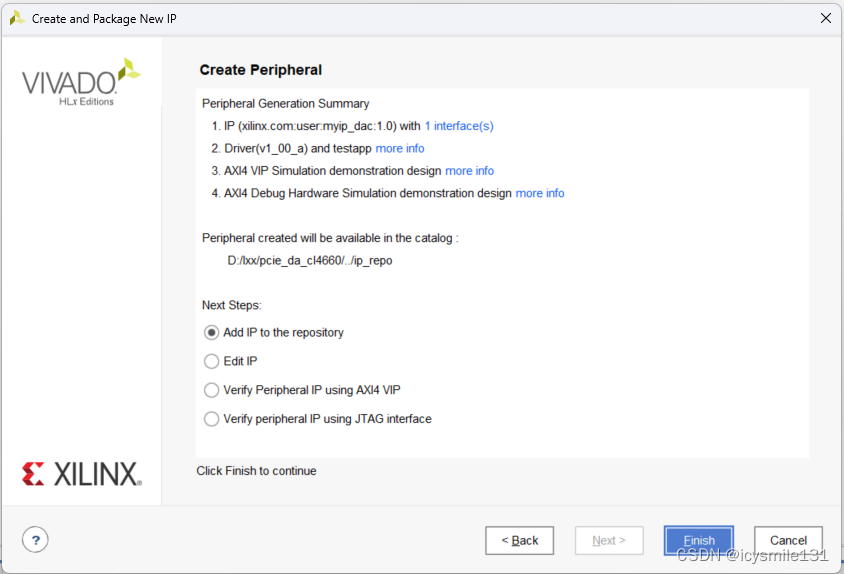

Klik Selesai,

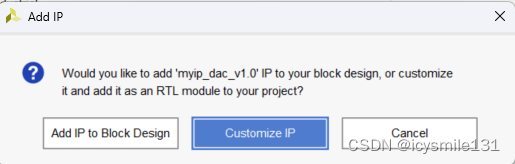

Klik dua kali Katalog IP di MANAJER PROYEK, dan klik dua kali inti IP yang baru dibuat myip_dac_v1.0 di Katalog IP di sebelah kanan.

Klik Tambahkan IP ke Desain Blokir di menu pop-up baru.

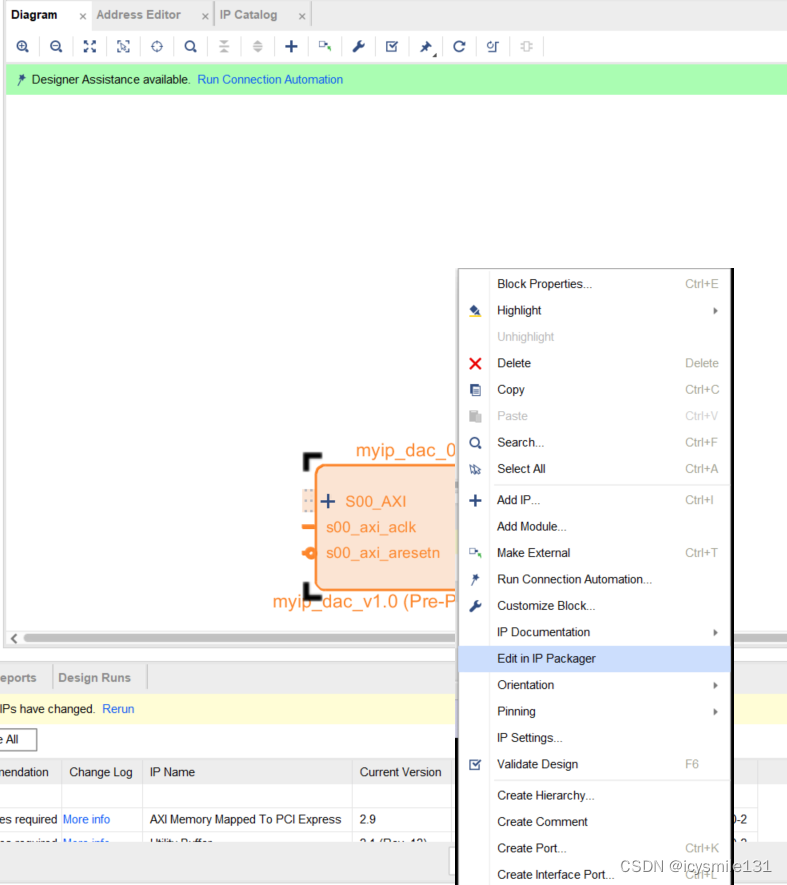

Pilih inti IP myip_dac_v1.0, klik kanan dan pilih Edit dalam paket IP di menu pop-up.

Pilih OK di menu pop-up untuk mulai mengedit inti IP khusus yang baru dibuat.