私の連絡先情報

郵便メール:

2024-07-08

한어Русский языкEnglishFrançaisIndonesianSanskrit日本語DeutschPortuguêsΕλληνικάespañolItalianoSuomalainenLatina

vivado デザインでは、ブロック デザインをデザインに便利に使用するために、vivado ソフトウェアを使用して、作成したコードを IP コアにカプセル化できます。カプセル化された IP コアには、元のコードと同じ機能があります。この記事では、24 ビット DA 変換 (パラレル/シリアル変換を含む、使用したデジタル/アナログ コンバータは CL4660) の実装を例に、VIVADO パッケージ化 IP コアのメソッドと呼び出し方法、およびDAC 変換の詳細な FPGA 設計プロセスを示し、検証済みの詳細コード (Verilog 言語を使用) を提供します。

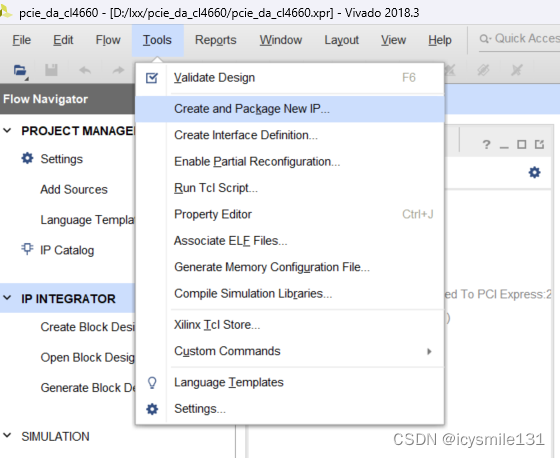

新しいプロジェクトを作成するか、既存のプロジェクトを開いて、[ツール] - [新しい IP の作成とパッケージ化...] をクリックします。

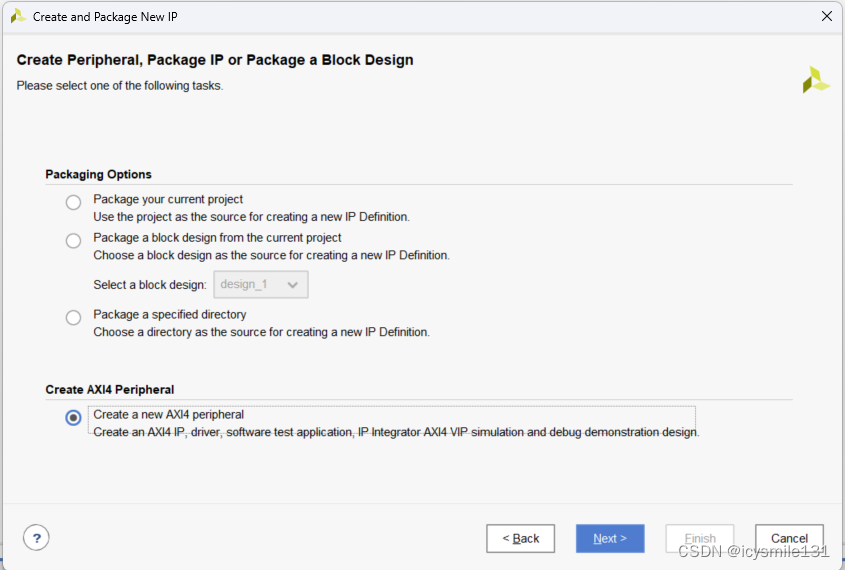

次のダイアログボックスが表示されます。

[次へ] をクリックし、[新しい AXI4 ペリフェラルの作成] を選択して、[次へ] をクリックします。

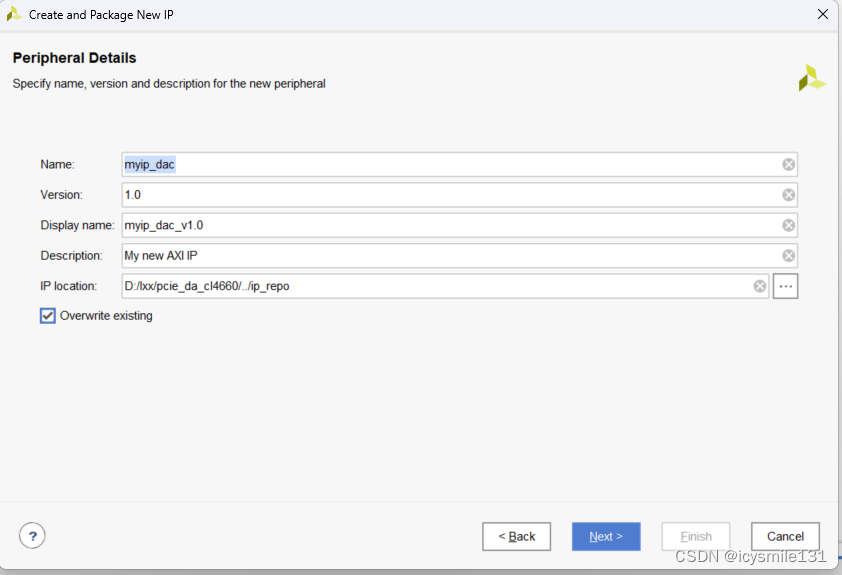

[名前] に生成する IP コアの名前を入力し、[既存の上書き] を選択します。IP を再生成する必要がある場合、元のデザインは自動的に上書きされます。

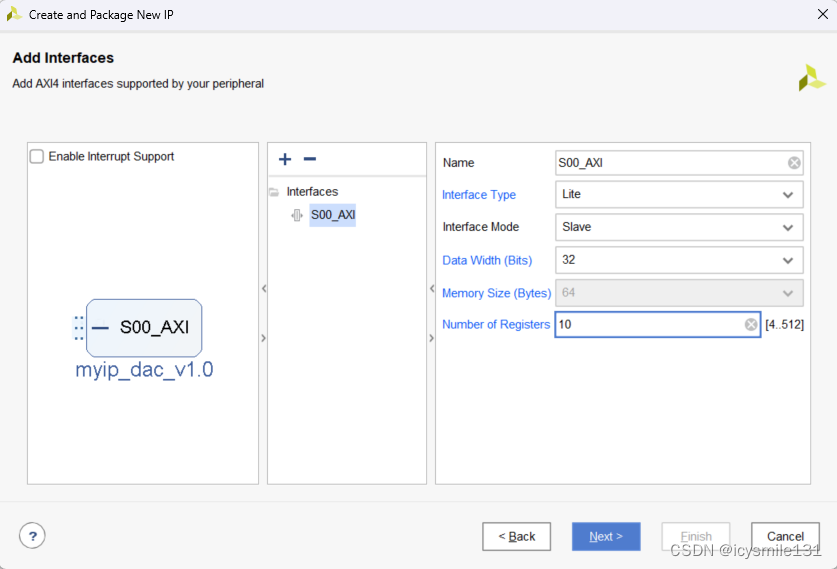

[次へ] をクリックします。[データ幅 (ビット)] はデータ幅、[レジスタ数] はレジスタの数です。ここでは、設計要件を満たすパラメータを入力する必要があります。[次へ] をクリックします。

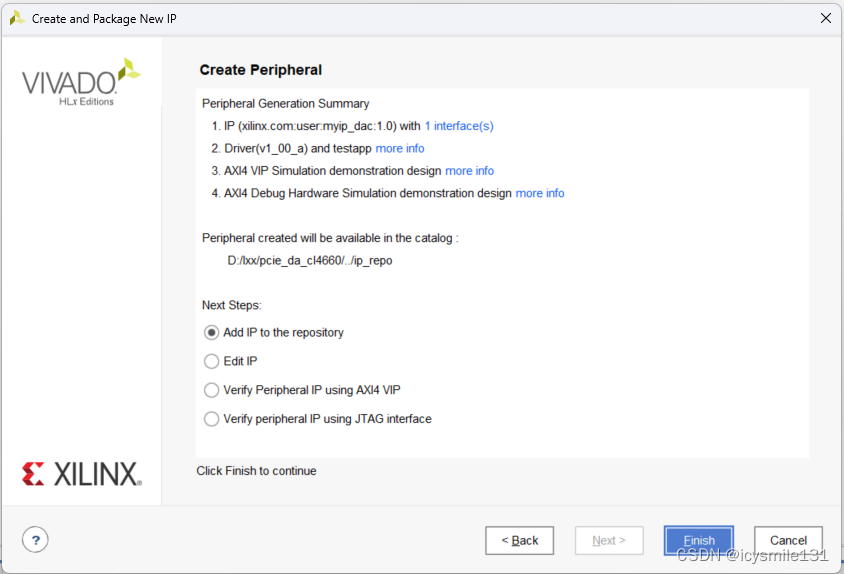

「完了」をクリックします。

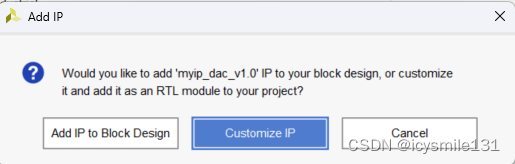

PROJECT MANAGER で IP カタログをダブルクリックし、右側の IP カタログで新しく生成された IP コア myip_dac_v1.0 をダブルクリックします。

新しいポップアップ メニューで [ブロック デザインに IP を追加] をクリックします。

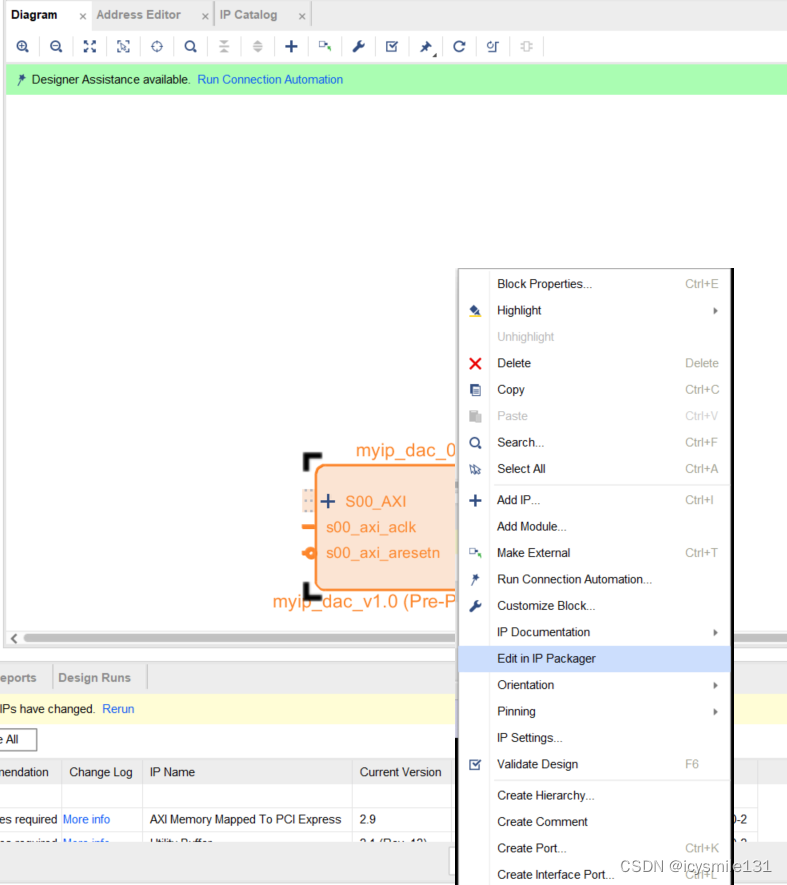

myip_dac_v1.0 IP コアを選択し、右クリックして、ポップアップ メニューの [IP パッケージャーで編集] を選択します。

ポップアップ メニューで [OK] を選択して、新しく生成されたカスタム IP コアの編集を開始します。