2024-07-08

한어Русский языкEnglishFrançaisIndonesianSanskrit日本語DeutschPortuguêsΕλληνικάespañolItalianoSuomalainenLatina

vivado design इत्यस्मिन्, डिजाइनार्थं Block Desgin इत्यस्य सुविधानुसारं उपयोगं कर्तुं, भवान् vivado software इत्यस्य उपयोगं कृत्वा भवता लिखितं कोडं IP core इत्यस्मिन् encapsulated कर्तुं शक्नोति । अयं लेखः 24-बिट् DA रूपान्तरणस्य कार्यान्वयनम् (समानान्तर-क्रमाङ्करूपान्तरणं सहितं, प्रयुक्तः डिजिटल-तः-एनालॉग्-परिवर्तकः CL4660 अस्ति) उदाहरणरूपेण VIVADO पैकेजिंग् IP कोरस्य विधिं, आह्वानविधिं च परिचययितुं उदाहरणरूपेण गृह्णाति, तथा च DAC रूपान्तरणस्य विस्तृतं FPGA डिजाइनप्रक्रिया, तथा च तस्य सत्यापितं विस्तृतसङ्केतं (Verilog भाषायाः उपयोगेन) प्रदाति ।

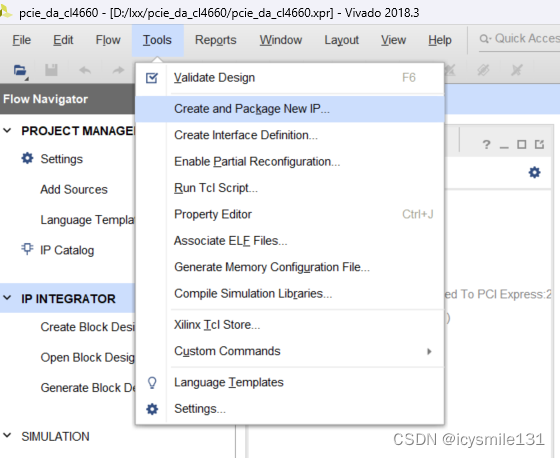

नूतनं परियोजनां रचयन्तु, अथवा विद्यमानं परियोजनां उद्घाटयन्तु, Tools - Create and Package New IP... इत्यत्र क्लिक् कुर्वन्तु...

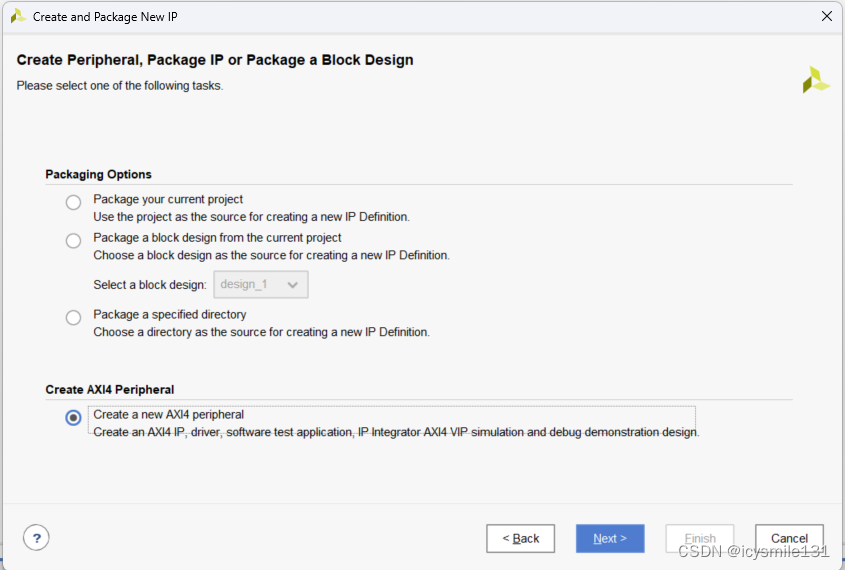

निम्नलिखित संवादपेटिका पॉप अप भवति, .

Next नुदन्तु, नूतनं AXI4 परिधीयम् रचयन्तु इति चिनोतु, Next नुदन्तु,

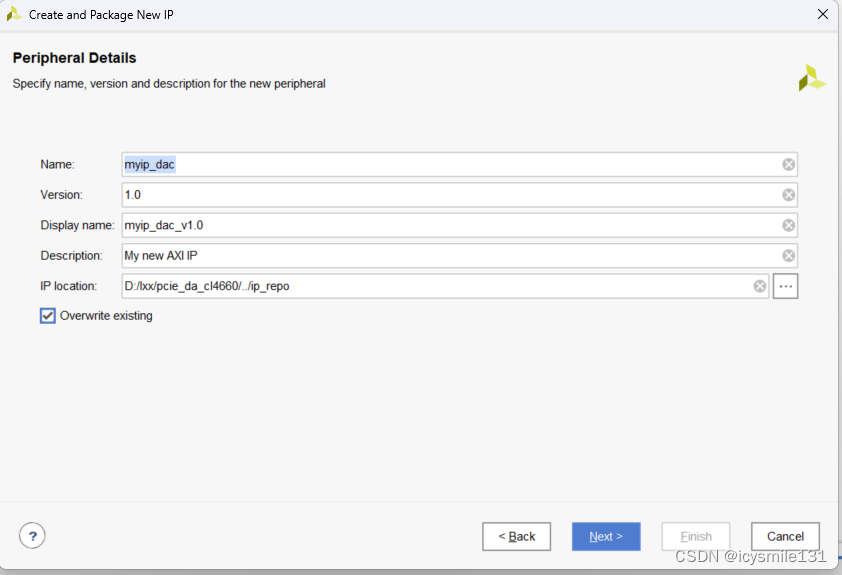

Name इत्यत्र उत्पन्नस्य IP कोरस्य नाम प्रविशन्तु तथा च Overwrite existing इति चिनोतु यदा IP इत्यस्य पुनर्जन्मस्य आवश्यकता भवति तदा मूलडिजाइनः स्वयमेव अधिलिखितः भविष्यति ।

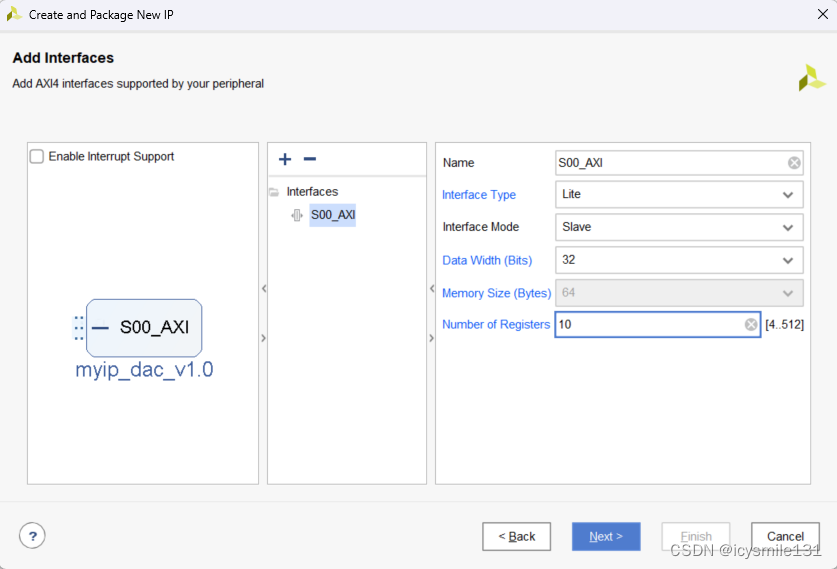

Next इत्यत्र क्लिक् कुर्वन्तु, Data Width (Bits) इति data width, Number of Registers इति रजिस्टर् इत्यस्य संख्या, अत्र भवद्भिः डिजाइनस्य आवश्यकतां पूरयन्तः पैरामीटर्स् प्रविष्टव्याः सन्ति, Next इत्यत्र क्लिक् कुर्वन्तु,

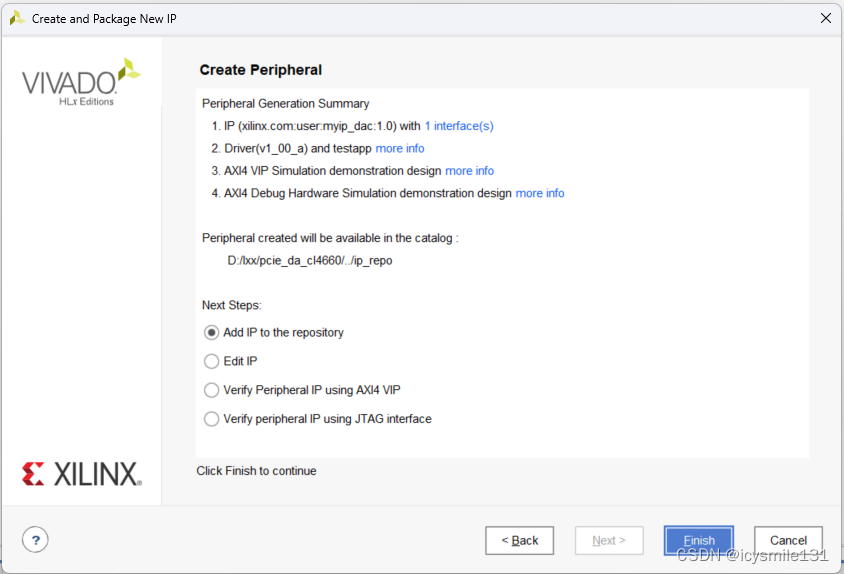

समाप्तं नुदन्तु, .

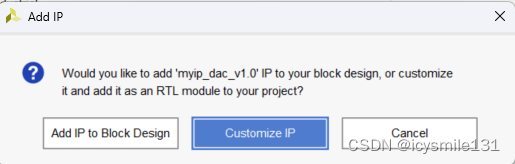

PROJECT MANAGER इत्यस्मिन् IP Catalog इत्यत्र द्विवारं क्लिक् कुर्वन्तु, तथा च दक्षिणभागे IP Catalog इत्यस्मिन् नवजनितं IP core myip_dac_v1.0 इत्यत्र डबल-क्लिक् कुर्वन्तु ।

नूतने पॉप्-अप मेन्यू मध्ये Add IP to Block Design इति नुदन्तु ।

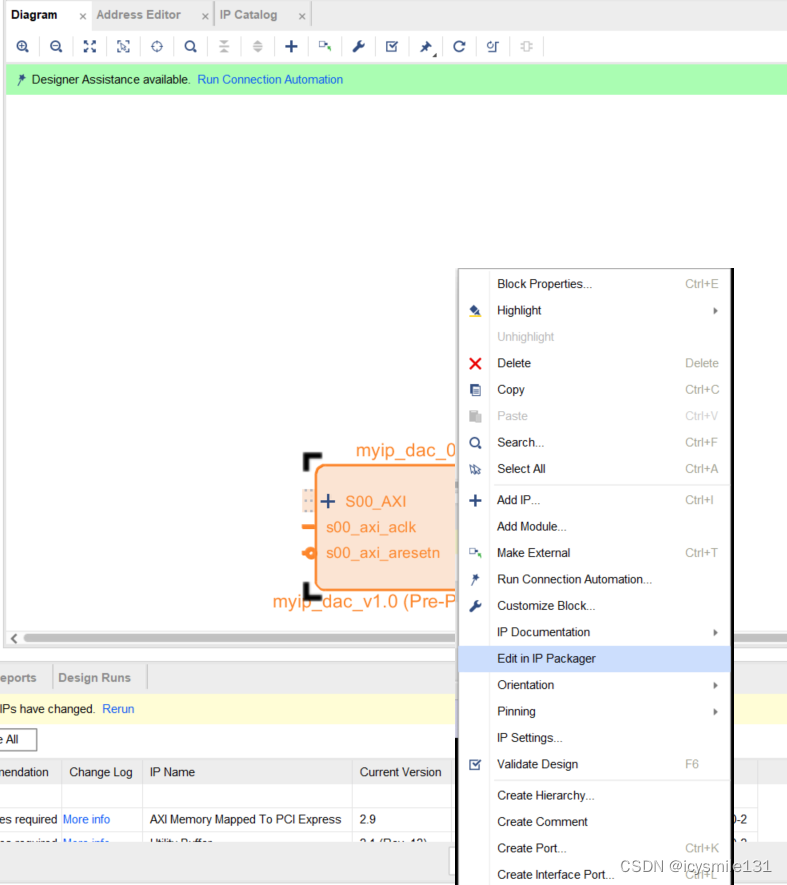

myip_dac_v1.0 IP कोरं चित्वा, राइट्-क्लिक् कृत्वा pop-up मेन्यू मध्ये Edit in IP packager इति चिनोतु ।

नवजनितस्य कस्टम् IP कोरस्य सम्पादनं आरभ्यतुं पॉप्-अप मेन्यू मध्ये OK इति चिनोतु ।