2024-07-08

한어Русский языкEnglishFrançaisIndonesianSanskrit日本語DeutschPortuguêsΕλληνικάespañolItalianoSuomalainenLatina

Dans la conception Vivado, afin d'utiliser facilement Block Desgin pour la conception, vous pouvez utiliser le logiciel Vivado pour encapsuler le code que vous avez écrit dans un noyau IP. Le noyau IP encapsulé a les mêmes fonctions que le code d'origine. Cet article prend comme exemple la mise en œuvre de la conversion DA 24 bits (y compris la conversion parallèle-série, le convertisseur numérique-analogique utilisé est CL4660) pour présenter la méthode et la méthode d'appel du noyau IP de packaging VIVADO, ainsi que le processus détaillé de conception FPGA de conversion DAC et fournit son code détaillé vérifié (en utilisant le langage Verilog).

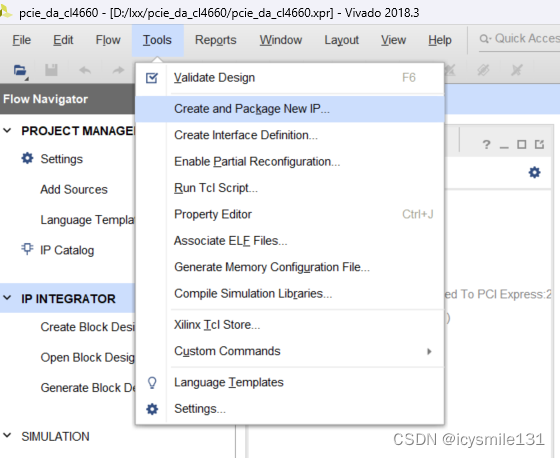

Créez un nouveau projet ou ouvrez un projet existant, cliquez sur Outils - Créer et empaqueter une nouvelle adresse IP...

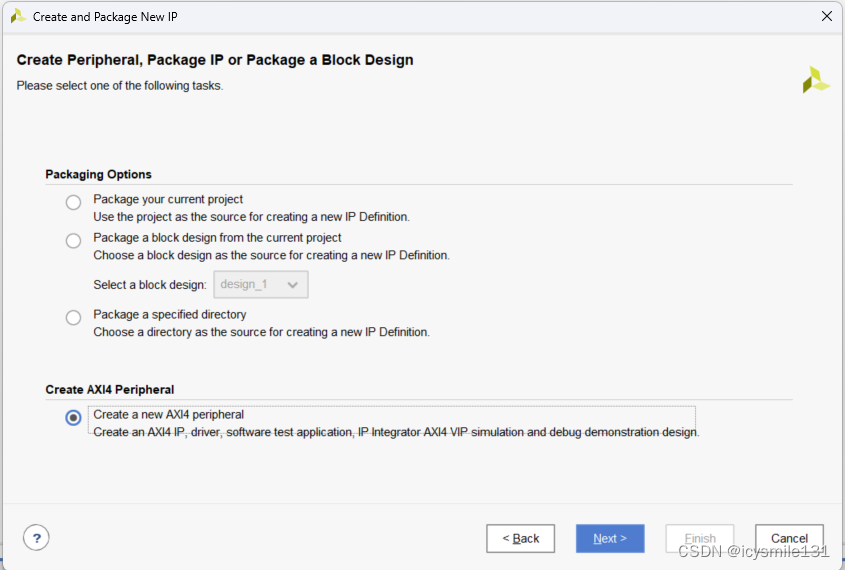

La boîte de dialogue suivante apparaît,

Cliquez sur Suivant, sélectionnez Créer un nouveau périphérique AXI4, cliquez sur Suivant,

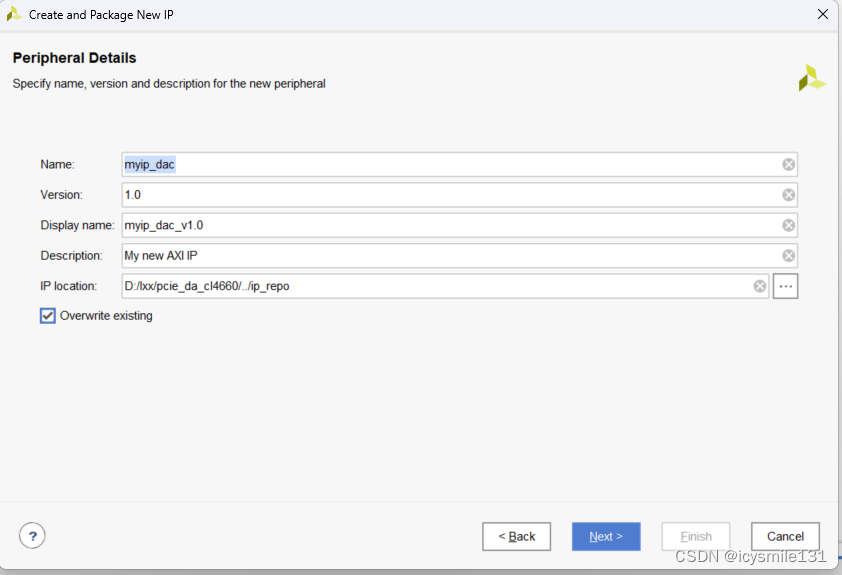

Entrez le nom du noyau IP à générer dans Nom et sélectionnez Écraser l'existant. Lorsque l'IP doit être régénérée, la conception d'origine sera automatiquement écrasée.

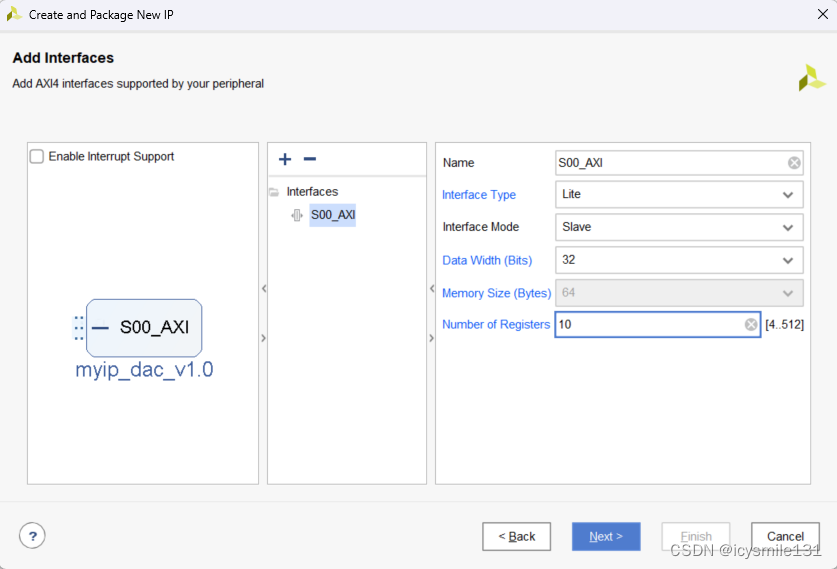

Cliquez sur Suivant, la largeur des données (bits) est la largeur des données, le nombre de registres est le nombre de registres, vous devez ici entrer des paramètres qui répondent aux exigences de conception, cliquez sur Suivant,

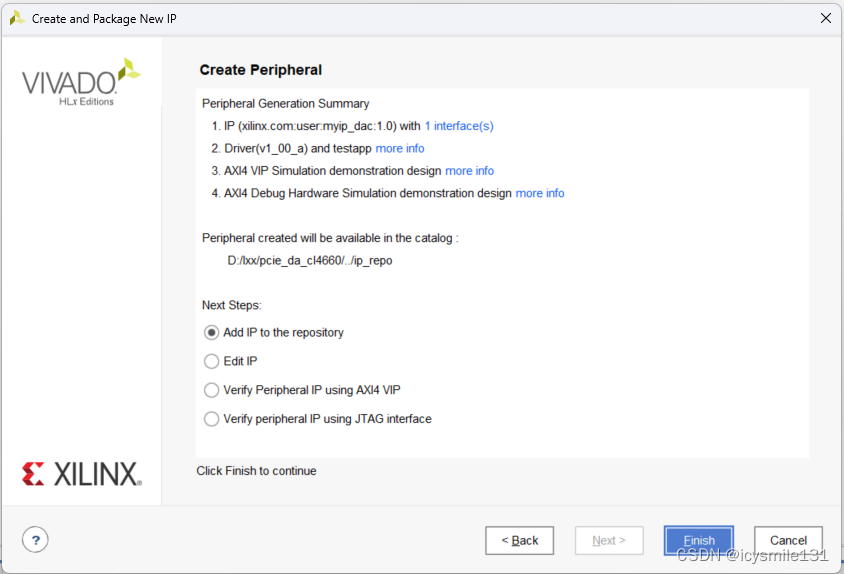

Cliquez sur Terminer,

Double-cliquez sur le catalogue IP dans PROJECT MANAGER et double-cliquez sur le noyau IP nouvellement généré myip_dac_v1.0 dans le catalogue IP à droite.

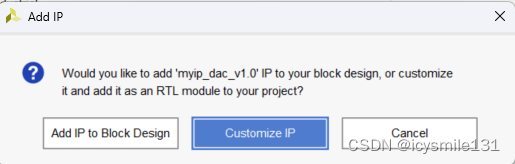

Cliquez sur Ajouter une adresse IP à la conception de blocs dans le nouveau menu contextuel.

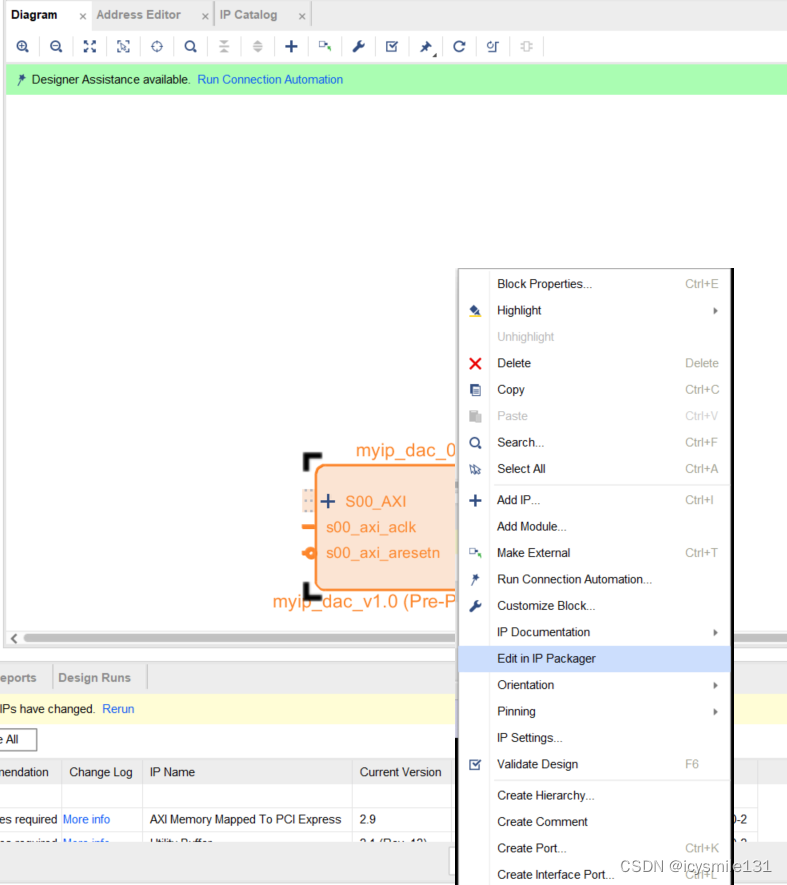

Sélectionnez le noyau IP myip_dac_v1.0, cliquez avec le bouton droit et sélectionnez Modifier dans le packageur IP dans le menu contextuel.

Sélectionnez OK dans le menu contextuel pour commencer à modifier le noyau IP personnalisé nouvellement généré.