Mi informacion de contacto

Correo[email protected]

2024-07-08

한어Русский языкEnglishFrançaisIndonesianSanskrit日本語DeutschPortuguêsΕλληνικάespañolItalianoSuomalainenLatina

En el diseño de vivado, para utilizar Block Desgin de manera conveniente para el diseño, puede usar el software vivado para encapsular el código que escribió en un núcleo IP. El núcleo IP encapsulado tiene las mismas funciones que el código original. Este artículo toma la implementación de la conversión DA de 24 bits (incluida la conversión de paralelo a serie, el convertidor de digital a analógico utilizado es CL4660) como ejemplo para presentar el método y el método de llamada del núcleo IP empaquetado de VIVADO, así como el proceso detallado de diseño FPGA de conversión DAC y proporciona su código detallado verificado (usando lenguaje Verilog).

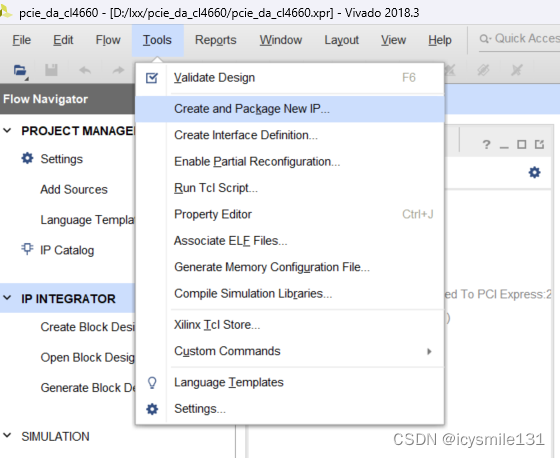

Cree un nuevo proyecto o abra un proyecto existente, haga clic en Herramientas - Crear y empaquetar nueva IP...

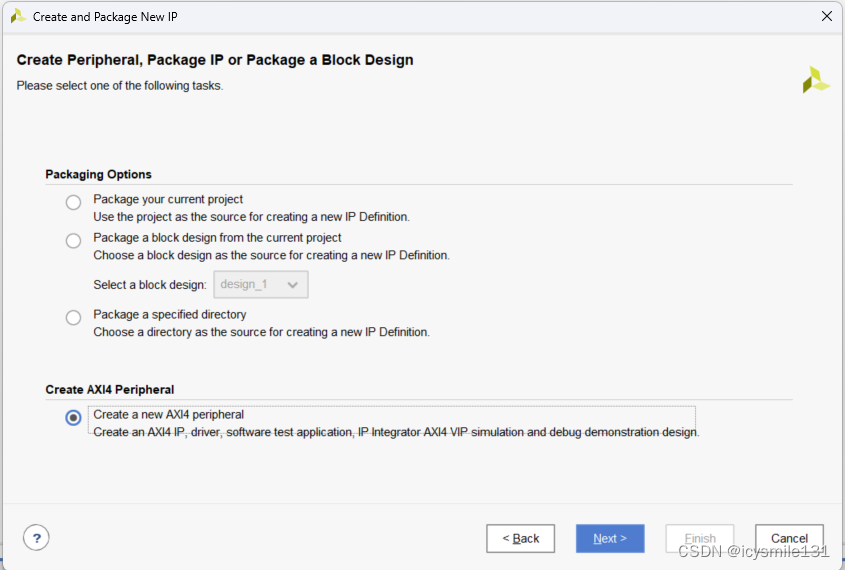

Aparece el siguiente cuadro de diálogo,

Haga clic en Siguiente, seleccione Crear un nuevo periférico AXI4, haga clic en Siguiente,

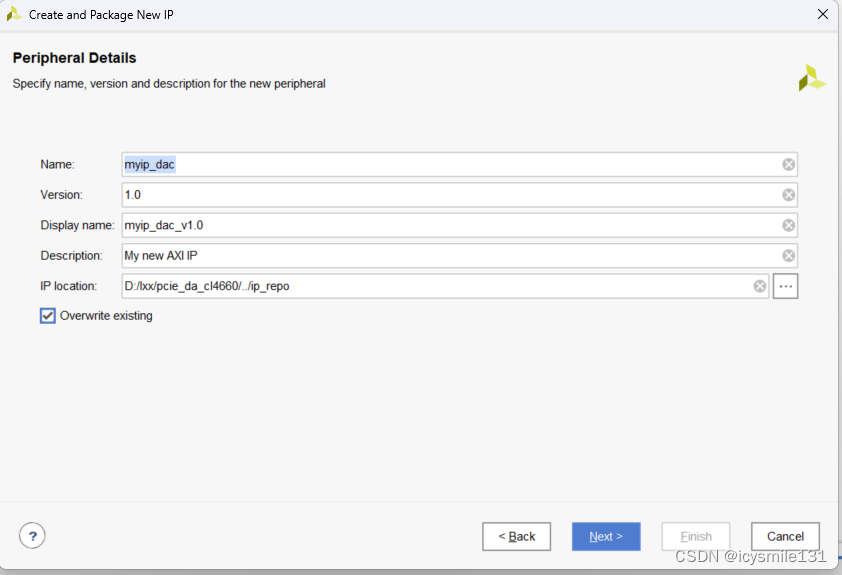

Ingrese el nombre del núcleo de IP que se generará en Nombre y seleccione Sobrescribir existente. Cuando sea necesario regenerar la IP, el diseño original se sobrescribirá automáticamente.

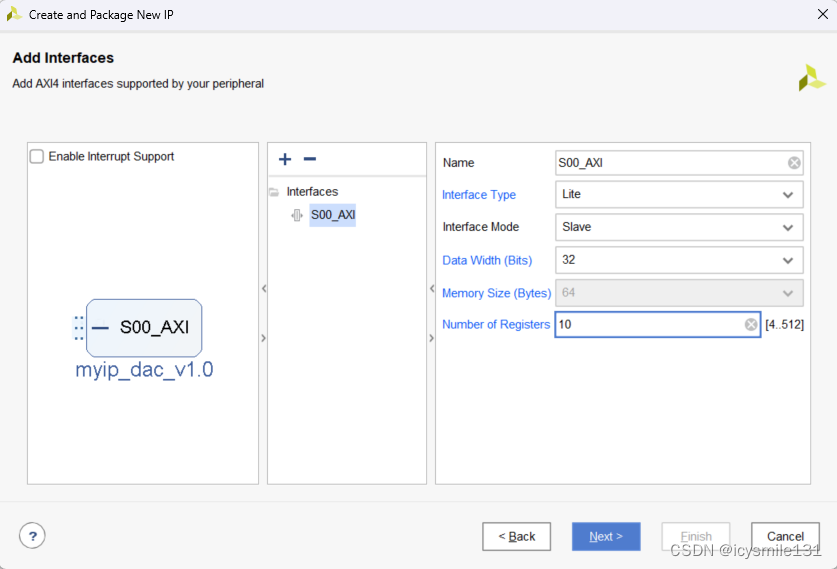

Haga clic en Siguiente, Ancho de datos (Bits) es el ancho de datos, Número de registros es el número de registros, aquí debe ingresar parámetros que cumplan con los requisitos de diseño, haga clic en Siguiente,

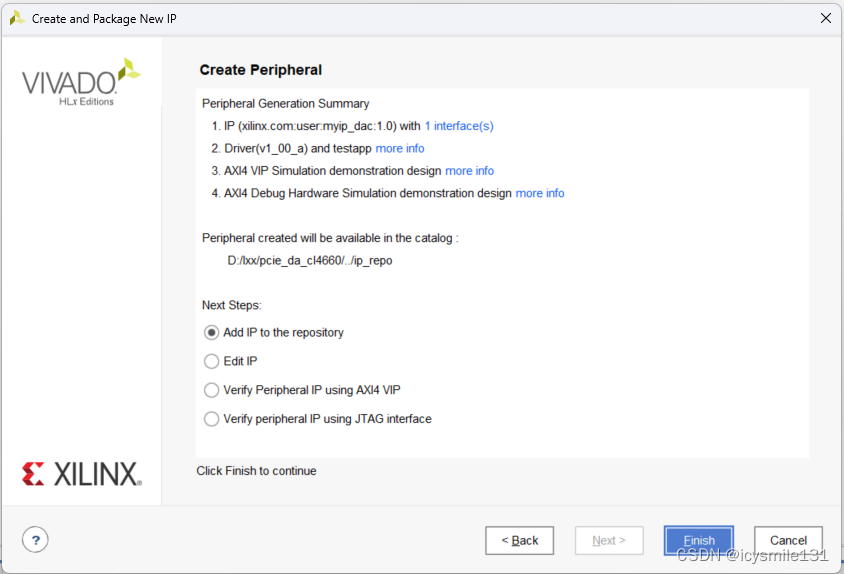

Haga clic en Finalizar,

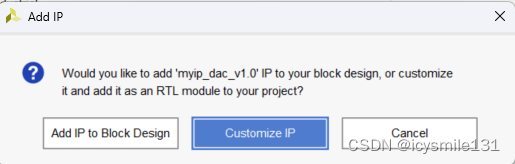

Haga doble clic en el Catálogo de IP en el ADMINISTRADOR DE PROYECTOS y haga doble clic en el núcleo de IP recién generado myip_dac_v1.0 en el Catálogo de IP de la derecha.

Haga clic en Agregar IP al diseño de bloque en el nuevo menú emergente.

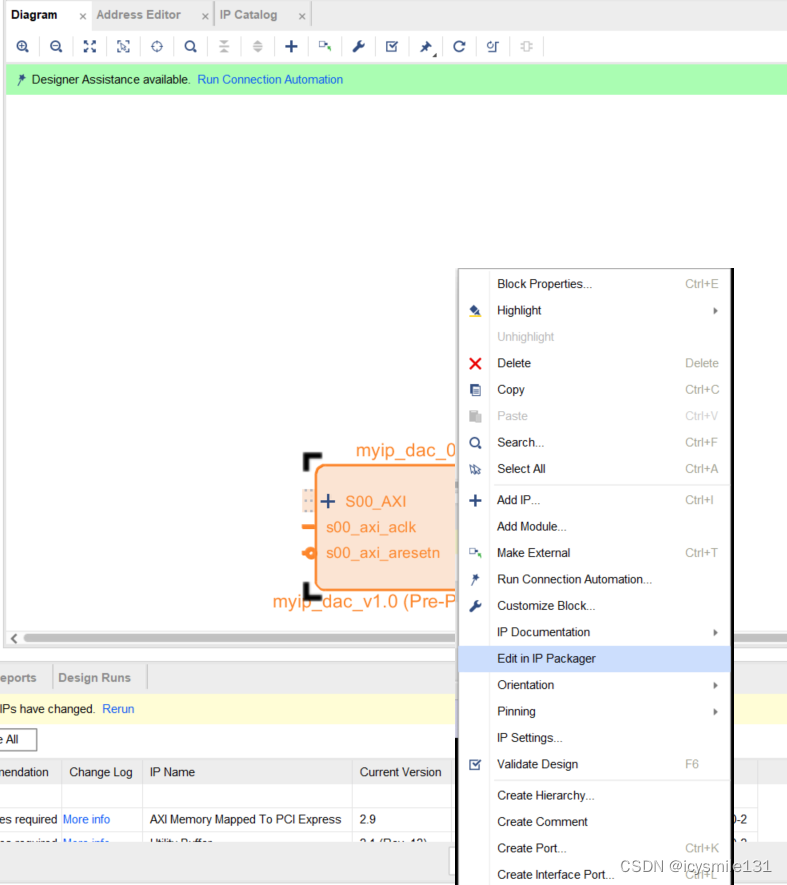

Seleccione el núcleo IP myip_dac_v1.0, haga clic derecho y seleccione Editar en empaquetador IP en el menú emergente.

Seleccione Aceptar en el menú emergente para comenzar a editar el núcleo de IP personalizado recién generado.