2024-07-08

한어Русский языкEnglishFrançaisIndonesianSanskrit日本語DeutschPortuguêsΕλληνικάespañolItalianoSuomalainenLatina

Vivado-suunnittelussa, jotta voit käyttää Block Desginiä kätevästi suunnittelussa, voit käyttää vivado-ohjelmistoa kapseloimaan kirjoittamasi koodi IP-ytimeen. Kapseloidulla IP-ytimellä on samat toiminnot kuin alkuperäisellä koodilla. Tämä artikkeli ottaa 24-bittisen DA-muunnoksen toteutuksen (mukaan lukien rinnakkais-sarjamuunnos, käytetty digitaali-analogi-muunnin on CL4660) esimerkkinä VIVADO-paketin IP-ytimen menetelmän ja kutsumistavan sekä DAC-muunnoksen yksityiskohtaisen FPGA-suunnitteluprosessin ja tarjoaa sen varmennetun yksityiskohtaisen koodin (Verilog-kielellä).

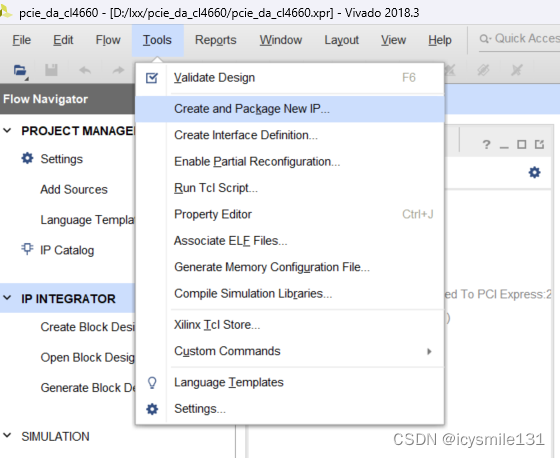

Luo uusi projekti tai avaa olemassa oleva projekti, napsauta Työkalut - Luo ja pakkaa uusi IP...

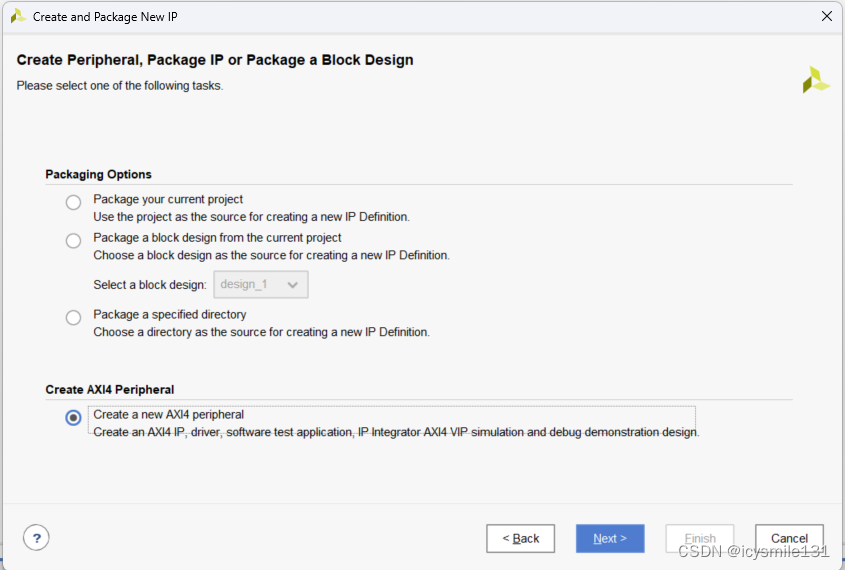

Seuraava valintaikkuna avautuu,

Napsauta Seuraava, valitse Luo uusi AXI4-oheislaite, napsauta Seuraava,

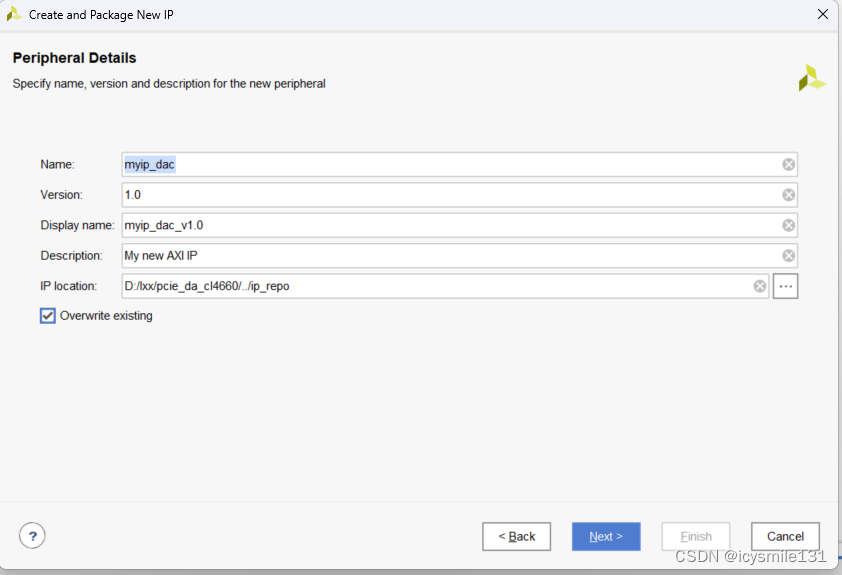

Kirjoita luotavan IP-ytimen nimi kohtaan Nimi ja valitse Korvaa olemassa oleva, kun IP-osoite on luotava uudelleen, alkuperäinen rakenne korvataan automaattisesti.

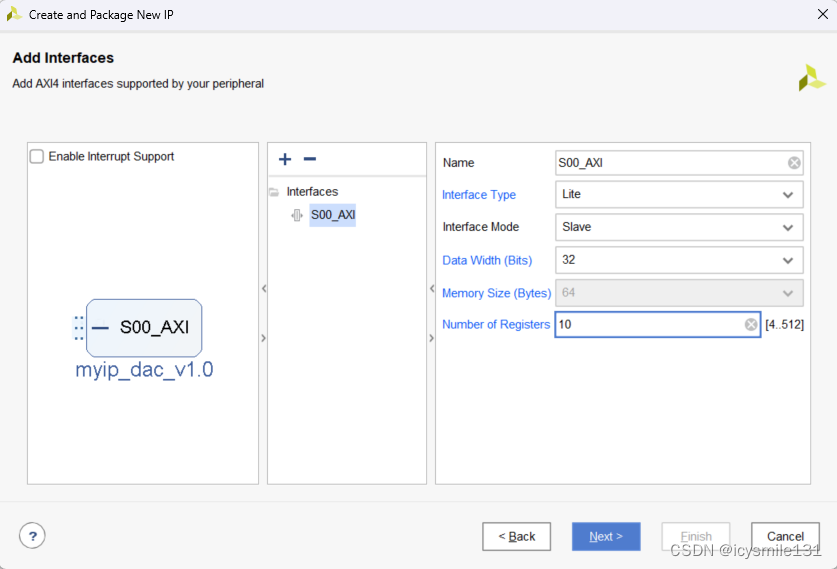

Napsauta Seuraava, Data Width (Bits) on datan leveys, Number of Registers on rekisterien määrä, tähän sinun on syötettävä parametrit, jotka täyttävät suunnitteluvaatimukset, napsauta Seuraava,

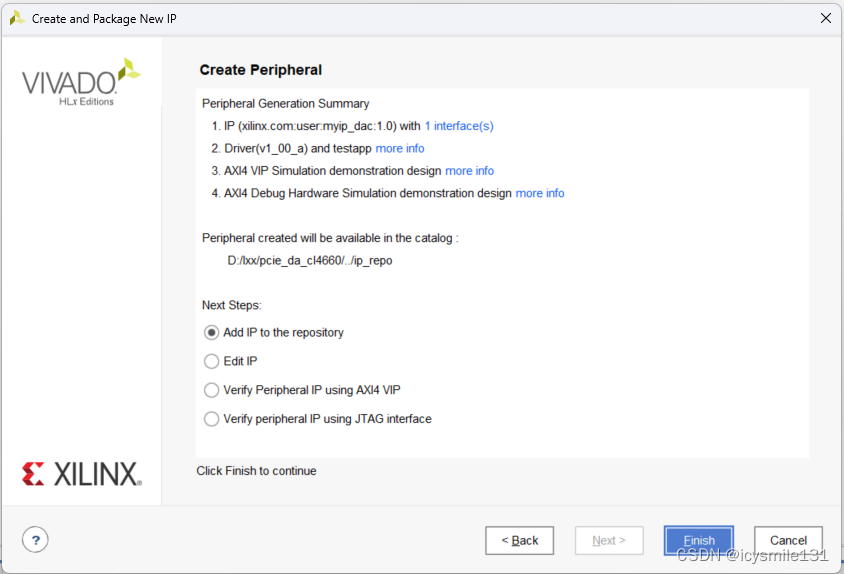

Napsauta Valmis,

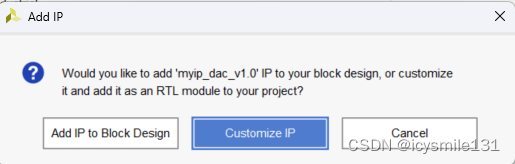

Kaksoisnapsauta IP-luetteloa PROJEKTINHALLINTA-ohjelmassa ja kaksoisnapsauta juuri luotua IP-ydintä myip_dac_v1.0 oikealla olevassa IP-katalogissa.

Napsauta Lisää IP lohkosuunnitteluun uudessa ponnahdusvalikosta.

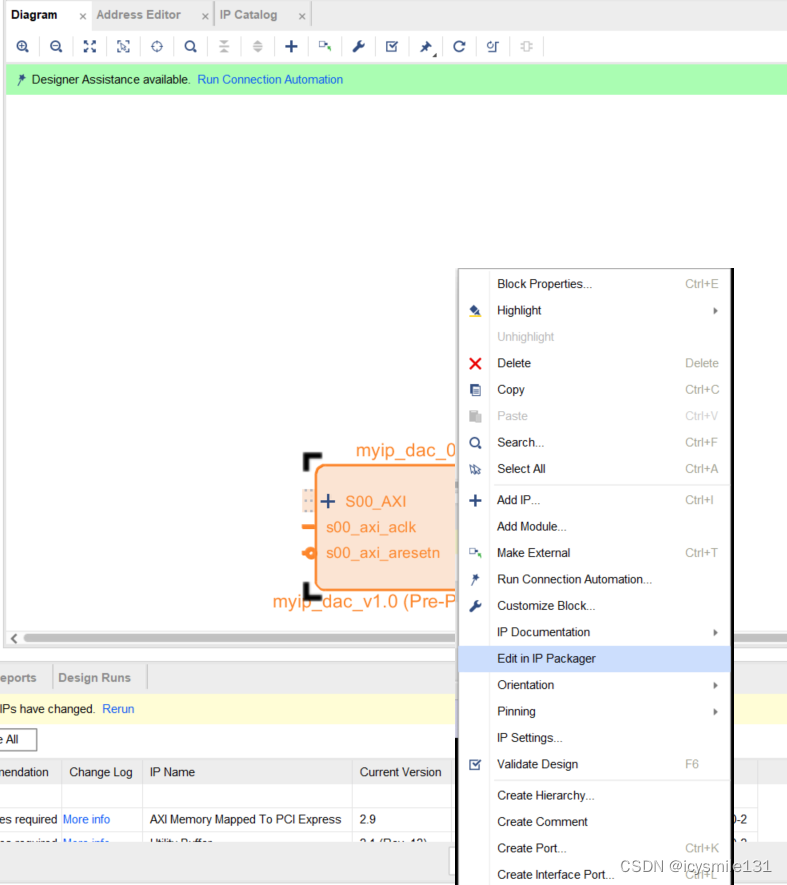

Valitse myip_dac_v1.0 IP-ydin, napsauta hiiren kakkospainikkeella ja valitse ponnahdusvalikosta Muokkaa IP-pakettiohjelmassa.

Aloita juuri luodun mukautetun IP-ytimen muokkaaminen valitsemalla ponnahdusvalikosta OK.