2024-07-08

한어Русский языкEnglishFrançaisIndonesianSanskrit日本語DeutschPortuguêsΕλληνικάespañolItalianoSuomalainenLatina

In vivado design, in order to facilitate the use of Block Desgin for design, you can use vivado software to encapsulate your own code into an IP core. The encapsulated IP core has the same function as the original code. This article takes the implementation of 24-bit DA conversion (including parallel-to-serial conversion, the digital-to-analog converter used is CL4660) as an example to introduce the VIVADO encapsulation IP core method and calling method, as well as the detailed FPGA design process of DAC conversion, and provides its verified detailed code (using Verilog language).

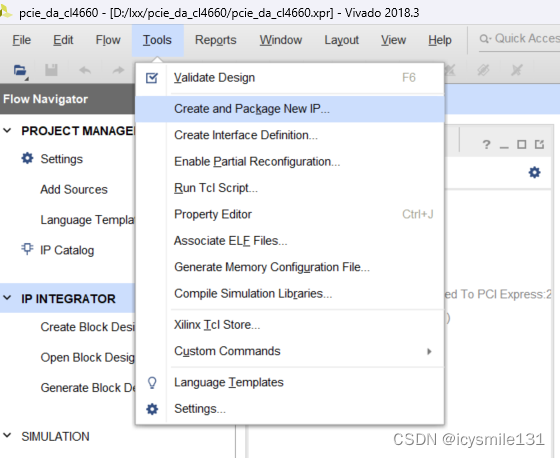

Create a new project, or open an existing project, click Tools - Create and Package New IP...

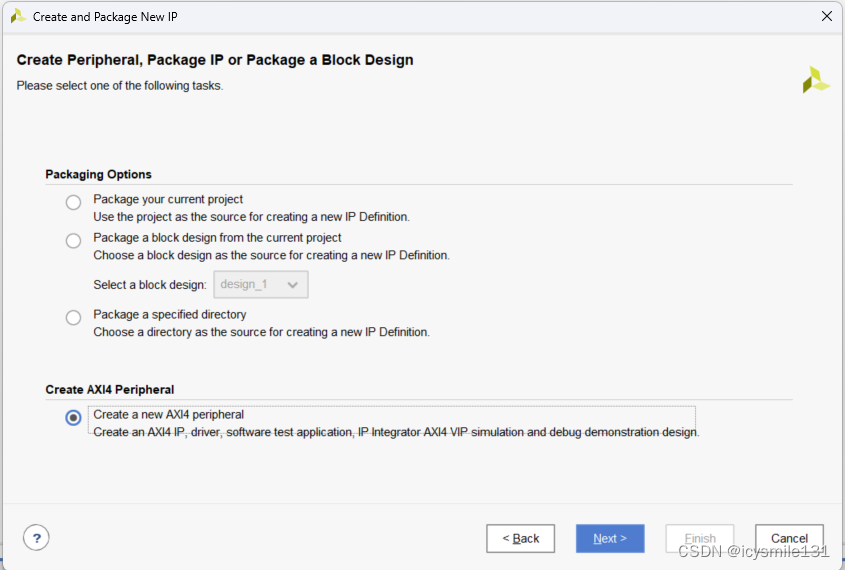

The following dialog box pops up.

Click Next, select Create a new AXI4 peripheral, click Next,

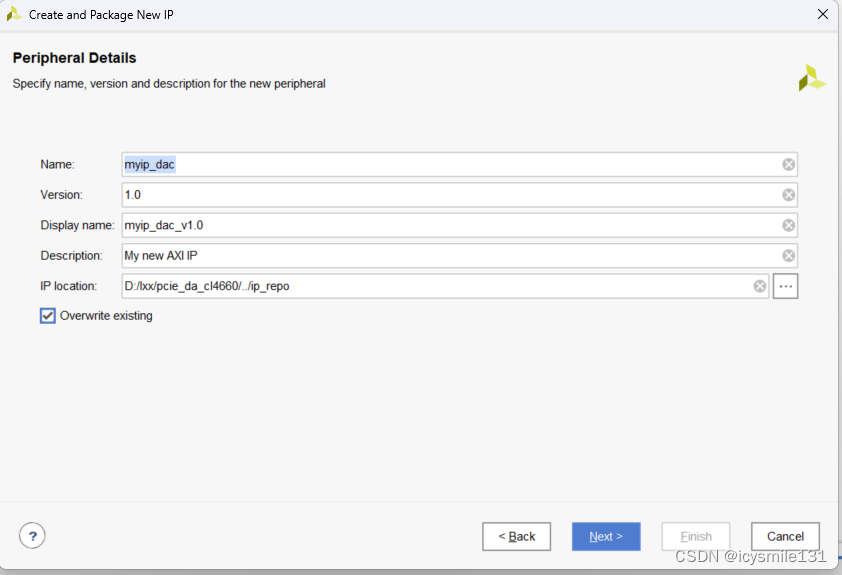

Enter the name of the IP core to be generated in Name, select Overwrite existing, and when you need to regenerate the IP, the original design will be automatically overwritten.

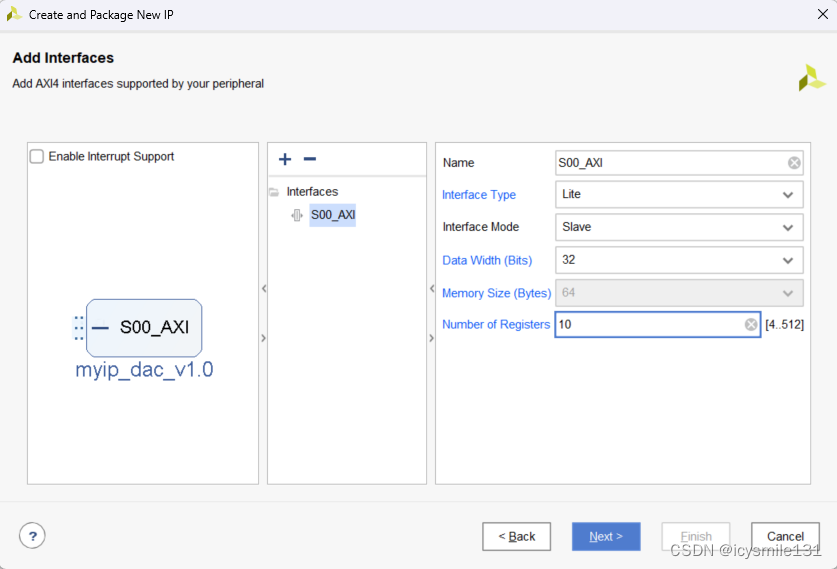

Click Next, Data Width (Bits) is the data width, Number of Registers is the number of registers, here you need to enter the parameters that meet the design requirements, click Next,

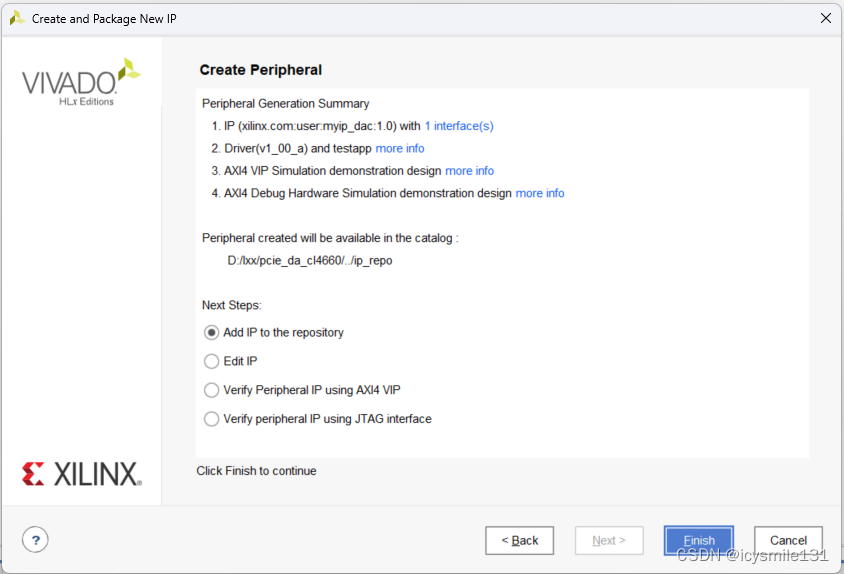

Click Finish.

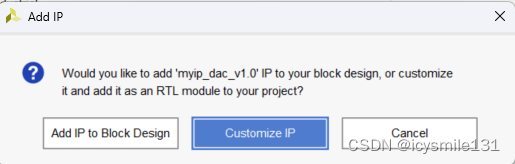

Double-click the IP Catalog in the PROJECT MANAGER, and double-click the newly generated IP core myip_dac_v1.0 in the IP Catalog on the right.

Click Add IP to Block Design in the new pop-up menu.

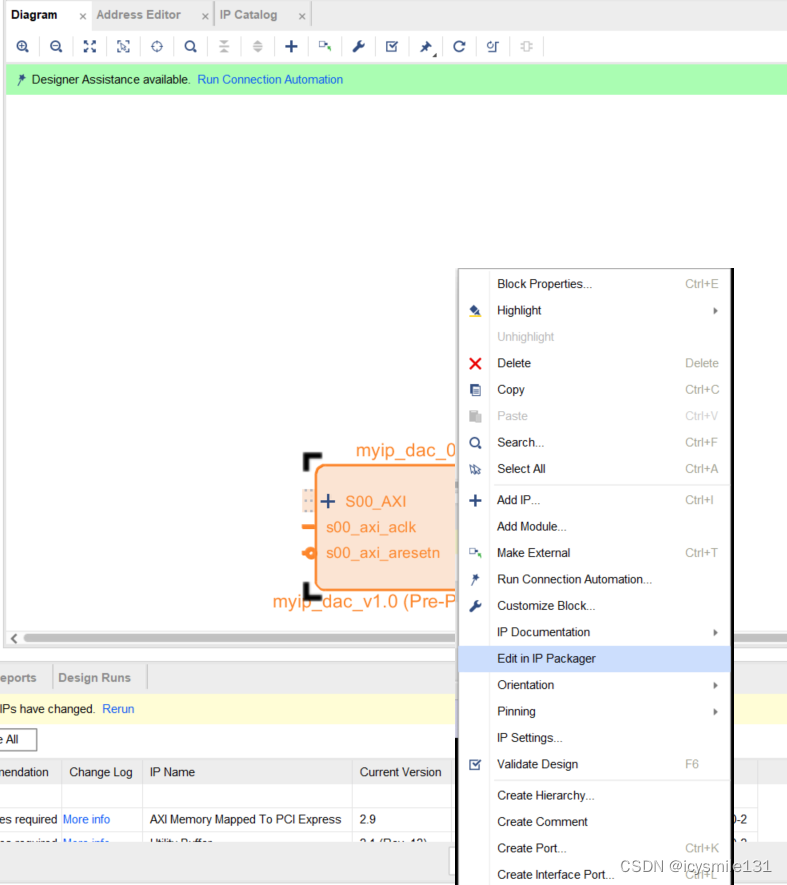

Select the myip_dac_v1.0 IP core, right-click, and select Edit in IP packager from the pop-up menu.

Select OK in the pop-up menu to start editing the newly generated custom IP core.