minhas informações de contato

Correspondência[email protected]

2024-07-08

한어Русский языкEnglishFrançaisIndonesianSanskrit日本語DeutschPortuguêsΕλληνικάespañolItalianoSuomalainenLatina

No design vivado, para usar convenientemente o Block Desgin para design, você pode usar o software vivado para encapsular o código que você escreveu em um núcleo IP. O núcleo IP encapsulado tem as mesmas funções do código original. Este artigo toma a implementação da conversão DA de 24 bits (incluindo conversão paralela para serial, o conversor digital para analógico usado é CL4660) como exemplo para apresentar o método e método de chamada do núcleo IP de empacotamento VIVADO, bem como o processo detalhado de design FPGA de conversão DAC e fornece seu código detalhado verificado (usando a linguagem Verilog).

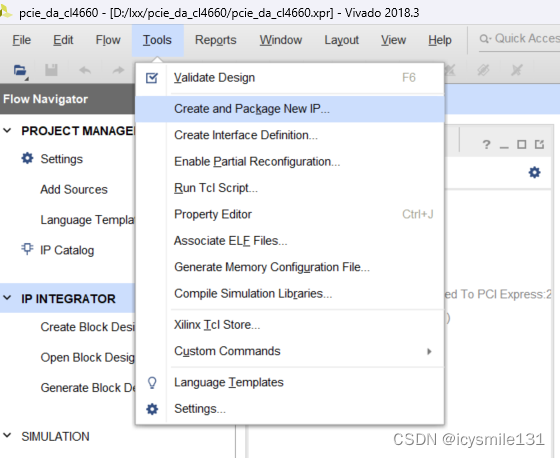

Crie um novo projeto ou abra um projeto existente, clique em Ferramentas - Criar e empacotar novo IP...

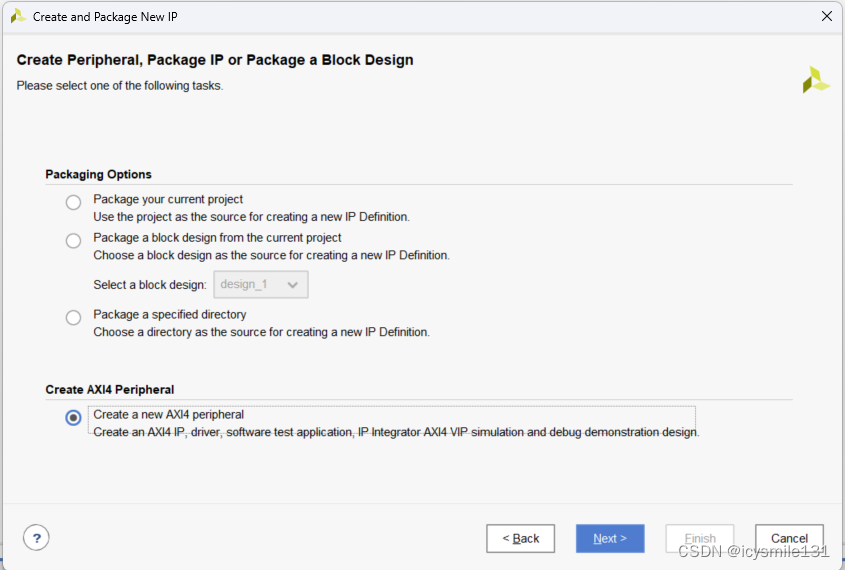

A seguinte caixa de diálogo é exibida,

Clique em Avançar, selecione Criar um novo periférico AXI4, clique em Avançar,

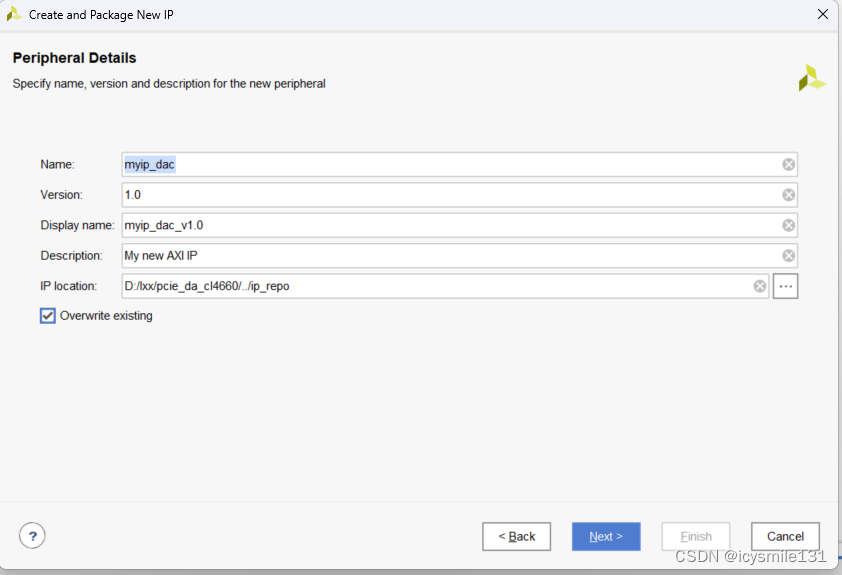

Insira o nome do núcleo IP a ser gerado em Nome e selecione Substituir existente. Quando o IP precisar ser regenerado, o design original será automaticamente substituído.

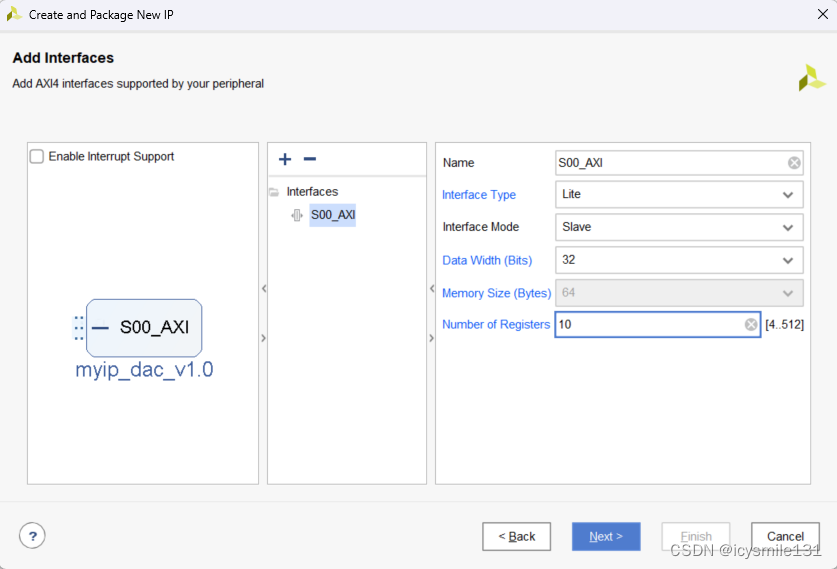

Clique em Avançar, Largura de dados (Bits) é a largura dos dados, Número de registros é o número de registros, aqui você precisa inserir parâmetros que atendam aos requisitos de design, clique em Avançar,

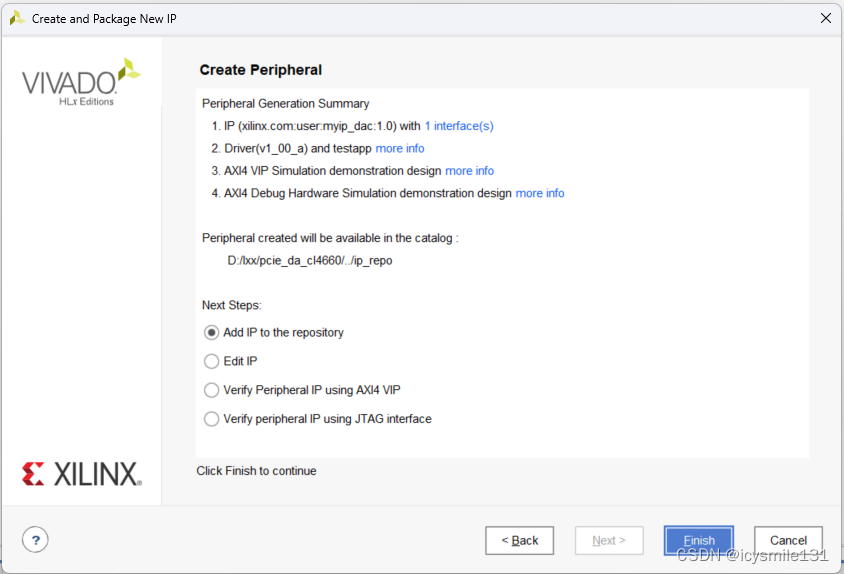

Clique em Concluir,

Clique duas vezes no Catálogo IP no PROJECT MANAGER e clique duas vezes no núcleo IP recém-gerado myip_dac_v1.0 no Catálogo IP à direita.

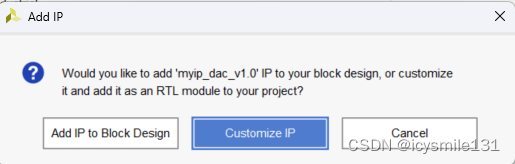

Clique em Adicionar IP ao Block Design no novo menu pop-up.

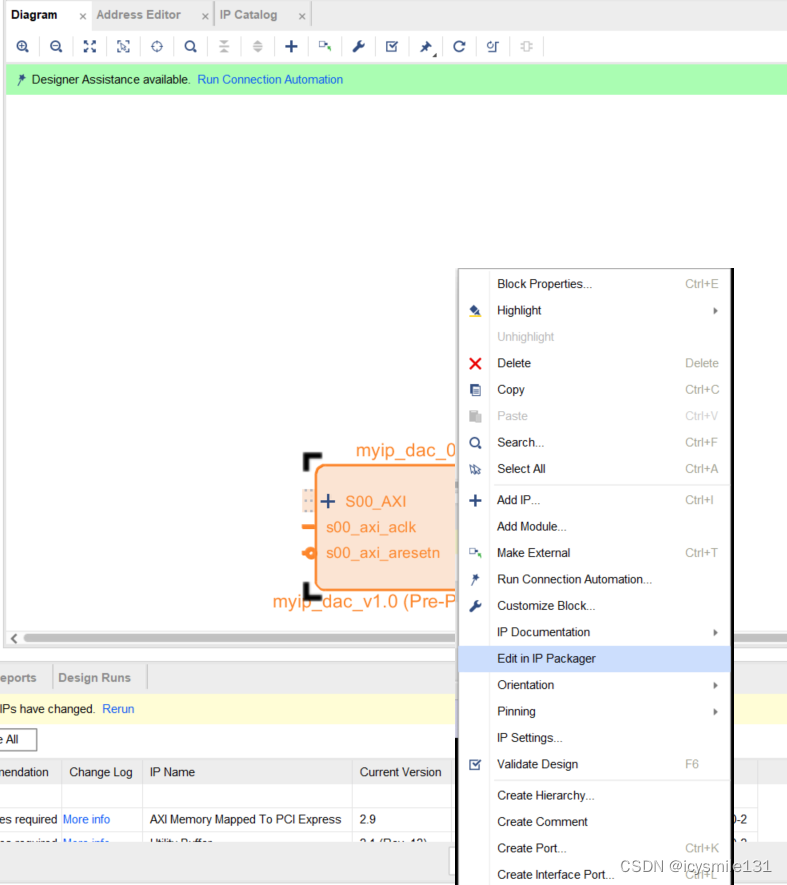

Selecione o núcleo IP myip_dac_v1.0, clique com o botão direito e selecione Editar no empacotador IP no menu pop-up.

Selecione OK no menu pop-up para começar a editar o núcleo IP personalizado recém-gerado.