τα στοιχεία επικοινωνίας μου

Ταχυδρομείο[email protected]

2024-07-12

한어Русский языкEnglishFrançaisIndonesianSanskrit日本語DeutschPortuguêsΕλληνικάespañolItalianoSuomalainenLatina

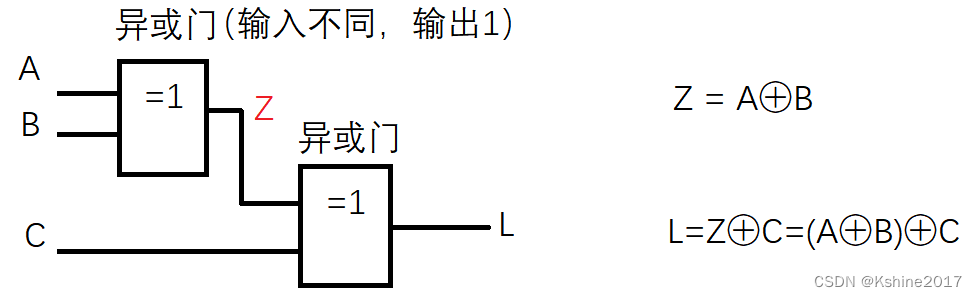

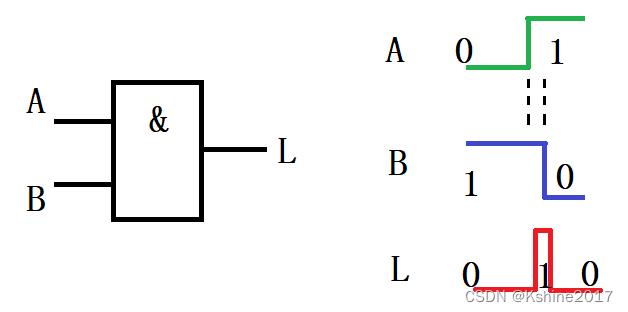

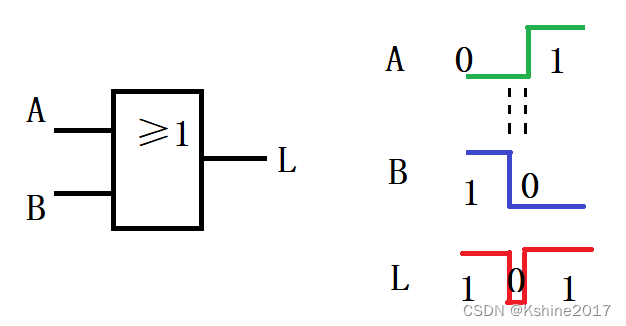

(1) Όπως φαίνεται στο παρακάτω σχήμα.

(2) Καταγράψτε τον πίνακα αλήθειας

| ΕΝΑ | σι | ντο | Ζ | μεγάλο |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 | 1 |

| 0 | 1 | 0 | 1 | 1 |

| 0 | 1 | 1 | 1 | 0 |

| 1 | 0 | 0 | 1 | 1 |

| 1 | 0 | 1 | 1 | 0 |

| 1 | 1 | 0 | 0 | 0 |

| 1 | 1 | 1 | 0 | 1 |

(3) ΑναλύστεΚύκλωμα περιττής ισοτιμίαςΛειτουργία.

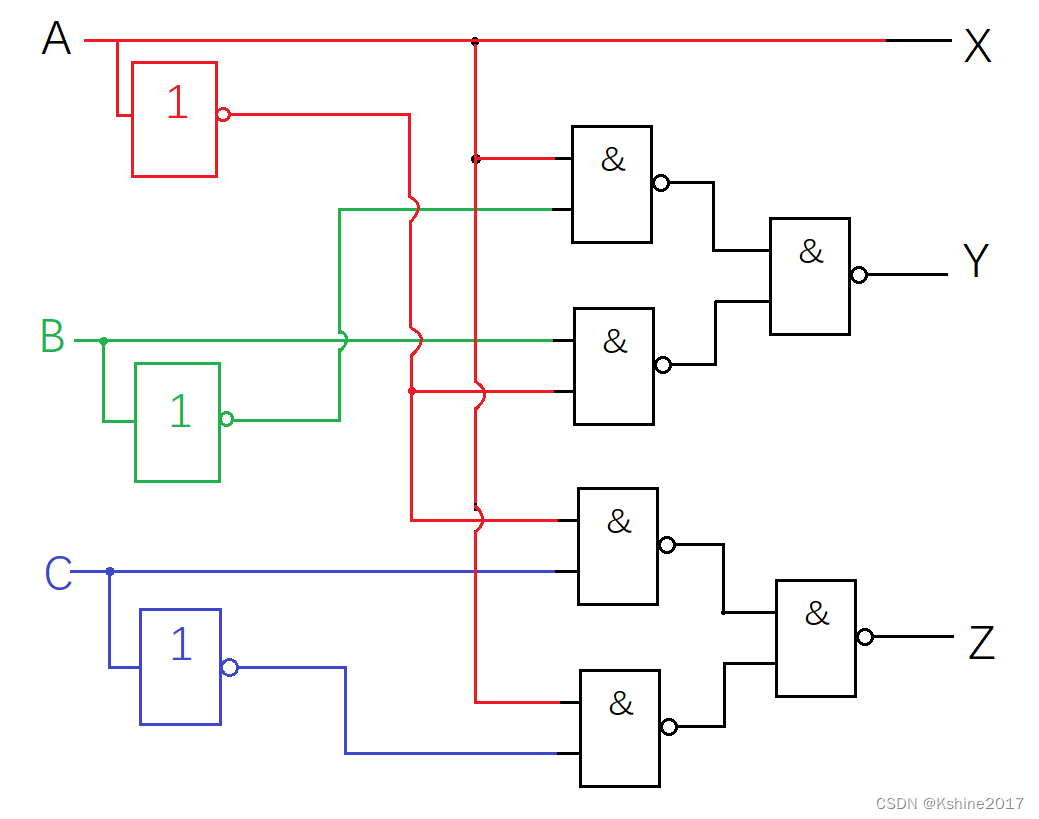

(1) Με βάση το κύκλωμα περιττής ισοτιμίας, προσθέτοντας έναν μετατροπέα στο άκρο εξόδου, μπορούμε να πάρουμεΚύκλωμα ομοιόμορφης ισοτιμίας。

| ΕΝΑ | σι | ντο | Χ | Υ | Ζ |

|---|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 | 0 | 1 |

| 0 | 1 | 0 | 0 | 1 | 0 |

| 0 | 1 | 1 | 0 | 1 | 1 |

| 1 | 0 | 0 | 1 | 1 | 1 |

| 1 | 0 | 1 | 1 | 1 | 0 |

| 1 | 1 | 0 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 | 0 | 0 |

χρειάζομαι.

(1) Χρησιμοποιήστε 2 εισόδουςΠύλη NAND,αντιστροφέας.

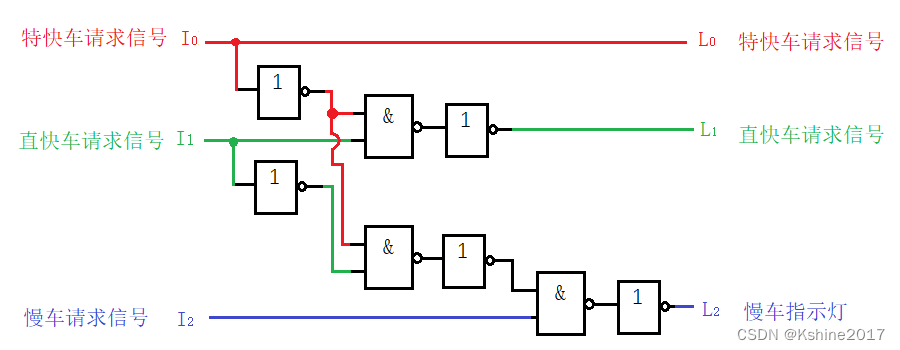

(2) Νο. 1 ενδεικτική λυχνία, ενδεικτική λυχνία άφιξης τρένου ταχείας κυκλοφορίας. Υψηλή προτεραιότητα.

(3) Ενδεικτική λυχνία Νο. 2, αμαξοστοιχία άμεσης ταχύτητας που εισέρχεται στην ενδεικτική λυχνία σταθμού. Σε προτεραιότητα.

(4) Ενδεικτική λυχνία Νο. 3, αργή αμαξοστοιχία που εισέρχεται στην ενδεικτική λυχνία του σταθμού. Χαμηλή προτεραιότητα.

(5) Το πολύ μια ενδεικτική λυχνία μπορεί να ανάβει ταυτόχρονα.

Ορισμός μεταβλητών εισόδου και εξόδου.

(1) Σήμα εισόδου, I 0 ρητή αίτηση, I 1 άμεση ρητή αίτηση, I 2 τοπικό αίτημα τρένου I_0 ρητή αίτηση, I_1 άμεση ρητή αίτηση, I_2 αίτημα τοπικού τρένουΕγώ0ρητή αίτηση,Εγώ1Απλά ζητήστε το γρήγορα,Εγώ2Αίτημα αργού τρένου . Το 1 σημαίνει ότι υπάρχει εισερχόμενο αίτημα, το 0 σημαίνει ότι δεν υπάρχει εισερχόμενο αίτημα.

(2) Σήμα εξόδου, L 0 ενδεικτική λυχνία ταχείας στάσης, L 1 ενδεικτική λυχνία άμεσης στάσης τρένου, L 2 ενδεικτική λυχνία τοπικής στάσης τρένου L_0 ενδεικτική λυχνία ταχείας στάσης, L_1 ενδεικτική λυχνία άμεσης γρήγορης στάσης, L_2 ενδεικτική λυχνία τοπικής στάσης τρένουμεγάλο0Φως άφιξης Express,μεγάλο1Ενδεικτική λυχνία άμεσης στάσης,μεγάλο2Ενδεικτική λυχνία αργής άφιξης τρένου . Το 1 σημαίνει ότι το φως είναι αναμμένο, το 0 σημαίνει ότι το φως είναι σβηστό.

Πίνακας αλήθειας.

| εισαγω | παραγωγή | ||||

| I_0 | I_1 | I_2 | L_0 | L_1 | L_2 |

| 0 | 0 | 0 | 0 | 0 | 0 |

| 1 | Χ | Χ | 1 | 0 | 0 |

| 0 | 1 | Χ | 0 | 1 | 0 |

| 0 | 0 | 1 | 0 | 0 | 1 |

Κατάλογος λογικών εκφράσεων

L 0 = I 0 L_0 = I_0μεγάλο0=Εγώ0

L 1 = I 0 ‾ ⋅ I 1 L_1 = overline{I_0}·I_1μεγάλο1=Εγώ0⋅Εγώ1

L 2 = I 0 ‾ ⋅ I 1 ‾ ⋅ I 2 L_2 = overline{I_0}·overline{I_1}·I_2μεγάλο2=Εγώ0⋅Εγώ1⋅Εγώ2

Μετατρέψτε σε φόρμα NAND όπως απαιτείται.

L 0 = I 0 L_0 = I_0μεγάλο0=Εγώ0

L 1 = I 0 ‾ ⋅ I 1 ‾ ‾ L_1 = overline{overline{overline{I_0}·I_1}}μεγάλο1=Εγώ0⋅Εγώ1

L 2 = I 0 ‾ ⋅ I 1 ‾ ‾ ‾ ⋅ I 2 ‾ ‾ L_2 =overline{overline{overline{overline{overline{I_0}·overline{I_1}}}·I_2}}μεγάλο2=Εγώ0⋅Εγώ1⋅Εγώ2

Σχεδιάστε ένα λογικό διάγραμμα.

(1) Ένα τσιπ 74HC00 περιέχει τέσσερις πύλες CMOS NAND 2 εισόδων.

(2) Ένα τσιπ 74HC04 περιέχει 6 μετατροπείς CMOS.

χρειάζομαι.

(1) Μπορεί να χρησιμοποιηθεί οποιοδήποτε κύκλωμα λογικής πύλης.

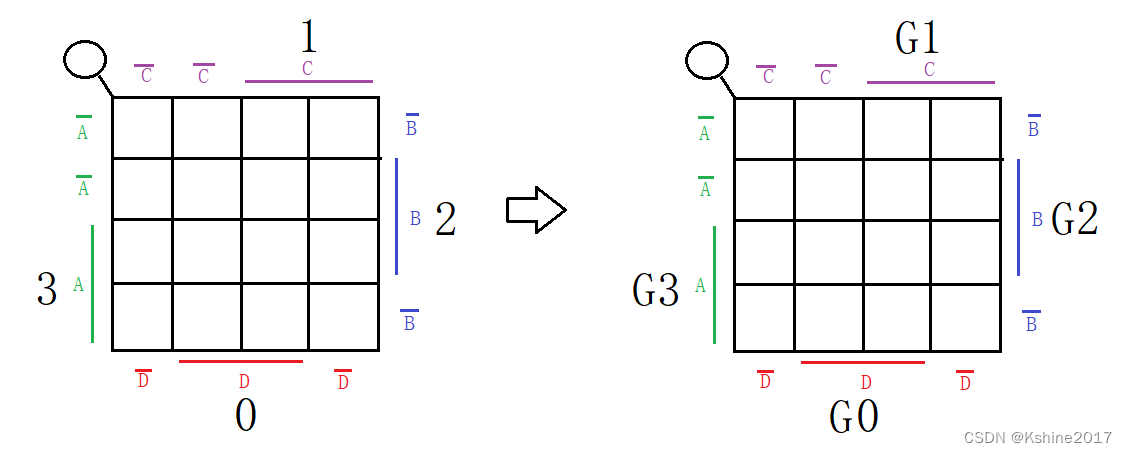

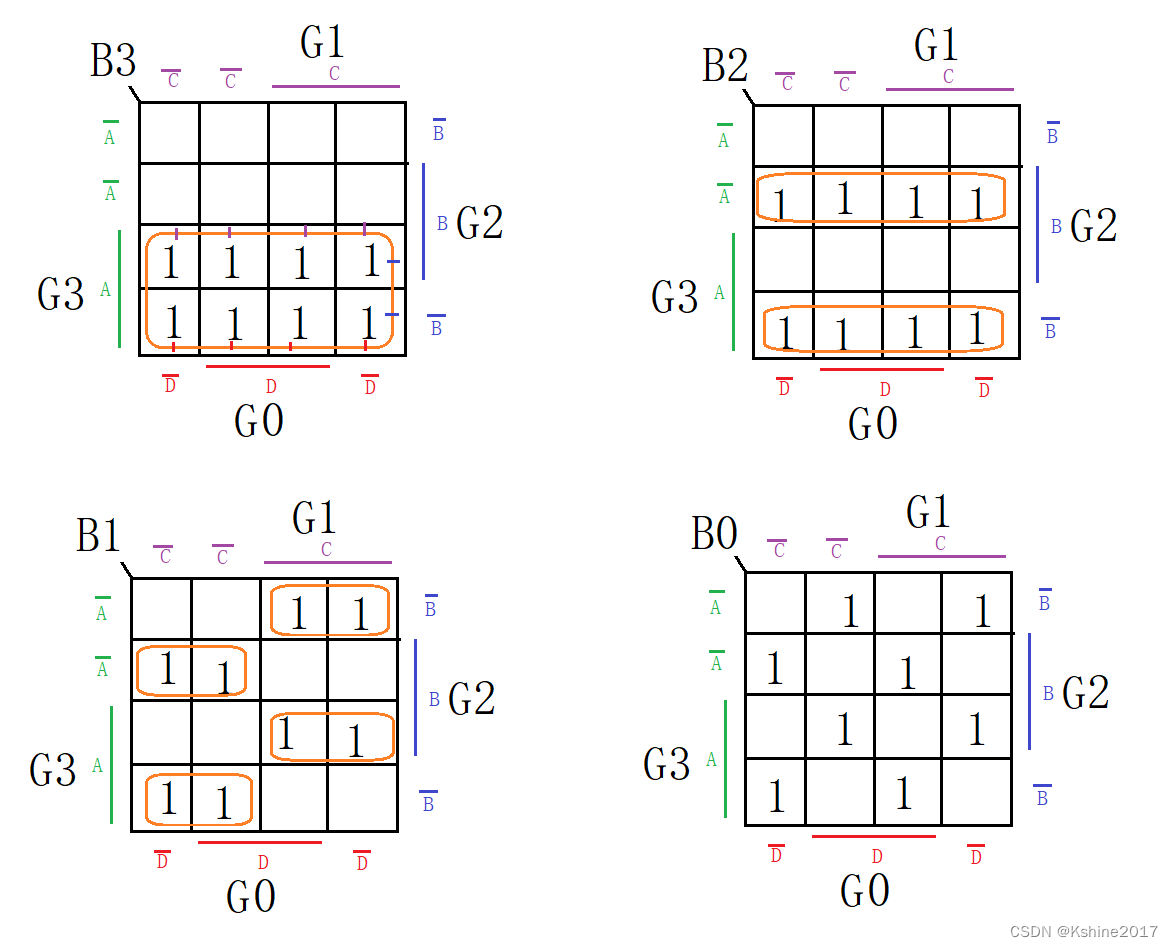

(2) Γκρι κώδικας 4 bit, που μετατράπηκε σε φυσικό δυαδικό κώδικα.

Ορισμός μεταβλητών εισόδου και εξόδου.

(1) Μεταβλητές εισόδου, G 3 , G 2 , G 1 , G 0 G_3,G_2,G_1,G_0σολ3,σολ2,σολ1,σολ0。

(2) Μεταβλητές εξόδου, B 3 , B 2 , B 1 , B 0 B_3, B_2, B_1, B_0σι3,σι2,σι1,σι0。

Καταγράψτε τον πίνακα αλήθειας.

| εισαγω | παραγωγή | ||||||

| G_3 | G_2 | G_1 | G_0 | B_3 | Β_2 | B_1 | B_0 |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 0 | 1 | 0 | 0 | 0 | 1 |

| 0 | 0 | 1 | 1 | 0 | 0 | 1 | 0 |

| 0 | 0 | 1 | 0 | 0 | 0 | 1 | 1 |

| 0 | 1 | 1 | 0 | 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 1 | 0 | 1 | 0 | 1 |

| 0 | 1 | 0 | 1 | 0 | 1 | 1 | 0 |

| 0 | 1 | 0 | 0 | 0 | 1 | 1 | 1 |

| 1 | 1 | 0 | 0 | 1 | 0 | 0 | 0 |

| 1 | 1 | 0 | 1 | 1 | 0 | 0 | 1 |

| 1 | 1 | 1 | 1 | 1 | 0 | 1 | 0 |

| 1 | 1 | 1 | 0 | 1 | 0 | 1 | 1 |

| 1 | 0 | 1 | 0 | 1 | 1 | 0 | 0 |

| 1 | 0 | 1 | 1 | 1 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 | 1 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 | 1 | 1 | 1 | 1 |

Σχεδιάστε έναν χάρτη Karnaugh με βάση τον πίνακα αλήθειας.

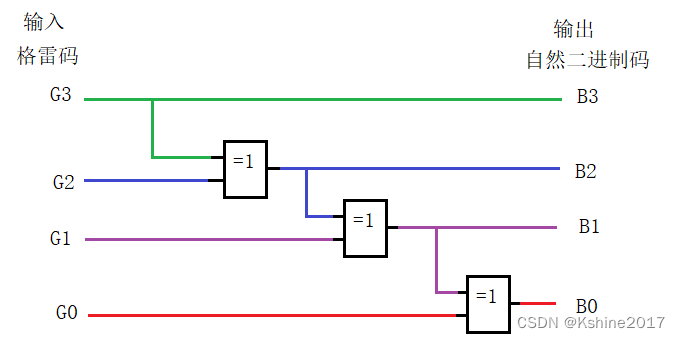

Κατάλογος λογικών εκφράσεων.

B 3 = G 3 B_3 = G_3σι3=σολ3

B 2 = G 3 ‾ ⋅ G 2 + G 3 ⋅ G 2 ‾ = G 3 ⊕ G 2 B_2 = overline{G_3}·G_2 + G_3·overline{G_2}=G_3⊕G_2σι2=σολ3⋅σολ2+σολ3⋅σολ2=σολ3⊕σολ2

B 1 = G 3 ‾ G 2 G 1 ‾ + G 3 G 2 ‾ G 1 ‾ + G 3 ‾ G 2 ‾ G 1 + G 3 G 2 G 1 = ( G 3 G 2 ‾ + G 3 ‾ G 2 ) G 1 ‾ + ( G 3 G 2 ‾ + G 3 ‾ G 2 ) ‾ G 1 = G 3 ⊕ G 2 ⊕ G 1 B_1 = overline{G_3}G_2overline{G_1}+G_3overline{G_2}overline{G_1}+ {G_3}overline{G_2}G_1+G_3G_2G_1=(G_3overline{G_2}+overline{G_3}G_2)overline{G_1}+overline{(G_3overline{G_2}+overline{G_3}G_2)}G_1=G_3⊕G_2σι1=σολ3σολ2σολ1+σολ3σολ2σολ1+σολ3σολ2σολ1+σολ3σολ2σολ1=(σολ3σολ2+σολ3σολ2)σολ1+(σολ3σολ2+σολ3σολ2)σολ1=σολ3⊕σολ2⊕σολ1

B 0 = G 3 ⊕ G 2 ⊕ G 1 ⊕ G 0 B_0=G_3⊕G_2⊕G_1⊕G_0σι0=σολ3⊕σολ2⊕σολ1⊕σολ0

Σχεδιάστε ένα λογικό διάγραμμα.

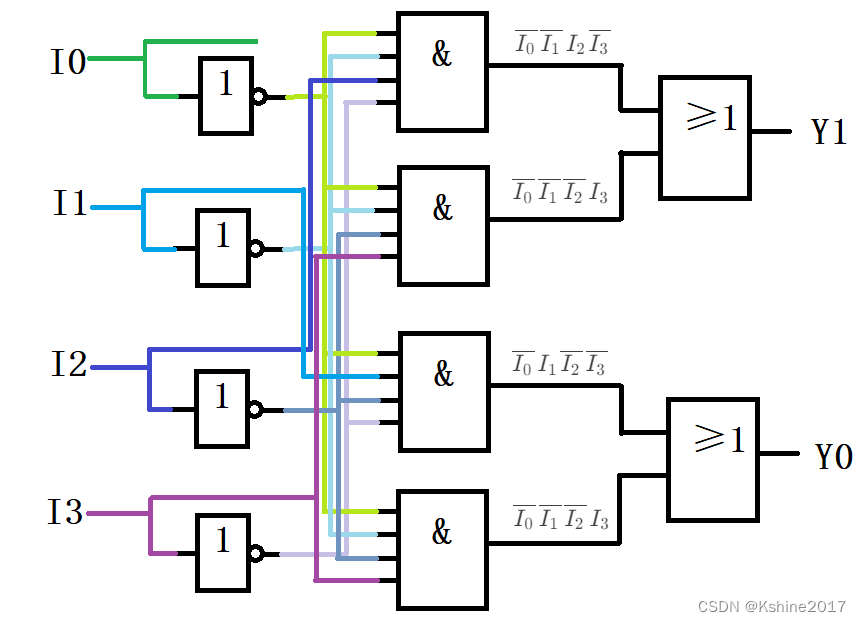

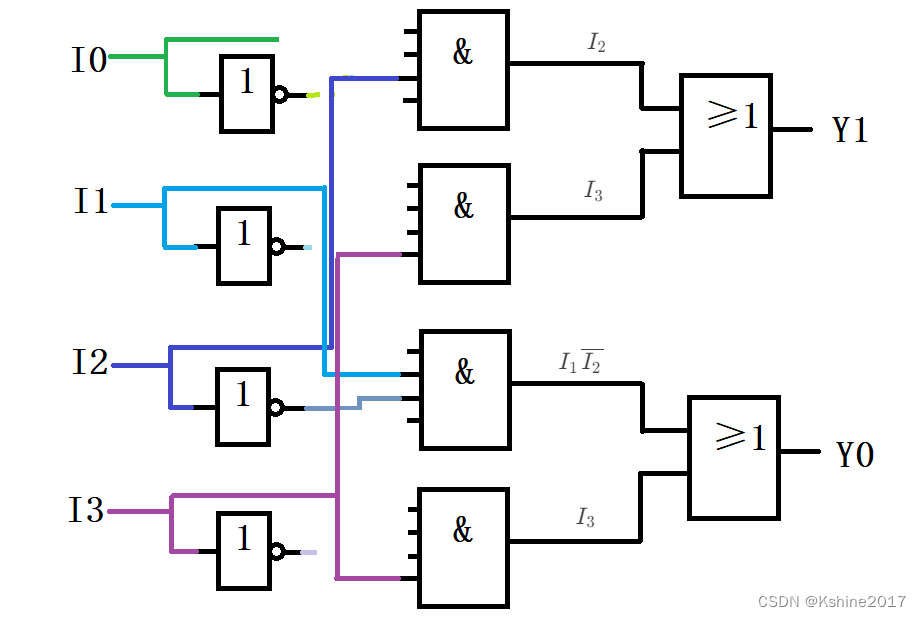

| I 0 I_0Εγώ0 | I 1 I_1Εγώ1 | I 2 I_2Εγώ2 | I 3 I_3Εγώ3 | Υ 1 Υ_1Υ1 | Y 0 Y_0Υ0 |

|---|---|---|---|---|---|

| 1 | 0 | 0 | 0 | 0 | 0 |

| 0 | 1 | 0 | 0 | 0 | 1 |

| 0 | 0 | 1 | 0 | 1 | 0 |

| 0 | 0 | 0 | 1 | 1 | 1 |

| I 0 I_0Εγώ0 | I 1 I_1Εγώ1 | I 2 I_2Εγώ2 | I 3 I_3Εγώ3 | Υ 1 Υ_1Υ1 | Y 0 Y_0Υ0 |

|---|---|---|---|---|---|

| 1 | 0 | 0 | 0 | 0 | 0 |

| Χ | 1 | 0 | 0 | 0 | 1 |

| Χ | Χ | 1 | 0 | 1 | 0 |

| Χ | Χ | Χ | 1 | 1 | 1 |

| S 9 S_9μικρό9 | S 8 S_8μικρό8 | S 7 S_7μικρό7 | S 6 S_6μικρό6 | S 5 S_5μικρό5 | S 4 S_4μικρό4 | S 3 S_3μικρό3 | S 2 S_2μικρό2 | S 1 S_1μικρό1 | S 0 S_0μικρό0 | AAΕΝΑ | ΒΒσι | CCντο | DDρε | ΓΣ ΓΣΓ.Σ | |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | |

| 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | |

| 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 0 | 0 | 0 | 1 | 1 | |

| 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 0 | 0 | 1 | 0 | 1 | |

| 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 0 | 0 | 1 | 1 | 1 | |

| 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 0 | 1 | 0 | 0 | 1 | |

| 1 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 0 | 1 | 1 | |

| 1 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 0 | 1 | |

| 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | |

| 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 1 | |

| 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 1 | 1 |

Τυπικό: Κωδικοποιητής προτεραιότητας CD4532 (δεν συνεχίζεται)

Ο κωδικοποιητής προτεραιότητας I 7 έχει την υψηλότερη προτεραιότητα και ο I 0 τη χαμηλότερη προτεραιότητα. Ο κωδικοποιητής προτεραιότητας I_7 έχει την υψηλότερη προτεραιότητα και ο I_0 έχει τη χαμηλότερη προτεραιότητα.κωδικοποιητής προτεραιότηταςΕγώ7πρώτη προτεραιότητα,Εγώ0Η χαμηλότερη προτεραιότητα.

Όταν EI=1, όταν όλες οι είσοδοι είναι χαμηλού επιπέδου, όχιχαμηλότερη προτεραιότητα Εισαγωγή υψηλού επιπέδου και έξοδος 000 αυτή τη στιγμή. Αυτή τη στιγμή EO=1.

Μόνο όταν EI=1 και όλες οι είσοδοι είναι 0, EO=1. Αφιερωμένο στο EI cascading με άλλη συσκευή.

Όταν EI=1, τουλάχιστον ένας από τους ακροδέκτες εισόδου είναι υψηλού επιπέδου 1 και GS=1.

Ανατρέξτε στο βιβλίο για συγκεκριμένες λογικές εκφράσεις και λογικά μπλοκ διαγράμματα.

| Το EI επιτρέπει την κωδικοποίηση Το EI επιτρέπει την κωδικοποίησημιΕγώΕπιτρέπεται η κωδικοποίηση | I 7 I_7Εγώ7 | I 6 I_6Εγώ6 | I 5 I_5Εγώ5 | I 4 I_4Εγώ4 | I 3 I_3Εγώ3 | I 2 I_2Εγώ2 | I 1 I_1Εγώ1 | I 0 I_0Εγώ0 | Υ 2 Υ_2Υ2 | Υ 1 Υ_1Υ1 | Y 0 Y_0Υ0 | Το GS έχει είσοδο 1 Το GS έχει είσοδο 1Γ.ΣΥπάρχει είσοδος1 | Το EO εισάγει όλα τα 0 Το EO εισάγει όλα τα 0ΕΟΕισαγάγετε όλα0 | |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 0 | Χ | Χ | Χ | Χ | Χ | Χ | Χ | Χ | 0 | 0 | 0 | 0 | 0 | |

| 1 | 1 | Χ | Χ | Χ | Χ | Χ | Χ | Χ | 1 | 1 | 1 | 1 | 0 | |

| 1 | 0 | 1 | Χ | Χ | Χ | Χ | Χ | Χ | 1 | 1 | 0 | 1 | 0 | |

| 1 | 0 | 0 | 1 | Χ | Χ | Χ | Χ | Χ | 1 | 0 | 1 | 1 | 0 | |

| 1 | 0 | 0 | 0 | 1 | Χ | Χ | Χ | Χ | 1 | 0 | 0 | 1 | 0 | |

| 1 | 0 | 0 | 0 | 0 | 1 | Χ | Χ | Χ | 0 | 1 | 1 | 1 | 0 | |

| 1 | 0 | 0 | 0 | 0 | 0 | 1 | Χ | Χ | 0 | 1 | 0 | 1 | 0 | |

| 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | Χ | 0 | 0 | 1 | 1 | 0 | |

| 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 1 | 0 | |

| 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 |

Όταν EI 1 = 0, το κομμάτι 1 είναι απενεργοποιημένο. Y 2 Y 1 Y 0 = = 000 , GS 1 = 0 , EO 1 = 0 . EI 0 = 0, το chip 0 είναι επίσης απενεργοποιημένο. Όταν EI_1=0, το κομμάτι 1 είναι απενεργοποιημένο. Y_2Y_1Y_0==000, GS_1=0, EO_1=0. EI_0=0, το slice 0 είναι επίσης απενεργοποιημένο.πότεμιΕγώ1=0ώρα, ταινία1Ατομα με ειδικές ανάγκες.Υ2Υ1Υ0==000,σολμικρό1=0,μιΟ1=0。μιΕγώ0=0,κομμάτι0Επίσης απενεργοποιημένο.

Όταν EI 1 = 1, η φέτα 1 επιτρέπεται να κωδικοποιηθεί Αν I 15 − I 8 = 000...000, τότε EO 1 = 1, άρα EI 0 = 1. Το Slice 0 επιτρέπει την κωδικοποίηση. Μπορεί να φανεί ότι η κωδικοποίηση του τεμαχίου 1 έχει μεγαλύτερη προτεραιότητα από την κωδικοποίηση του τμήματος 0. Όταν EI_1=1, επιτρέπεται η κωδικοποίηση του τμήματος 1 Εάν I_{15} - I_8 = 000...000, τότε EO_1= 1, άρα EI_0=1. Το Slice 0 επιτρέπει την κωδικοποίηση.Μπορεί να φανεί ότι η προτεραιότητα της κωδικοποίησης του τμήματος 1 είναι υψηλότερη από εκείνη της κωδικοποίησης του τμήματος 0.πότεμιΕγώ1=1ώρα, ταινία1Η κωδικοποίηση επιτρέπεται εάνΕγώ15−Εγώ8=000...000, αυτή τη στιγμήμιΟ1=1,εκ τούτουμιΕγώ0=1 .κομμάτι0 Επιτρέπεται η κωδικοποίηση.Μπορεί να φανεί ότι η ταινία1Η κωδικοποίηση έχει προτεραιότητα έναντι των τμημάτων0κωδικοποίηση。

Όταν EI 1 = 1, επιτρέπεται η κωδικοποίηση στο slice 1. Εάν το I 15 − I 8 έχει τουλάχιστον ένα 1, τότε EO 1 = 0, άρα EI 0 = 0, και η κωδικοποίηση απαγορεύεται στο slice 0. Όταν EI_1=1, επιτρέπεται η κωδικοποίηση στο slice 1. Εάν το I_{15} - I_8 έχει τουλάχιστον ένα 1, τότε EO_1=0, επομένως EI_0=0, η κωδικοποίηση απαγορεύεται στο slice 0.πότεμιΕγώ1=1ώρα, ταινία1Η κωδικοποίηση επιτρέπεται εάνΕγώ15−Εγώ8τουλάχιστον ένα1, αυτή τη στιγμήμιΟ1=0,εκ τούτουμιΕγώ0=0,κομμάτι0Η κωδικοποίηση απαγορεύεται.

| Το EI 1 επιτρέπει την κωδικοποίηση Το EI_1 επιτρέπει την κωδικοποίησημιΕγώ1Επιτρέπεται η κωδικοποίηση | Το EI 0 επιτρέπει την κωδικοποίηση Το EI_0 επιτρέπει την κωδικοποίησημιΕγώ0Επιτρέπεται η κωδικοποίηση | I 15 I_{15}Εγώ15 | I 14 I_{14}Εγώ14 | I 13 I_{13}Εγώ13 | I 12 I_{12}Εγώ12 | I 11 I_{11}Εγώ11 | I 10 I_{10}Εγώ10 | I 9 I_{9}Εγώ9 | I 8 I_8Εγώ8 | I 7 I_7Εγώ7 | I 6 I_6Εγώ6 | I 5 I_5Εγώ5 | I 4 I_4Εγώ4 | I 3 I_3Εγώ3 | I 2 I_2Εγώ2 | I 1 I_1Εγώ1 | I 0 I_0Εγώ0 | Υ 2 1 Υ2_1Υ21 | Υ 1 1 Υ1_1Υ11 | Y 0 1 Y0_1Υ01 | Υ 2 0 Υ2_0Υ20 | Υ 1 0 Υ1_0Υ10 | Y 0 0 Y0_0Υ00 | EO 1 Εισαγάγετε όλα τα 0 EO_1 Εισάγετε όλα τα 0μιΟ1Εισαγάγετε όλα0 | EO 0 Εισαγάγετε όλα τα 0 EO_0 Εισάγετε όλα τα 0μιΟ0Εισαγάγετε όλα0 | Το GS 1 έχει είσοδο 1 Το GS_1 έχει είσοδο 1σολμικρό1Υπάρχει είσοδος1 | Το GS 0 έχει είσοδο 0 Το GS_0 έχει είσοδο 0σολμικρό0Υπάρχει είσοδος0 | L 3 L_3μεγάλο3 | L 2 L_2μεγάλο2 | L 1 L_1μεγάλο1 | L 0 L_0μεγάλο0 | |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 0 (κομμάτι 1 απενεργοποιημένο) | EI 0 = EO 1 = 0 EI_0=EO_1=0μιΕγώ0=μιΟ1=0(απενεργοποιημένο στο κομμάτι 0) | Χ | Χ | Χ | Χ | Χ | Χ | Χ | Χ | Χ | Χ | Χ | Χ | Χ | Χ | Χ | Χ | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | |

| 1 | 0 | 1 | Χ | Χ | Χ | Χ | Χ | Χ | Χ | Χ | Χ | Χ | Χ | Χ | Χ | Χ | Χ | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 1 (το τσιπ 1 έχει είσοδο) | 0 | 1 L 3 = GS 1 L_3 =GS_1μεγάλο3=σολμικρό1 | 1 L 2 = Y 2 1 L_2 =Y2_1μεγάλο2=Υ21 | 1 L 1 = Y 1 1 L_1 =Y1_1μεγάλο1=Υ11 | 1 L 0 = Y 0 1 L_0 =Y0_1μεγάλο0=Υ01 | |

| 1 | 0 | 0 | 1 | Χ | Χ | Χ | Χ | Χ | Χ | Χ | Χ | Χ | Χ | Χ | Χ | Χ | Χ | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 1 | 1 | 1 | 0 | |

| 1 | 0 | 0 | 0 | 1 | Χ | Χ | Χ | Χ | Χ | Χ | Χ | Χ | Χ | Χ | Χ | Χ | Χ | 1 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 1 | 1 | 0 | 1 | |

| 1 | 0 | 0 | 0 | 0 | 1 | Χ | Χ | Χ | Χ | Χ | Χ | Χ | Χ | Χ | Χ | Χ | Χ | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 1 | 1 | 0 | 0 | |

| 1 | 0 | 0 | 0 | 0 | 0 | 1 | Χ | Χ | Χ | Χ | Χ | Χ | Χ | Χ | Χ | Χ | Χ | 0 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 1 | 0 | 1 | 1 | |

| 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | Χ | Χ | Χ | Χ | Χ | Χ | Χ | Χ | Χ | Χ | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | |

| 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | Χ | Χ | Χ | Χ | Χ | Χ | Χ | Χ | Χ | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 1 | 0 | 0 | 1 | |

| 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | Χ | Χ | Χ | Χ | Χ | Χ | Χ | Χ | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 1 | 0 | 0 | 0 | |

| 1 | EI 0 = EO 1 = 1 EI_0=EO_1=1μιΕγώ0=μιΟ1=1(τεμάχιο 0 έργο) | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | Χ | Χ | Χ | Χ | Χ | Χ | Χ | 0 | 0 | 0 | 1 | 1 | 1 | 1 (η είσοδος του τσιπ 1 είναι και 0) | 0 | 0 (Μη έγκυρη κωδικοποίηση για το τμήμα 1) | 1 | 0 L 3 = GS 1 L_3 =GS_1μεγάλο3=σολμικρό1 | 1 L 2 = Y 2 0 L_2 =Y2_0μεγάλο2=Υ20 | 1 L 1 = Y 1 0 L_1 =Y1_0μεγάλο1=Υ10 | 1 L 0 = Y 0 0 L_0 =Y0_0μεγάλο0=Υ00 | |

| 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | Χ | Χ | Χ | Χ | Χ | Χ | 0 | 0 | 0 | 1 | 1 | 0 | 1 | 0 | 0 | 1 | 0 | 1 | 1 | 0 | |

| 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | Χ | Χ | Χ | Χ | Χ | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 0 | 1 | 0 | 1 | 0 | 1 | |

| 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | Χ | Χ | Χ | Χ | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 0 | 1 | 0 | 1 | 0 | 0 | |

| 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | Χ | Χ | Χ | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 0 | 1 | 0 | 0 | 1 | 1 | |

| 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | Χ | Χ | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 0 | 1 | 0 | 0 | 1 | 0 | |

| 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | Χ | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 1 | |

| 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | |

| 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 (η είσοδος τσιπ 0 είναι όλη η 0) | 0 | 0 (τμήμα 0 μη έγκυρη κωδικοποίηση) | 0 | 0 | 0 | 0 |

| εισαγω | παραγωγή | |||||

| /ΜΙ | Α'1 | A_0 | /Y_3 | /Y_2 | /Y_1 | /Y_0 |

| 1 απαγορευμένο | Χ | Χ | 1 | 1 | 1 | 1 |

| 0 ενεργοποίηση | 0 | 0 | 1 | 1 | 1 | 0 χαμηλή ενεργή |

| 0 ενεργοποίηση | 0 | 1 | 1 | 1 | 0 χαμηλή αποτελεσματική | 1 |

| 0 ενεργοποίηση | 1 | 0 | 1 | 0 χαμηλή ενεργή | 1 | 1 |

| 0 ενεργοποίηση | 1 | 1 | 0 χαμηλή ενεργή | 1 | 1 | 1 |

Y 0 ‾ = E ‾ ‾ ⋅ A 1 ‾ ⋅ A 0 ‾ ‾ overline{Y_0} = overline{overline{overline{E}}·overline{A_1}·overline{A_0}}Υ0=μι⋅ΕΝΑ1⋅ΕΝΑ0 //00

Y 1 ‾ = E ‾ ‾ ⋅ A 1 ‾ ⋅ A 0 ‾ overline{Y_1} = overline{overline{overline{E}}·overline{A_1}·A_0}Υ1=μι⋅ΕΝΑ1⋅ΕΝΑ0 //01

Y 2 ‾ = E ‾ ‾ ⋅ A 1 ⋅ A 0 ‾ ‾ overline{Y_2} = overline{overline{overline{E}}·A_1·overline{A_0}}Υ2=μι⋅ΕΝΑ1⋅ΕΝΑ0 //10

Y 3 ‾ = E ‾ ‾ ⋅ A 1 ⋅ A 0 ‾ overline{Y_3} = overline{overline{overline{E}}·A_1·A_0}Υ3=μι⋅ΕΝΑ1⋅ΕΝΑ0 //11

Y 0 ‾ = E 3 ⋅ E 2 ‾ ‾ ⋅ E 1 ‾ ‾ ⋅ A 2 ‾ ⋅ A 1 ‾ ⋅ A 0 ‾ ‾ overline{Y_0} = overline{E_3·{_overline{2}overline E_1}}·overline{A_2}·overline{A_1}·overline{A_0}}Υ0=μι3⋅μι2⋅μι1⋅ΕΝΑ2⋅ΕΝΑ1⋅ΕΝΑ0 //000

Y 1 ‾ = E 3 ⋅ E 2 ‾ ‾ ⋅ E 1 ‾ ‾ ⋅ A 2 ‾ ⋅ A 1 ‾ ⋅ A 0 ‾ overline{Y_1} = overline{E_3·overline2}overline·{1] }}·overline{A_2}·overline{A_1}·A_0}Υ1=μι3⋅μι2⋅μι1⋅ΕΝΑ2⋅ΕΝΑ1⋅ΕΝΑ0 //001

Y 2 ‾ = E 3 ⋅ E 2 ‾ ‾ ⋅ E 1 ‾ ‾ ⋅ A 2 ‾ ⋅ A 1 ⋅ A 0 ‾ ‾ overline{Y_2} = overline{E_3·overline2}overline·{E_overline }}·overline{A_2}·A_1·overline{A_0}}Υ2=μι3⋅μι2⋅μι1⋅ΕΝΑ2⋅ΕΝΑ1⋅ΕΝΑ0 //010

Y 3 ‾ = E 3 ⋅ E 2 ‾ ‾ ⋅ E 1 ‾ ‾ ⋅ A 2 ‾ ⋅ A 1 ⋅ A 0 ‾ overline{Y_3} = overline{E_3·overline{overline{E_2} }·overline{A_2}·A_1·A_0}Υ3=μι3⋅μι2⋅μι1⋅ΕΝΑ2⋅ΕΝΑ1⋅ΕΝΑ0 //011

Y 4 ‾ = E 3 ⋅ E 2 ‾ ‾ ⋅ E 1 ‾ ‾ ⋅ A 2 ⋅ A 1 ‾ ⋅ A 0 ‾ ‾ overline{Y_4} = overline{E_3·overline2}overline·{1] overline }}·A_2·overline{A_1}·overline{A_0}}Υ4=μι3⋅μι2⋅μι1⋅ΕΝΑ2⋅ΕΝΑ1⋅ΕΝΑ0 //100

Y 5 ‾ = E 3 ⋅ E 2 ‾ ‾ ⋅ E 1 ‾ ‾ ⋅ A 2 ⋅ A 1 ‾ ⋅ A 0 ‾ overline{Y_5} = overline{E_3·overline{overline{E_1}{E_2} }·A_2·overline{A_1}·A_0}Υ5=μι3⋅μι2⋅μι1⋅ΕΝΑ2⋅ΕΝΑ1⋅ΕΝΑ0 //101

Y 6 ‾ = E 3 ⋅ E 2 ‾ ‾ ⋅ E 1 ‾ ‾ ⋅ A 2 ⋅ A 1 ⋅ A 0 ‾ ‾ overline{Y_6} = overline{E_3·overline{overline{E_2} }·A_2·A_1·overline{A_0}}Υ6=μι3⋅μι2⋅μι1⋅ΕΝΑ2⋅ΕΝΑ1⋅ΕΝΑ0 //110

Y 7 ‾ = E 3 ⋅ E 2 ‾ ‾ ⋅ E 1 ‾ ‾ ⋅ A 2 ⋅ A 1 ⋅ A 0 ‾ overline{Y_7} = overline{E_3·overline{overline{E_2}}·E_1}overline ·A_2·A_1·A_0}Υ7=μι3⋅μι2⋅μι1⋅ΕΝΑ2⋅ΕΝΑ1⋅ΕΝΑ0 //111

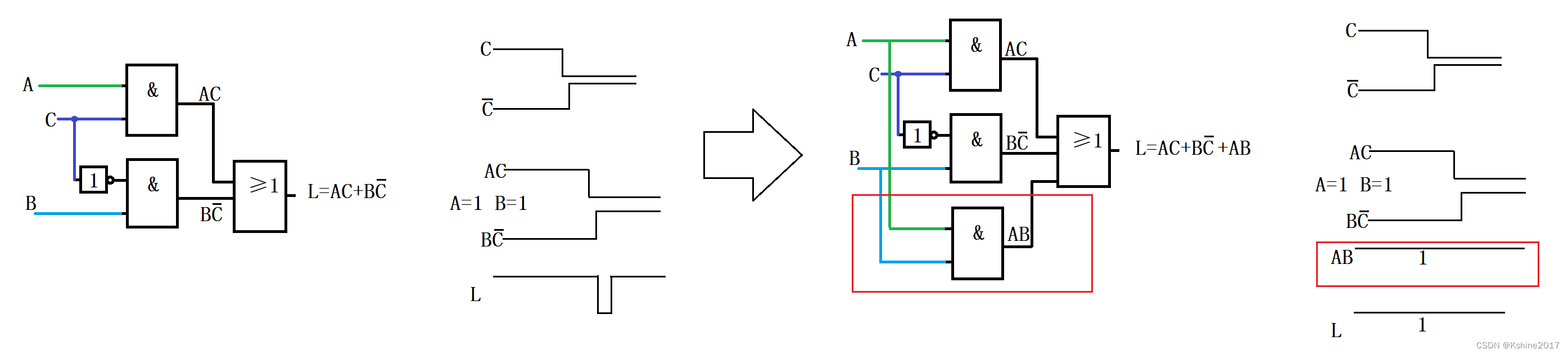

L = A ‾ ⋅ C ‾ + A ⋅ B = A ‾ ⋅ B ‾ ⋅ C ‾ + A ‾ ⋅ B ⋅ C ‾ + A ⋅ B ⋅ C ‾ + ABC = m 0 + m + m 2 + L =overline{A}·overline{C}+A·B =overline{A}·overline{B}·overline{C}+overline{A}·B·overline{C} + A·B·overline{C} +ABC = m_0+m_2+m_6+m_7μεγάλο=ΕΝΑ⋅ντο+ΕΝΑ⋅σι=ΕΝΑ⋅σι⋅ντο+ΕΝΑ⋅σι⋅ντο+ΕΝΑ⋅σι⋅ντο+ΕΝΑπρο ΧΡΙΣΤΟΥ=Μ0+Μ2+Μ6+Μ7

Y 0 ‾ = E 3 ⋅ E 2 ‾ ‾ ⋅ E 1 ‾ ‾ ⋅ A 2 ‾ ⋅ A 1 ‾ ⋅ A 0 ‾ ‾ = E 3 ⋅ E 2 ‾ ‾ overline{Y_0} = overline{E_3·overline{overline{E_2}}·overline{overline{E_1}}·overline{A_2}·overline{A_1}·overline{A_0}} = overline{E_3·overline{overline{E_2}}·overline {overline{E_1}}·m_0}Υ0=μι3⋅μι2⋅μι1⋅ΕΝΑ2⋅ΕΝΑ1⋅ΕΝΑ0=μι3⋅μι2⋅μι1⋅Μ0 //000

Y 1 ‾ = E 3 ⋅ E 2 ‾ ‾ ⋅ E 1 ‾ ‾ ⋅ A 2 ‾ ⋅ A 1 ‾ ⋅ A 0 ‾ = E 3 ⋅ E 2 ‾ ‾ ‾ ‾ ‾ _1} = overline{E_3·overline{overline{E_2}}·overline{overline{E_1}}·overline{A_2}·overline{A_1}·A_0} = overline{E_3·overline{overline{E_2}}·overline{overline{E_1 }}·m_1}Υ1=μι3⋅μι2⋅μι1⋅ΕΝΑ2⋅ΕΝΑ1⋅ΕΝΑ0=μι3⋅μι2⋅μι1⋅Μ1 //001

Y 2 ‾ = E 3 ⋅ E 2 ‾ ‾ ⋅ E 1 ‾ ‾ ⋅ A 2 ‾ ⋅ A 1 ⋅ A 0 ‾ ‾ = E 3 ⋅ E 2 ‾ ‾ ‾ ‾ _2} = overline{E_3·overline{overline{E_2}}·overline{overline{E_1}}·overline{A_2}·A_1·overline{A_0}}= overline{E_3·overline{overline{E_2}}·overline{overline{E_1 }}·m_2}Υ2=μι3⋅μι2⋅μι1⋅ΕΝΑ2⋅ΕΝΑ1⋅ΕΝΑ0=μι3⋅μι2⋅μι1⋅Μ2 //010

Y 3 ‾ = E 3 ⋅ E 2 ‾ ‾ ⋅ E 1 ‾ ‾ ⋅ A 2 ‾ ⋅ A 1 ⋅ A 0 ‾ = E 3 ⋅ E 2 ‾ ‾ ⋅ ‾ ‾ ⋅ ⋅ ‾ ‾ ‾ ⋅ υπεργραμμίστε {E_3·overline{overline{E_2}}·overline{overline{E_1}}·overline{A_2}·A_1·A_0}= overline{E_3·overline{overline{E_2}}·overline{overline{E_1}}·m_3 }Υ3=μι3⋅μι2⋅μι1⋅ΕΝΑ2⋅ΕΝΑ1⋅ΕΝΑ0=μι3⋅μι2⋅μι1⋅Μ3 //011

Y 4 ‾ = E 3 ⋅ E 2 ‾ ‾ ⋅ E 1 ‾ ‾ ⋅ A 2 ⋅ A 1 ‾ ⋅ A 0 ‾ ‾ = E 3 ⋅ E 2 ‾ ‾ ‾ ‾ ‾ _4} = overline{E_3·overline{overline{E_2}}·overline{overline{E_1}}·A_2·overline{A_1}·overline{A_0}}= overline{E_3·overline{overline{E_2}}·overline{overline{E_1 }}·m_4}Υ4=μι3⋅μι2⋅μι1⋅ΕΝΑ2⋅ΕΝΑ1⋅ΕΝΑ0=μι3⋅μι2⋅μι1⋅Μ4 //100

Y 5 ‾ = E 3 ⋅ E 2 ‾ ‾ ⋅ E 1 ‾ ‾ ⋅ A 2 ⋅ A 1 ‾ ⋅ A 0 ‾ = E 3 ⋅ E 2 ‾ ‾ ⋅ ⋅ ‾ ‾ ‾ ‾ ‾ ‾ ‾ ‾ ⋅ υπεργραμμίστε {E_3·overline{overline{E_2}}·overline{overline{E_1}}·A_2·overline{A_1}·A_0}= overline{E_3·overline{overline{E_2}}·overline{overline{E_1}}·m_5 }Υ5=μι3⋅μι2⋅μι1⋅ΕΝΑ2⋅ΕΝΑ1⋅ΕΝΑ0=μι3⋅μι2⋅μι1⋅Μ5 //101

Y 6 ‾ = E 3 ⋅ E 2 ‾ ‾ ⋅ E 1 ‾ ‾ ⋅ A 2 ⋅ A 1 ⋅ A 0 ‾ ‾ = E 3 ⋅ E 2 ‾ ‾ ⋅ ‾ ‾ ⋅ ⋅ ‾ ‾ ‾ ‾ ‾ ⋅ υπεργραμμίστε {E_3·overline{overline{E_2}}·overline{overline{E_1}}·A_2·A_1·overline{A_0}}= overline{E_3·overline{overline{E_2}}·overline{overline{E_1}}·m_6 }Υ6=μι3⋅μι2⋅μι1⋅ΕΝΑ2⋅ΕΝΑ1⋅ΕΝΑ0=μι3⋅μι2⋅μι1⋅Μ6 //110

Y 7 ‾ = E 3 ⋅ E 2 ‾ ‾ ⋅ E 1 ‾ ‾ ⋅ A 2 ⋅ A 1 ⋅ A 0 ‾ = E 3 ⋅ E 2 ‾ ‾ ⋅ E 1 ‾ ‾ πάνω από γραμμή m E_3·overline{overline{E_2}}·overline{overline{E_1}}·A_2·A_1·A_0}= overline{E_3·overline{overline{E_2}}·overline{overline{E_1}}·m_7}Υ7=μι3⋅μι2⋅μι1⋅ΕΝΑ2⋅ΕΝΑ1⋅ΕΝΑ0=μι3⋅μι2⋅μι1⋅Μ7 //111

Βεβαιωθείτε ότι E 3 = 1 , E 2 = 0 , E 1 = 0 Βεβαιωθείτε ότι E_3=1,E_2=0,E_1=0συγουρεύομαιμι3=1,μι2=0,μι1=0, δηλαδή Y 0 ‾ = m 0 ‾ , Y 2 ‾ = m 2 ‾ , Y 6 ‾ = m 6 ‾ , Y 7 ‾ = m 7 ‾ overline{Y_0}=overline{m_0},overline{Y_2} ,overline{Y_6}=overline{m_6},overline{Y_7}=overline{m_7}Υ0=Μ0,Υ2=Μ2,Υ6=Μ6,Υ7=Μ7。

Μετασχηματίστε λογικές συναρτήσεις σύμφωνα με το νόμο της αντιστροφής

L = L ‾ ‾ = m 0 + m 2 + m 6 + m 7 ‾ ‾ = m 0 ‾ ⋅ m 2 ‾ ⋅ m 6 ‾ ⋅ m 7 ‾ ‾ = m 0 + m 2 + m 6 + m 7 = Y 0 ‾ ⋅ Y 2 ‾ ⋅ Y 6 ‾ ⋅ Y 7 ‾ ‾ L=overline{overline{L}} = overline{overline{m_0+m_2+m_6+m_7}} = overline{overline{m_0}·overline{ m_2}·overline{m_6}·overline{m_7}} = overline{overline{m_0+m_2+m_6+m_7}} = overline{overline{Y_0}·overline{Y_2}·overline{Y_6}·overline{Y_7}}μεγάλο=μεγάλο=Μ0+Μ2+Μ6+Μ7=Μ0⋅Μ2⋅Μ6⋅Μ7=Μ0+Μ2+Μ6+Μ7=Υ0⋅Υ2⋅Υ6⋅Υ7

Λήψη λογικού διαγράμματος

774HC42

4 είσοδοι

10 ακροδέκτες εξόδου, η έξοδος είναι ενεργή σε χαμηλό επίπεδο, που αντιστοιχεί σε δεκαδικούς αριθμούς 0~9.

4 ακροδέκτες εισόδου, συνολικά 16 καταστάσεις

μόνο m 0 , m 1 , m 2 . . . . . . m 9 m_0 ,m_1,m_2......m_9Μ0,Μ1,Μ2......Μ9Είναι μια έγκυρη είσοδος (η αντίστοιχη ακίδα εξόδου βγάζει χαμηλή τιμή 0 και οι άλλες έξοδοι είναι υψηλή 1).

Ανάμεσα στα υπόλοιπα 6 m 10 , m 11 , m 12 . . . . . . m 15 m_{10} ,m_{11},m_{12}......m_{15}Μ10,Μ11,Μ12......Μ15Σημαίνει ότι δεν υπάρχει έγκυρη έξοδος αποκωδικοποίησης (όταν δεν είναι έγκυρη, η έξοδος είναι όλα υψηλή 1).

Σχεδιάστε τα διαγράμματα κυματομορφής εισόδου και εξόδου του 74HC42.

Αρχή απεικόνισης ψηφιακού σωλήνα

Ενσωματωμένος αποκωδικοποιητής οθόνης επτά τμημάτων. 74HC4511 (κοινή κάθοδος) (υψηλού επιπέδου ανάβει)

ΛΕ ΛΕμεγάλομιΕνεργοποίηση κλειδώματος

LT ‾ overline{LT}μεγάλοΤείσοδος δοκιμής λαμπτήρα όταν LT ‾ = 0 overline{LT}=0μεγάλοΤ=0Όταν , το ag βγάζει όλα τα 1 και εμφανίζει τη γραμματοσειρά "8".

BL ‾ overline{BL}σιμεγάλοΕίσοδος σβησίματος φωτός, όταν LT ‾ = 1, και BL ‾ = 1 overline{LT}=1, και overline{BL}=1μεγάλοΤ=1,καισιμεγάλο=1 Όταν , ag όλες οι έξοδοι 0. Μπορεί να χρησιμοποιηθεί για να σβήσει το μη απαραίτητο εμφανιζόμενο μηδέν "0".

D 3 D 2 D 1 D 0 D_3D_2D_1D_0ρε3ρε2ρε1ρε0=0000, η αντίστοιχη γλυφή εξόδου "0"

D 3 D 2 D 1 D 0 D_3D_2D_1D_0ρε3ρε2ρε1ρε0=0001, η αντίστοιχη γραμματοσειρά εξόδου "1"

D 3 D 2 D 1 D 0 D_3D_2D_1D_0ρε3ρε2ρε1ρε0=0010, η αντίστοιχη γραμματοσειρά εξόδου "2"

D 3 D 2 D 1 D 0 D_3D_2D_1D_0ρε3ρε2ρε1ρε0=0011, η αντίστοιχη γραμματοσειρά εξόδου "3"

D 3 D 2 D 1 D 0 D_3D_2D_1D_0ρε3ρε2ρε1ρε0=0100, η αντίστοιχη γραμματοσειρά εξόδου "4"

D 3 D 2 D 1 D 0 D_3D_2D_1D_0ρε3ρε2ρε1ρε0=0101, η αντίστοιχη γραμματοσειρά εξόδου "5"

D 3 D 2 D 1 D 0 D_3D_2D_1D_0ρε3ρε2ρε1ρε0=0110, η αντίστοιχη γραμματοσειρά εξόδου "6"

D 3 D 2 D 1 D 0 D_3D_2D_1D_0ρε3ρε2ρε1ρε0=0111, η αντίστοιχη γραμματοσειρά εξόδου "7"

D 3 D 2 D 1 D 0 D_3D_2D_1D_0ρε3ρε2ρε1ρε0=1000, η αντίστοιχη γραμματοσειρά εξόδου "8"

D 3 D 2 D 1 D 0 D_3D_2D_1D_0ρε3ρε2ρε1ρε0=1001, η αντίστοιχη γραμματοσειρά εξόδου "9"

1010-1111, εκτός

Από ένα σε πολλά, τα δεδομένα στην κοινή γραμμή δεδομένων αποστέλλονται σε διαφορετικά κανάλια ανάλογα με τις ανάγκες.

Παρόμοιο με τον "μονοπολικό διακόπτη πολλαπλών ρίψεων"

Χρησιμοποιώντας έναν μοναδικό αποκωδικοποιητή διευθύνσεων, εφαρμόστε τον εκχωρητή δεδομένων

Για παράδειγμα, το 74x138 ενσωματώνει έναν αποκωδικοποιητή 3 γραμμών έως 8 γραμμών.

E 1 ‾ ως εισαγωγή δεδομένων overline{E_1} ως εισαγωγή δεδομένωνμι1ως εισαγωγή δεδομένων

Y 0 Y 1 Y 2 Y 3 Y 4 Y 5 Y 6 Y 7 Y_0 Y_1 Y_2Y_3Y_4Y_5Y_6Y_7Υ0Υ1Υ2Υ3Υ4Υ5Υ6Υ78 κανάλια ως έξοδος δεδομένων

Y 2 ‾ = E 3 ⋅ E 2 ‾ ‾ ⋅ E 1 ‾ ‾ ⋅ A 2 ‾ ⋅ A 1 ⋅ A 0 ‾ ‾ overline{Y_2} = overline{E_3·overline2}overline·{E_overline }}·overline{A_2}·A_1·overline{A_0}}Υ2=μι3⋅μι2⋅μι1⋅ΕΝΑ2⋅ΕΝΑ1⋅ΕΝΑ0 //010

Στην παραπάνω φωτογραφία, E 3 = 1 , E 2 ‾ = 0 E_3=1,overline{E_2}=0μι3=1,μι2=0, όταν η γραμμή διεύθυνσης A 2 A 1 A 0 = 010 A_2A_1A_0=010ΕΝΑ2ΕΝΑ1ΕΝΑ0=010ώρα, Y 2 ‾ = E 1 ‾ overline{Y_2}=overline{E_1}Υ2=μι1

Με την ίδια λογική μπορούμε να συμπεράνουμε:

Όταν η γραμμή διεύθυνσης A 2 A 1 A 0 = 000 A_2A_1A_0=000ΕΝΑ2ΕΝΑ1ΕΝΑ0=000ώρα, Y 0 ‾ = E 1 ‾ = D overline{Y_0}=overline{E_1}=DΥ0=μι1=ρε,άλλα Y x = 1 Y_x=1ΥΧ=1。

Όταν η γραμμή διεύθυνσης A 2 A 1 A 0 = 001 A_2A_1A_0=001ΕΝΑ2ΕΝΑ1ΕΝΑ0=001ώρα, Y 1 ‾ = E 1 ‾ = D overline{Y_1}=overline{E_1}=DΥ1=μι1=ρε,άλλα Y x = 1 Y_x=1ΥΧ=1。

Όταν η γραμμή διεύθυνσης A 2 A 1 A 0 = 010 A_2A_1A_0=010ΕΝΑ2ΕΝΑ1ΕΝΑ0=010ώρα, Y 2 ‾ = E 1 ‾ = D overline{Y_2}=overline{E_1}=DΥ2=μι1=ρε,άλλα Y x = 1 Y_x=1ΥΧ=1。

Όταν η γραμμή διεύθυνσης A 2 A 1 A 0 = 011 A_2A_1A_0=011ΕΝΑ2ΕΝΑ1ΕΝΑ0=011ώρα, Y 3 ‾ = E 1 ‾ = D overline{Y_3}=overline{E_1}=DΥ3=μι1=ρε,άλλα Y x = 1 Y_x=1ΥΧ=1。

Όταν η γραμμή διεύθυνσης A 2 A 1 A 0 = 100 A_2A_1A_0=100ΕΝΑ2ΕΝΑ1ΕΝΑ0=100ώρα, Y 4 ‾ = E 1 ‾ = D overline{Y_4}=overline{E_1}=DΥ4=μι1=ρε,άλλα Y x = 1 Y_x=1ΥΧ=1。

Όταν η γραμμή διεύθυνσης A 2 A 1 A 0 = 101 A_2A_1A_0=101ΕΝΑ2ΕΝΑ1ΕΝΑ0=101ώρα, Y 5 ‾ = E 1 ‾ = D overline{Y_5}=overline{E_1}=DΥ5=μι1=ρε,άλλα Y x = 1 Y_x=1ΥΧ=1。

Όταν η γραμμή διεύθυνσης A 2 A 1 A 0 = 110 A_2A_1A_0=110ΕΝΑ2ΕΝΑ1ΕΝΑ0=110ώρα, Y 6 ‾ = E 1 ‾ = D overline{Y_6}=overline{E_1}=DΥ6=μι1=ρε,άλλα Y x = 1 Y_x=1ΥΧ=1。

Όταν η γραμμή διεύθυνσης A 2 A 1 A 0 = 111 A_2A_1A_0=111ΕΝΑ2ΕΝΑ1ΕΝΑ0=111ώρα, Y 7 ‾ = E 1 ‾ = D overline{Y_7}=overline{E_1}=DΥ7=μι1=ρε,άλλα Y x = 1 Y_x=1ΥΧ=1。

Y = S 2 ‾ ⋅ S 1 ‾ ⋅ S 0 ‾ ⋅ D 0 + S 2 ‾ ⋅ S 1 ‾ ⋅ S 0 ⋅ D 1 + S 2 ‾ ⋅ S 1 ⋅ S ⋅ S ‾ ‾ 1 ⋅ S 0 ⋅ D 3 + S 2 ⋅ S 1 ‾ ⋅ S 0 ‾ ⋅ D 4 + S 2 ⋅ S 1 ‾ ⋅ S 0 ⋅ D 5 + S 2 ⋅ S 1 ⋅ S ⋅ S ⋅ 0 ⋅ S 1 ⋅ S 0 ⋅ D 7 Y=overline{S_2}·overline{S_1}·overline{S_0}·D_0 +overline{S_2}·overline{S_1}·S_0·D_1 +overline{S_2}·S_1·overline {S_0}·D_2 +overline{S_2}·S_1·S_0·D_3 +S_2·overline{S_1}·overline{S_0}·D_4 +S_2·overline{S_1}·S_0·D_5 +S_2·S_1·overline{S_0} ·D_6 +S_2·S_1·S_0·D_7Υ=μικρό2⋅μικρό1⋅μικρό0⋅ρε0+μικρό2⋅μικρό1⋅μικρό0⋅ρε1+μικρό2⋅μικρό1⋅μικρό0⋅ρε2+μικρό2⋅μικρό1⋅μικρό0⋅ρε3+μικρό2⋅μικρό1⋅μικρό0⋅ρε4+μικρό2⋅μικρό1⋅μικρό0⋅ρε5+μικρό2⋅μικρό1⋅μικρό0⋅ρε6+μικρό2⋅μικρό1⋅μικρό0⋅ρε7

Επεκτάσεις για επιλογείς δεδομένων.

γεννήτρια λογικής συνάρτησης

Γνωστός επιλογέας δεδομένων 8-προς-1.

Y = S 2 ‾ ⋅ S 1 ‾ ⋅ S 0 ‾ ⋅ D 0 + S 2 ‾ ⋅ S 1 ‾ ⋅ S 0 ⋅ D 1 + S 2 ‾ ⋅ S 1 ⋅ S ⋅ S ‾ ‾ 1 ⋅ S 0 ⋅ D 3 + S 2 ⋅ S 1 ‾ ⋅ S 0 ‾ ⋅ D 4 + S 2 ⋅ S 1 ‾ ⋅ S 0 ⋅ D 5 + S 2 ⋅ S 1 ⋅ S ⋅ S ⋅ 0 ⋅ S 1 ⋅ S 0 ⋅ D 7 Y=overline{S_2}·overline{S_1}·overline{S_0}·D_0 +overline{S_2}·overline{S_1}·S_0·D_1 +overline{S_2}·S_1·overline {S_0}·D_2 +overline{S_2}·S_1·S_0·D_3 +S_2·overline{S_1}·overline{S_0}·D_4 +S_2·overline{S_1}·S_0·D_5 +S_2·S_1·overline{S_0} ·D_6 +S_2·S_1·S_0·D_7Υ=μικρό2⋅μικρό1⋅μικρό0⋅ρε0+μικρό2⋅μικρό1⋅μικρό0⋅ρε1+μικρό2⋅μικρό1⋅μικρό0⋅ρε2+μικρό2⋅μικρό1⋅μικρό0⋅ρε3+μικρό2⋅μικρό1⋅μικρό0⋅ρε4+μικρό2⋅μικρό1⋅μικρό0⋅ρε5+μικρό2⋅μικρό1⋅μικρό0⋅ρε6+μικρό2⋅μικρό1⋅μικρό0⋅ρε7

Y = m 0 ⋅ D 0 + m 1 ⋅ D 1 + m 2 ⋅ D 2 + m 3 ⋅ D 3 + m 4 ⋅ D 4 + m 5 ⋅ D 5 + m 6 ⋅ D 6 + m 7 ⋅ D 7 Y =m_0·D_0 +m_1·D_1 +m_2·D_2 +m_3·D_3 +m_4·D_4 +m_5·D_5 +m_6·D_6 +m_7·D_7Υ=Μ0⋅ρε0+Μ1⋅ρε1+Μ2⋅ρε2+Μ3⋅ρε3+Μ4⋅ρε4+Μ5⋅ρε5+Μ6⋅ρε6+Μ7⋅ρε7

λογική λειτουργία L = A ‾ BC + AB ‾ C + ABL=overline{A}BC+Aoverline{B}C+ABμεγάλο=ΕΝΑπρο ΧΡΙΣΤΟΥ+ΕΝΑσιντο+ΕΝΑσι

L = A ‾ BC + AB ‾ C + AB = A ‾ BC + AB ‾ C + ABC ‾ + ABC = m 3 + m 5 + m 6 + m 7 L=overline{A}BC+Aoverline{B}C+ AB=overline{A}BC+Aoverline{B}C+ABoverline{C}+ABC=m_3+m_5+m_6+m_7μεγάλο=ΕΝΑπρο ΧΡΙΣΤΟΥ+ΕΝΑσιντο+ΕΝΑσι=ΕΝΑπρο ΧΡΙΣΤΟΥ+ΕΝΑσιντο+ΕΝΑσιντο+ΕΝΑπρο ΧΡΙΣΤΟΥ=Μ3+Μ5+Μ6+Μ7

Χρησιμοποιήστε τον επιλογέα δεδομένων 8-προς-1 για να εφαρμόσετε την παραπάνω λειτουργία L

L = Y = m 3 + m 5 + m 6 + m 7, όπου D 7 D 6 D 5 D 3 = 1111, D 4 D 2 D 1 D 0 = 0000 L=Y=m_3+m_5+m_6+m_7, Μεταξύ αυτών D_7D_6D_5D_3=1111, D_4D_2D_1D_0=0000μεγάλο=Υ=Μ3+Μ5+Μ6+Μ7,σερε7ρε6ρε5ρε3=1111,ρε4ρε2ρε1ρε0=0000

Παράλληλα δεδομένα με σειριακά δεδομένα

| ΕΝΑ | σι | FA > B F_{A>B}φάΕΝΑ>σι | FA < B F_{AφάΕΝΑ<σι | FA = = B F_{A==B}φάΕΝΑ==σι |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 1 |

| 0 | 1 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 0 |

| 1 | 1 | 0 | 0 | 1 |

| A 1; B 1 A _1; B_1ΕΝΑ1?σι1 | Α 0 ? B 0 A_0?B_0ΕΝΑ0?σι0 | FA > B F_{A>B}φάΕΝΑ>σι | FA < B F_{AφάΕΝΑ<σι | FA = = B F_{A==B}φάΕΝΑ==σι |

|---|---|---|---|---|

| A 1 > B 1 A_1>B_1ΕΝΑ1>σι1 | Χ | 1 | 0 | 0 |

| A 1 < B 1 A_1ΕΝΑ1<σι1 | Χ | 0 | 1 | 0 |

| A 1 = = B 1 A_1==B_1ΕΝΑ1==σι1 | A 0 > B 0 A_0>B_0ΕΝΑ0>σι0 | 1 | 0 | 0 |

| A 1 = = B 1 A_1==B_1ΕΝΑ1==σι1 | A 0 < B 0 A_0ΕΝΑ0<σι0 | 0 | 1 | 0 |

| A 1 = = B 1 A_1==B_1ΕΝΑ1==σι1 | A 0 = = B 0 A_0==B_0ΕΝΑ0==σι0 | 0 | 0 | 1 |

λογική έκφραση

FA > B = FA 1 > B 1 + FA 1 = = B 1 ⋅ FA 0 > B 0 F_{A>B} = F_{A_1>B_1} +F_{A_1==B_1}·F_{A_0>B_0}φάΕΝΑ>σι=φάΕΝΑ1>σι1+φάΕΝΑ1==σι1⋅φάΕΝΑ0>σι0

FA < B = FA 1 < B 1 + FA 1 = = B 1 ⋅ FA 0 < B 0 F_{AφάΕΝΑ<σι=φάΕΝΑ1<σι1+φάΕΝΑ1==σι1⋅φάΕΝΑ0<σι0

FA = = B = FA 1 = = B 1 ⋅ FA 0 = = B 0 F_{A==B} = F_{A_1==B_1}·F_{A_0==B_0}φάΕΝΑ==σι=φάΕΝΑ1==σι1⋅φάΕΝΑ0==σι0

λογικό διάγραμμα

Σύνδεση σειράς, επεκτάθηκε σε αριθμητική σύγκριση 8-bit

Παράλληλη σύνδεση, επεκτάθηκε σε αριθμητική σύγκριση 16-bit.

Όταν συνδέεται παράλληλα, η ταχύτητα είναι γρήγορη.