моя контактная информация

Почтамезофия@protonmail.com

2024-07-12

한어Русский языкEnglishFrançaisIndonesianSanskrit日本語DeutschPortuguêsΕλληνικάespañolItalianoSuomalainenLatina

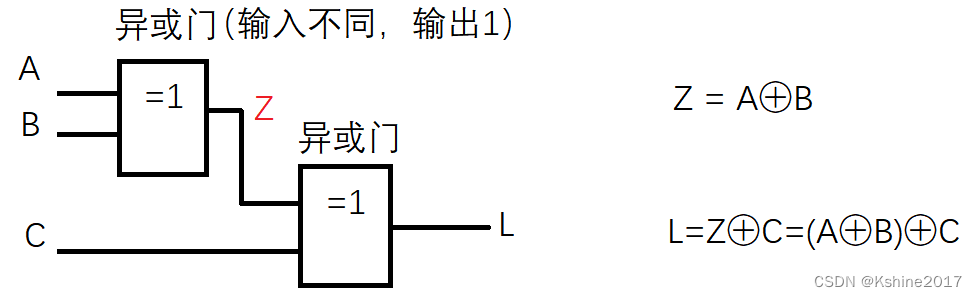

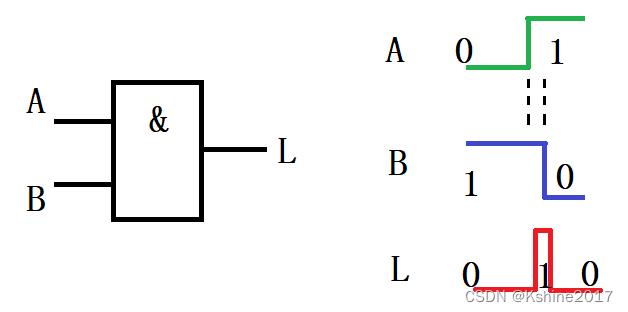

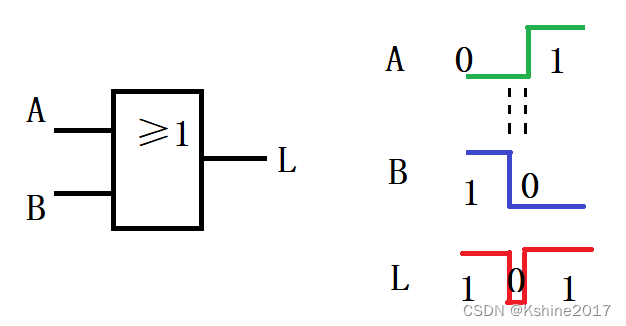

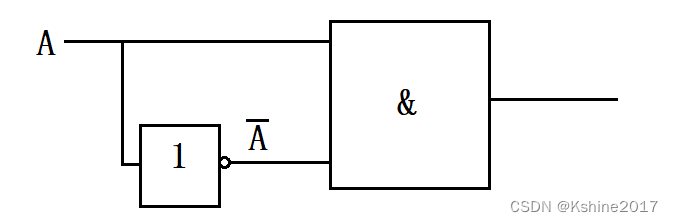

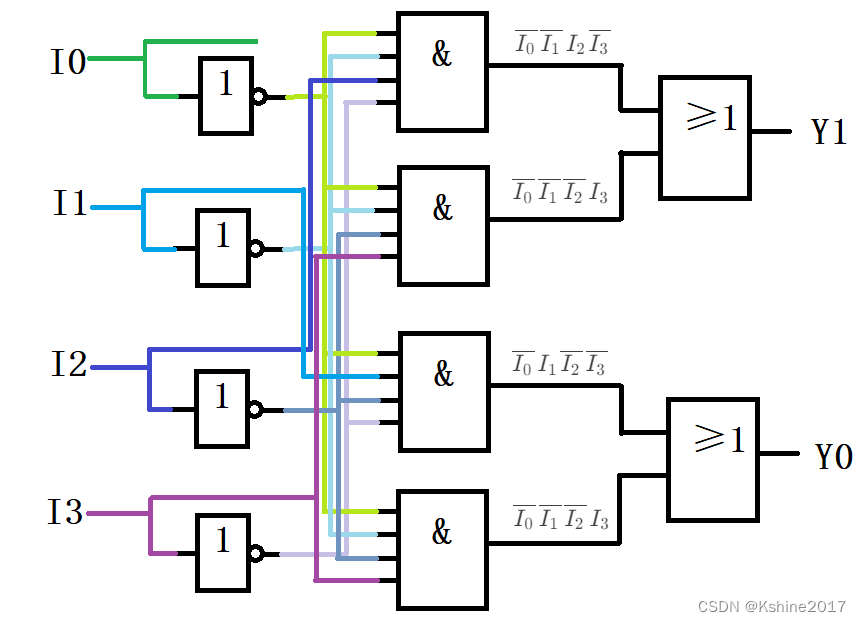

(1) Как показано на рисунке ниже.

(2) Перечислите таблицу истинности

| А | Б | С | З | Л |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 | 1 |

| 0 | 1 | 0 | 1 | 1 |

| 0 | 1 | 1 | 1 | 0 |

| 1 | 0 | 0 | 1 | 1 |

| 1 | 0 | 1 | 1 | 0 |

| 1 | 1 | 0 | 0 | 0 |

| 1 | 1 | 1 | 0 | 1 |

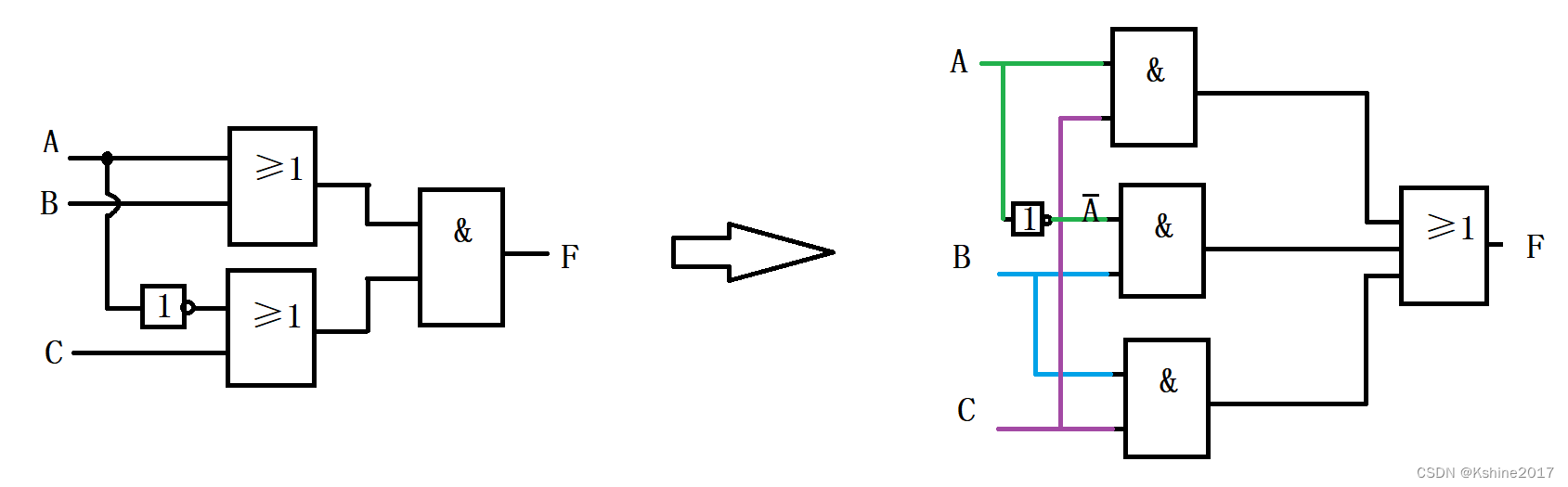

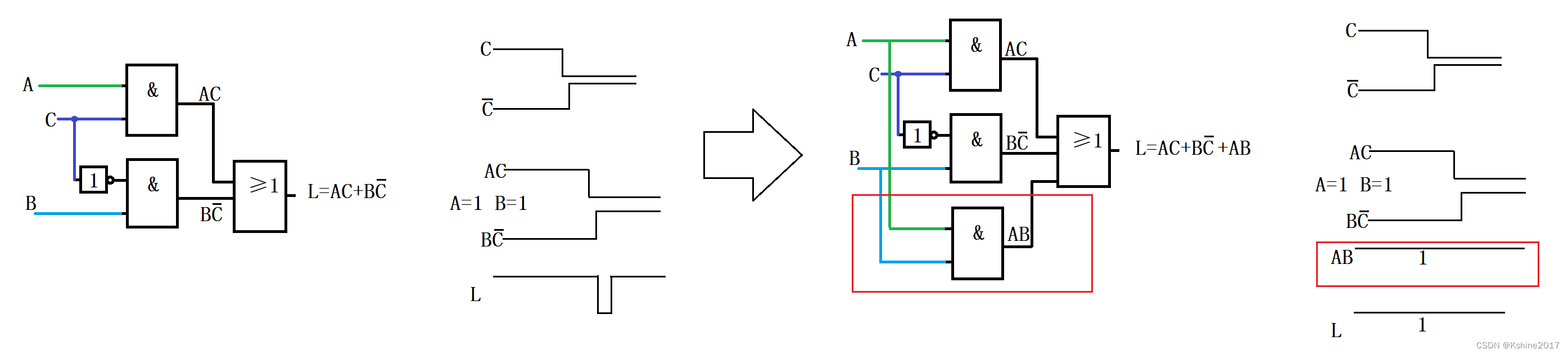

(3) ПроанализируйтеСхема нечетной четностиФункция.

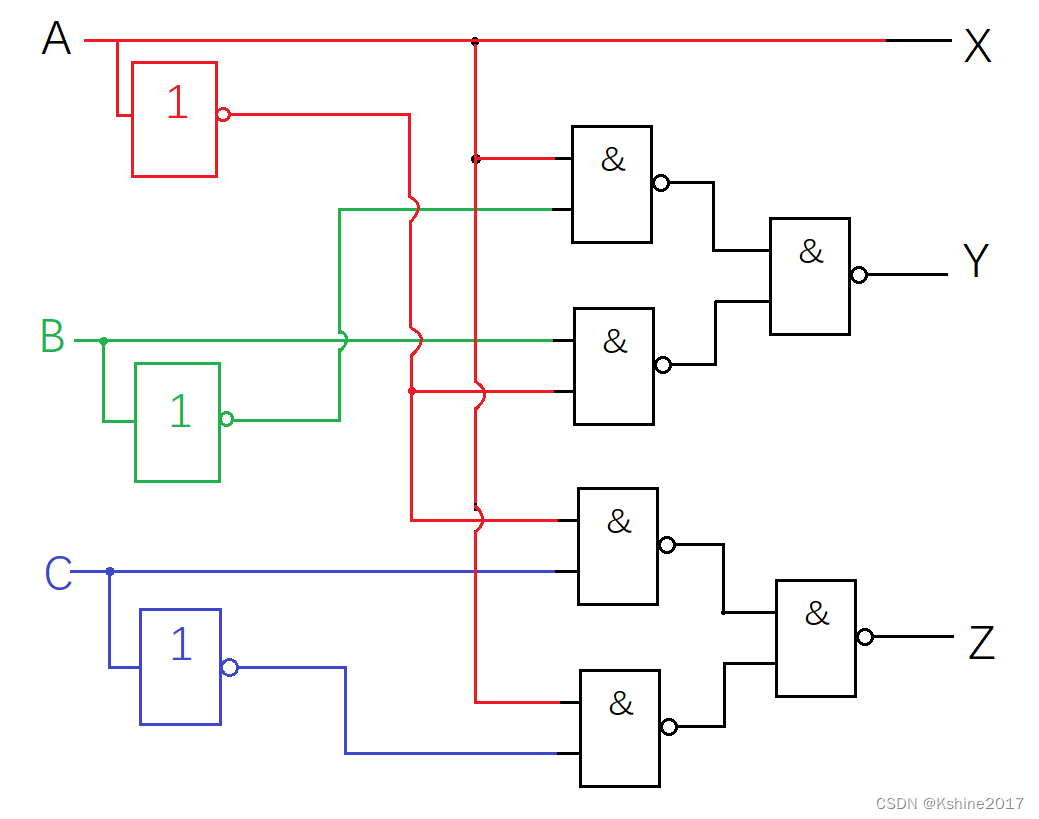

(1) На основе схемы нечетной четности, добавив инвертор на выходной конец, мы можем получитьСхема четности。

| А | Б | С | Икс | И | З |

|---|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 | 0 | 1 |

| 0 | 1 | 0 | 0 | 1 | 0 |

| 0 | 1 | 1 | 0 | 1 | 1 |

| 1 | 0 | 0 | 1 | 1 | 1 |

| 1 | 0 | 1 | 1 | 1 | 0 |

| 1 | 1 | 0 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 | 0 | 0 |

нуждаться.

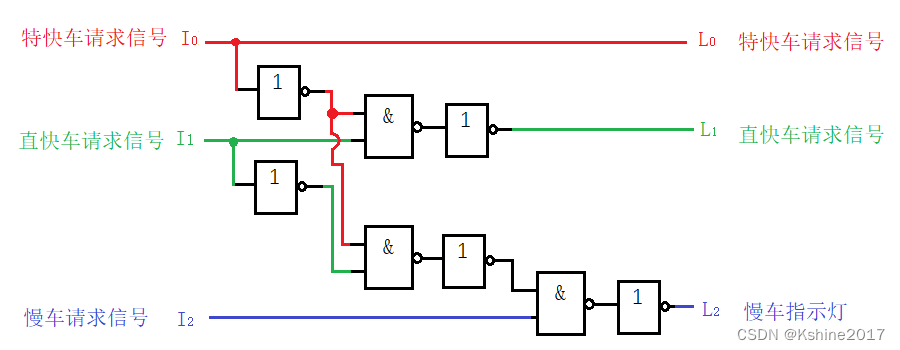

(1) Используйте 2 входаИ-НЕ-ворота, инвертор.

(2) Индикатор № 1, индикатор прибытия экспресс-поезда. Высокий приоритет.

(3) Индикатор № 2, прямой экспресс въезжает в индикатор станции. В приоритете.

(4) Индикатор № 3, медленный поезд входит в индикатор станции. Низкий приоритет.

(5) Одновременно может гореть не более одного индикатора.

Определите входные и выходные переменные.

(1) Входной сигнал, I 0 экспресс-запрос, I 1 прямой экспресс-запрос, I 2 запрос на пригородный поезд I_0 экспресс-запрос, I_1 прямой экспресс-запрос, I_2 запрос на пригородный поездя0экспресс-запрос,я1Просто запросите это быстро,я2Запрос на медленный поезд . 1 означает, что входящий запрос есть, 0 означает, что входящий запрос отсутствует.

(2) Выходной сигнал, L 0 индикатор экспресс-остановки, L 1 индикатор прямой экспресс-остановки, L 2 индикатор остановки пригородного поезда L_0 индикатор экспресс-остановки, L_1 индикатор прямой быстрой остановки, L_2 индикатор остановки пригородного поездаЛ0Свет экспресс-прибытия,Л1Индикатор прямой остановки,Л2Индикатор медленного прибытия поезда . 1 означает, что свет включен, 0 означает, что свет выключен.

Таблица истинности.

| входить | выход | ||||

| Я_0 | Я_1 | Я_2 | Л_0 | Л_1 | Л_2 |

| 0 | 0 | 0 | 0 | 0 | 0 |

| 1 | Икс | Икс | 1 | 0 | 0 |

| 0 | 1 | Икс | 0 | 1 | 0 |

| 0 | 0 | 1 | 0 | 0 | 1 |

Перечислить логические выражения

Л 0 = Я 0 Л_0 = Я_0Л0=я0

L 1 = I 0 ‾ ⋅ I 1 L_1 = надстрочный{I_0}·I_1Л1=я0⋅я1

L 2 = I 0 ‾ ⋅ I 1 ‾ ⋅ I 2 L_2 = надстрочный{I_0}·надстрочный{I_1}·I_2Л2=я0⋅я1⋅я2

При необходимости преобразуйте в форму NAND.

Л 0 = Я 0 Л_0 = Я_0Л0=я0

L 1 = I 0 ‾ ⋅ I 1 ‾ ‾ L_1 = overline{overline{overline{I_0}·I_1}}Л1=я0⋅я1

Л 2 = Я 0 ‾ ⋅ Я 1 ‾ ‾ ‾ ⋅ Я 2 ‾ ‾ Л_2 =overline{overline{overline{overline{overline{I_0}·overline{I_1}}}·I_2}}Л2=я0⋅я1⋅я2

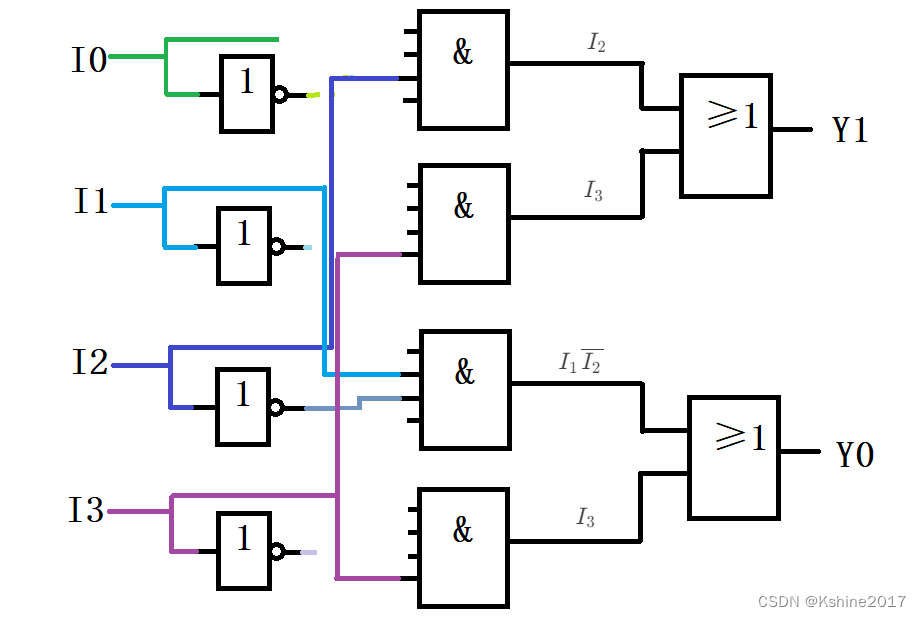

Нарисуйте логическую схему.

(1) Микросхема 74HC00 содержит четыре двухвходовых вентиля CMOS NAND.

(2) Микросхема 74HC04 содержит 6 инверторов CMOS.

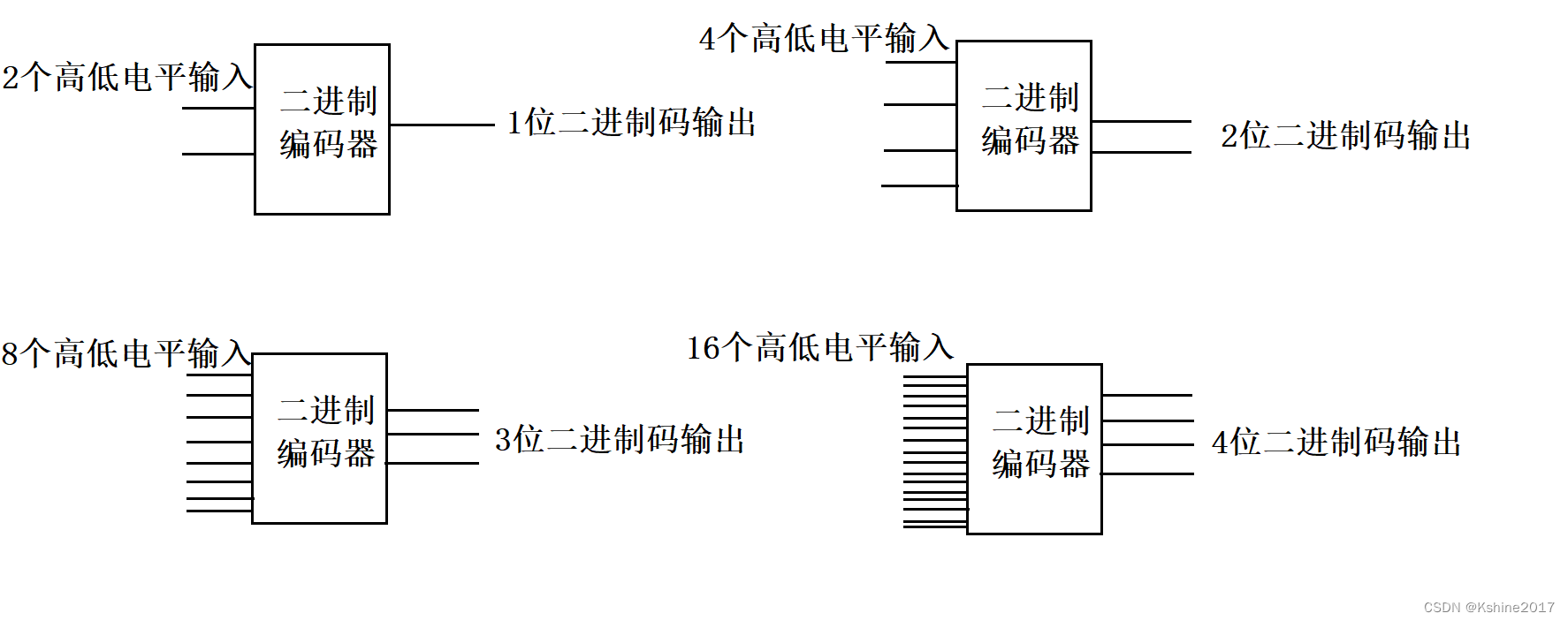

нуждаться.

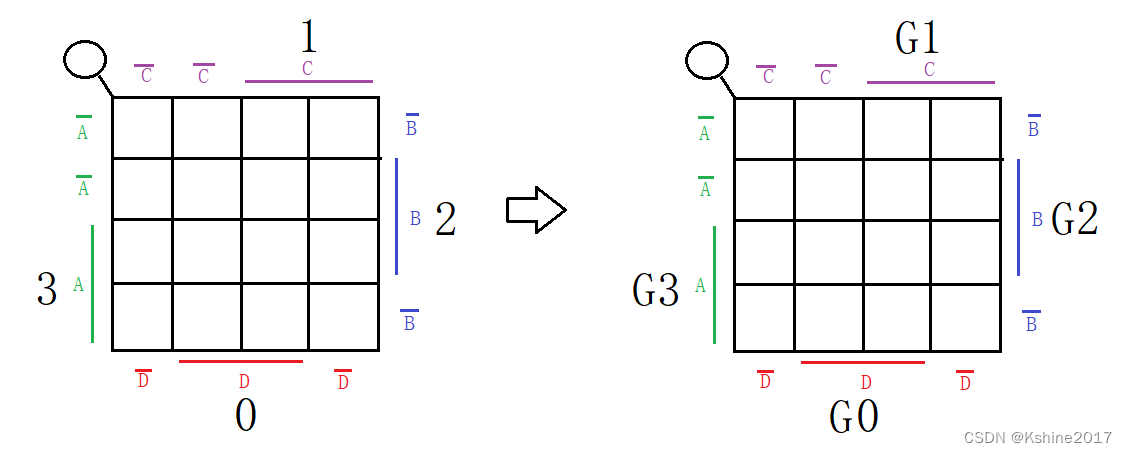

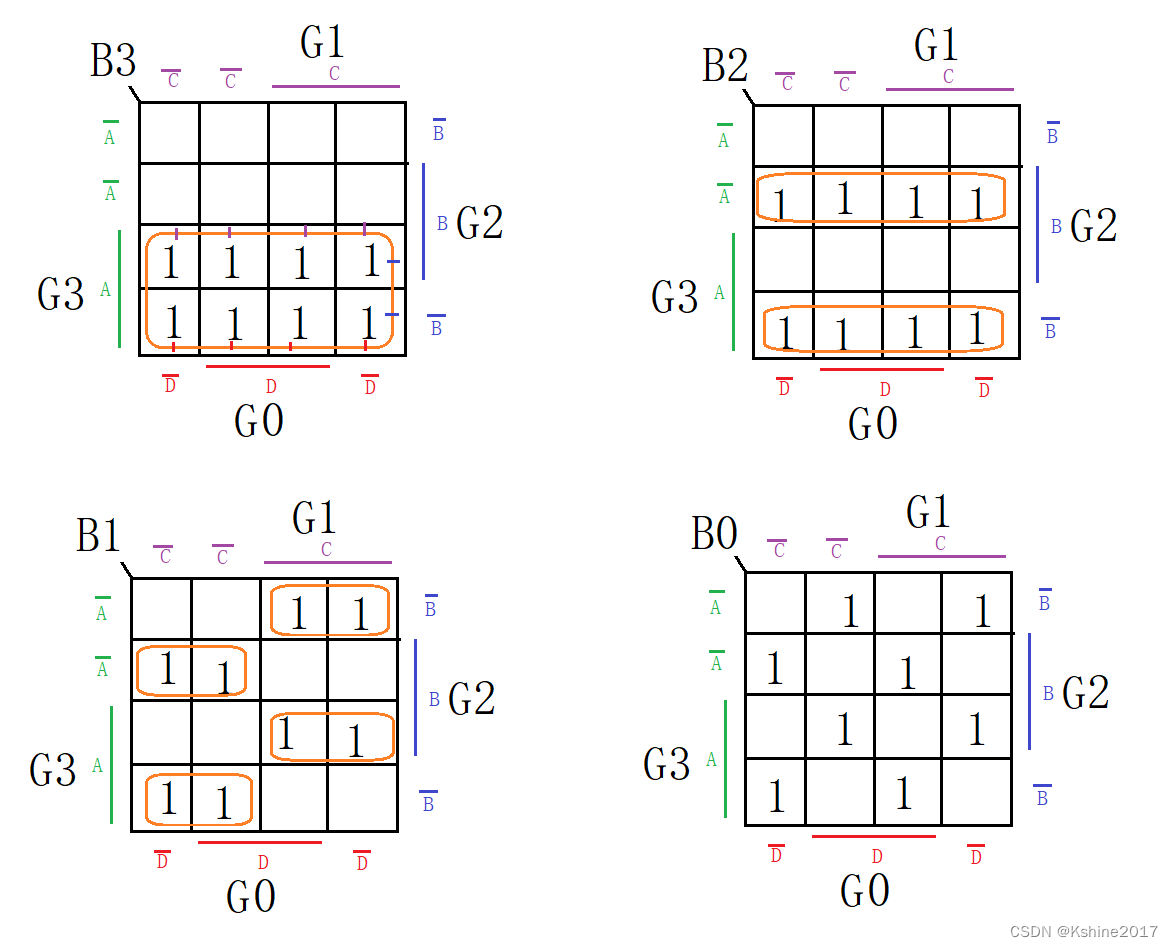

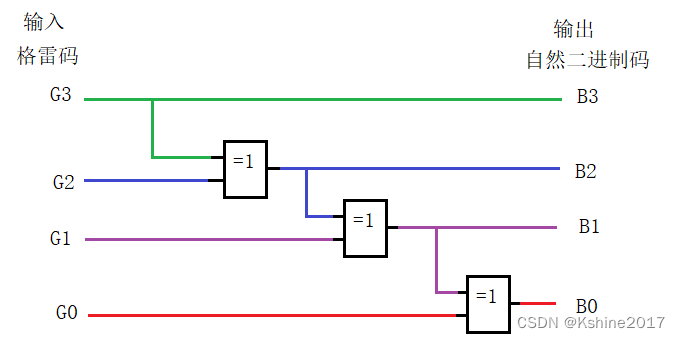

(1) Можно использовать любую схему логического элемента.

(2) 4-битный код Грея, преобразованный в естественный двоичный код.

Определите входные и выходные переменные.

(1) Входные переменные, Г 3 , Г 2 , Г 1 , Г 0 Г_3,Г_2,Г_1,Г_0г3,г2,г1,г0。

(2) Выходные переменные, В 3 , В 2 , В 1 , В 0 B_3,B_2,B_1,B_0Б3,Б2,Б1,Б0。

Назовите таблицу истинности.

| входить | выход | ||||||

| Г_3 | Г_2 | Г_1 | Г_0 | Б_3 | БИ 2 | Б_1 | Б_0 |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 0 | 1 | 0 | 0 | 0 | 1 |

| 0 | 0 | 1 | 1 | 0 | 0 | 1 | 0 |

| 0 | 0 | 1 | 0 | 0 | 0 | 1 | 1 |

| 0 | 1 | 1 | 0 | 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 1 | 0 | 1 | 0 | 1 |

| 0 | 1 | 0 | 1 | 0 | 1 | 1 | 0 |

| 0 | 1 | 0 | 0 | 0 | 1 | 1 | 1 |

| 1 | 1 | 0 | 0 | 1 | 0 | 0 | 0 |

| 1 | 1 | 0 | 1 | 1 | 0 | 0 | 1 |

| 1 | 1 | 1 | 1 | 1 | 0 | 1 | 0 |

| 1 | 1 | 1 | 0 | 1 | 0 | 1 | 1 |

| 1 | 0 | 1 | 0 | 1 | 1 | 0 | 0 |

| 1 | 0 | 1 | 1 | 1 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 | 1 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 | 1 | 1 | 1 | 1 |

На основе таблицы истинности нарисуйте карту Карно.

Перечислите логические выражения.

Б 3 = Г 3 Б_3 = Г_3Б3=г3

B 2 = G 3 ‾ ⋅ G 2 + G 3 ⋅ G 2 ‾ = G 3 ⊕ G 2 B_2 = надстрочный{G_3}·G_2 + G_3·надстрочный{G_2}=G_3⊕G_2Б2=г3⋅г2+г3⋅г2=г3⊕г2

B1 = G3 ‾ G2 G1 ‾ + G3 G2 ‾ G1 ‾ + G3 ‾ G2 ‾ G1 + G3 G2 G1 = (G3G2 ‾ + G3 ‾ G2) G1 ‾ + (G3G2 ‾ + G3 ‾ G2) ‾ G1 = G3 ⊕ G2 ⊕ G1 B_1 = надстрочный{G_3}G_2надстрочный{G_1}+G_3надстрочный{G_2}надстрочный{G_1}+надстрочный{G_3}надстрочный{G_2}G_1+G_3G_2G_1=(G_3надстрочный{G_2}+надстрочный{G_3}G_2)надстрочный{G_1}+надстрочный{(G_3надстрочный{G_2}+надстрочный{G_3}G_2)}G_1=G_3⊕G_2⊕G_1Б1=г3г2г1+г3г2г1+г3г2г1+г3г2г1=(г3г2+г3г2)г1+(г3г2+г3г2)г1=г3⊕г2⊕г1

В0 = Г3 ⊕ Г2 ⊕ Г1 ⊕ Г0 В_0=Г_3⊕Г_2⊕Г_1⊕Г_0Б0=г3⊕г2⊕г1⊕г0

Нарисуйте логическую схему.

| Я 0 Я_0я0 | Я 1 Я_1я1 | Я 2 Я_2я2 | Я 3 Я_3я3 | Г 1 Г_1И1 | Д 0 Д_0И0 |

|---|---|---|---|---|---|

| 1 | 0 | 0 | 0 | 0 | 0 |

| 0 | 1 | 0 | 0 | 0 | 1 |

| 0 | 0 | 1 | 0 | 1 | 0 |

| 0 | 0 | 0 | 1 | 1 | 1 |

| Я 0 Я_0я0 | Я 1 Я_1я1 | Я 2 Я_2я2 | Я 3 Я_3я3 | Г 1 Г_1И1 | Д 0 Д_0И0 |

|---|---|---|---|---|---|

| 1 | 0 | 0 | 0 | 0 | 0 |

| Икс | 1 | 0 | 0 | 0 | 1 |

| Икс | Икс | 1 | 0 | 1 | 0 |

| Икс | Икс | Икс | 1 | 1 | 1 |

| С 9 С_9С9 | С 8 С_8С8 | С 7 С_7С7 | С 6 С_6С6 | С 5 С_5С5 | С 4 С_4С4 | С 3 С_3С3 | С 2 С_2С2 | С 1 С_1С1 | С 0 С_0С0 | ААА | ВВБ | ССС | ДДД | ГС ГСГС | |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | |

| 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | |

| 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 0 | 0 | 0 | 1 | 1 | |

| 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 0 | 0 | 1 | 0 | 1 | |

| 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 0 | 0 | 1 | 1 | 1 | |

| 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 0 | 1 | 0 | 0 | 1 | |

| 1 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 0 | 1 | 1 | |

| 1 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 0 | 1 | |

| 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | |

| 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 1 | |

| 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 1 | 1 |

Типичное: приоритетный кодер CD4532 (снято с производства)

Приоритетный датчик I 7 имеет наивысший приоритет, а I 0 имеет наименьший приоритет. Приоритетный датчик I_7 имеет наивысший приоритет, а I_0 имеет наименьший приоритет.приоритетный кодеря7высший приоритет,я0Самый низкий приоритет.

Когда EI=1, когда все входы имеют низкий уровень, нетболее низкий приоритет Входной высокий уровень и выходной сигнал 000 в это время. В это время ЕО=1.

Только когда EI=1 и все входы равны 0, EO=1. Предназначен для каскадирования EI с другим устройством.

Когда EI=1, по крайней мере одна из входных клемм имеет высокий уровень 1 и GS=1.

Пожалуйста, обратитесь к книге за конкретными логическими выражениями и логическими блок-схемами.

| EI позволяет кодировать EI позволяет кодироватьЭяКодирование разрешено | Я 7 Я_7я7 | Я 6 Я_6я6 | Я 5 Я_5я5 | Я 4 Я_4я4 | Я 3 Я_3я3 | Я 2 Я_2я2 | Я 1 Я_1я1 | Я 0 Я_0я0 | Y 2 Y_2И2 | Г 1 Г_1И1 | Д 0 Д_0И0 | GS имеет вход 1 GS имеет вход 1ГСЕсть вход1 | ЭО вводит все 0 ЭО вводит все 0ЭОВведите все0 | |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 0 | Икс | Икс | Икс | Икс | Икс | Икс | Икс | Икс | 0 | 0 | 0 | 0 | 0 | |

| 1 | 1 | Икс | Икс | Икс | Икс | Икс | Икс | Икс | 1 | 1 | 1 | 1 | 0 | |

| 1 | 0 | 1 | Икс | Икс | Икс | Икс | Икс | Икс | 1 | 1 | 0 | 1 | 0 | |

| 1 | 0 | 0 | 1 | Икс | Икс | Икс | Икс | Икс | 1 | 0 | 1 | 1 | 0 | |

| 1 | 0 | 0 | 0 | 1 | Икс | Икс | Икс | Икс | 1 | 0 | 0 | 1 | 0 | |

| 1 | 0 | 0 | 0 | 0 | 1 | Икс | Икс | Икс | 0 | 1 | 1 | 1 | 0 | |

| 1 | 0 | 0 | 0 | 0 | 0 | 1 | Икс | Икс | 0 | 1 | 0 | 1 | 0 | |

| 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | Икс | 0 | 0 | 1 | 1 | 0 | |

| 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 1 | 0 | |

| 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 |

Когда EI 1 = 0, срез 1 отключен. Y 2 Y 1 Y 0 = = 000 , GS 1 = 0 , EO 1 = 0 . EI 0 = 0, чип 0 также отключен. Когда EI_1=0, срез 1 отключен. Y_2Y_1Y_0==000, GS_1=0, EO_1=0. EI_0=0, срез 0 также отключен.когдаЭя1=0время, фильм1Неполноценный.И2И1И0==000,гС1=0,ЭО1=0。Эя0=0,кусок0Тоже отключен.

Когда EI 1 = 1, разрешается кодировать срез 1. Если I 15 − I 8 = 000...000, то EO 1 = 1, поэтому EI 0 = 1. Срез 0 позволяет кодировать. Видно, что кодирование слайса 1 имеет более высокий приоритет, чем кодирование слайса 0. Когда EI_1=1, кодирование слайса 1 разрешено. Если I_{15} - I_8 = 000...000, то EO_1=. 1, поэтому EI_0=1. Срез 0 позволяет кодировать.Видно, что приоритет кодирования слайса 1 выше, чем приоритет кодирования слайса 0.когдаЭя1=1время, фильм1Кодирование допускается, еслия15−я8=000...000,в это времяЭО1=1,тем самымЭя0=1 .кусок0 Кодирование разрешено.Видно, что фильм1Кодирование имеет приоритет над срезами0кодирование。

Когда EI 1 = 1, кодирование разрешено в срезе 1. Если I 15 − I 8 имеет хотя бы одну 1, то EO 1 = 0, поэтому EI 0 = 0, и кодирование запрещено в срезе 0. Когда EI_1=1, кодирование разрешено в срезе 1. Если I_{15} – I_8 имеет хотя бы одну 1, то EO_1=0, поэтому EI_0=0, кодирование запрещено в срезе 0.когдаЭя1=1время, фильм1Кодирование допускается, еслия15−я8хотя бы один1,в это времяЭО1=0,тем самымЭя0=0,кусок0Кодирование запрещено.

| EI 1 позволяет кодировать EI_1 позволяет кодироватьЭя1Кодирование разрешено | EI 0 разрешает кодирование. EI_0 разрешает кодирование.Эя0Кодирование разрешено | Я 15 Я_{15}я15 | Я 14 Я_{14}я14 | Я 13 Я_{13}я13 | Я 12 Я_{12}я12 | Я 11 Я_{11}я11 | Я 10 Я_{10}я10 | Я 9 Я_{9}я9 | Я 8 Я_8я8 | Я 7 Я_7я7 | Я 6 Я_6я6 | Я 5 Я_5я5 | Я 4 Я_4я4 | Я 3 Я_3я3 | Я 2 Я_2я2 | Я 1 Я_1я1 | Я 0 Я_0я0 | Г 2 1 Г2_1И21 | Г 1 1 Г1_1И11 | Y 0 1 Y0_1И01 | Y 2 0 Y2_0И20 | Y 1 0 Y1_0И10 | Y 0 0 Y0_0И00 | EO 1 Введите все 0 EO_1 Введите все 0ЭО1Введите все0 | EO 0 Введите все 0 EO_0 Введите все 0ЭО0Введите все0 | GS 1 имеет вход 1 GS_1 имеет вход 1гС1Есть вход1 | GS 0 имеет вход 0 GS_0 имеет вход 0гС0Есть вход0 | Л 3 Л_3Л3 | Л 2 Л_2Л2 | Л 1 Л_1Л1 | Л 0 Л_0Л0 | |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 0 (срез 1 отключен) | ЭИ 0 = ЭО 1 = 0 ЭИ_0=ЭО_1=0Эя0=ЭО1=0(отключено в срезе 0) | Икс | Икс | Икс | Икс | Икс | Икс | Икс | Икс | Икс | Икс | Икс | Икс | Икс | Икс | Икс | Икс | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | |

| 1 | 0 | 1 | Икс | Икс | Икс | Икс | Икс | Икс | Икс | Икс | Икс | Икс | Икс | Икс | Икс | Икс | Икс | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 1 (чип 1 имеет вход) | 0 | 1 Л 3 = ГС 1 Л_3 = ГС_1Л3=гС1 | 1 Л 2 = Y 2 1 Л_2 =Y2_1Л2=И21 | 1 Л 1 = Y 1 1 Л_1 =Y1_1Л1=И11 | 1 Л 0 = Y 0 1 Л_0 =Y0_1Л0=И01 | |

| 1 | 0 | 0 | 1 | Икс | Икс | Икс | Икс | Икс | Икс | Икс | Икс | Икс | Икс | Икс | Икс | Икс | Икс | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 1 | 1 | 1 | 0 | |

| 1 | 0 | 0 | 0 | 1 | Икс | Икс | Икс | Икс | Икс | Икс | Икс | Икс | Икс | Икс | Икс | Икс | Икс | 1 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 1 | 1 | 0 | 1 | |

| 1 | 0 | 0 | 0 | 0 | 1 | Икс | Икс | Икс | Икс | Икс | Икс | Икс | Икс | Икс | Икс | Икс | Икс | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 1 | 1 | 0 | 0 | |

| 1 | 0 | 0 | 0 | 0 | 0 | 1 | Икс | Икс | Икс | Икс | Икс | Икс | Икс | Икс | Икс | Икс | Икс | 0 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 1 | 0 | 1 | 1 | |

| 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | Икс | Икс | Икс | Икс | Икс | Икс | Икс | Икс | Икс | Икс | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | |

| 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | Икс | Икс | Икс | Икс | Икс | Икс | Икс | Икс | Икс | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 1 | 0 | 0 | 1 | |

| 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | Икс | Икс | Икс | Икс | Икс | Икс | Икс | Икс | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 1 | 0 | 0 | 0 | |

| 1 | ЭИ 0 = ЭО 1 = 1 ЭИ_0=ЭО_1=1Эя0=ЭО1=1(шт. 0 работы) | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | Икс | Икс | Икс | Икс | Икс | Икс | Икс | 0 | 0 | 0 | 1 | 1 | 1 | 1 (вход чипа 1 — все 0) | 0 | 0 (Неверная кодировка для среза 1) | 1 | 0 Л 3 = ГС 1 Л_3 = ГС_1Л3=гС1 | 1 Л 2 = Y 2 0 Л_2 =Y2_0Л2=И20 | 1 Л 1 = Y 1 0 Л_1 =Y1_0Л1=И10 | 1 Л 0 = Y 0 0 Л_0 =Y0_0Л0=И00 | |

| 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | Икс | Икс | Икс | Икс | Икс | Икс | 0 | 0 | 0 | 1 | 1 | 0 | 1 | 0 | 0 | 1 | 0 | 1 | 1 | 0 | |

| 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | Икс | Икс | Икс | Икс | Икс | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 0 | 1 | 0 | 1 | 0 | 1 | |

| 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | Икс | Икс | Икс | Икс | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 0 | 1 | 0 | 1 | 0 | 0 | |

| 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | Икс | Икс | Икс | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 0 | 1 | 0 | 0 | 1 | 1 | |

| 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | Икс | Икс | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 0 | 1 | 0 | 0 | 1 | 0 | |

| 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | Икс | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 1 | |

| 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | |

| 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 (на входе чипа 0 все 0) | 0 | 0 (неверная кодировка фрагмента 0) | 0 | 0 | 0 | 0 |

| входить | выход | |||||

| /Э | А_1 | А_0 | /Y_3 | /Y_2 | /Y_1 | /Y_0 |

| 1 запрещено | Икс | Икс | 1 | 1 | 1 | 1 |

| 0 включить | 0 | 0 | 1 | 1 | 1 | 0 низкий активный |

| 0 включить | 0 | 1 | 1 | 1 | 0 низкая эффективность | 1 |

| 0 включить | 1 | 0 | 1 | 0 низкий активный | 1 | 1 |

| 0 включить | 1 | 1 | 0 низкий активный | 1 | 1 | 1 |

Y 0 ‾ = E ‾ ‾ ⋅ A 1 ‾ ⋅ A 0 ‾ ‾ надстрочный{Y_0} = надстрочный{надстрочный{надстрочный{E}}·надстрочный{A_1}·надстрочный{A_0}}И0=Э⋅А1⋅А0 //00

Y 1 ‾ = E ‾ ‾ ⋅ A 1 ‾ ⋅ A 0 ‾ надстрочный{Y_1} = надстрочный{надстрочный{надстрочный{E}}·надстрочный{A_1}·A_0}И1=Э⋅А1⋅А0 //01

Y 2 ‾ = E ‾ ‾ ⋅ A 1 ⋅ A 0 ‾ ‾ надстрочный{Y_2} = надстрочный{надстрочный{надстрочный{E}}·A_1·надстрочный{A_0}}И2=Э⋅А1⋅А0 //10

Y 3 ‾ = E ‾ ‾ ⋅ A 1 ⋅ A 0 ‾ надстрочный{Y_3} = надстрочный{надстрочный{надстрочный{E}}·A_1·A_0}И3=Э⋅А1⋅А0 //11

Y 0 ‾ = E 3 ⋅ E 2 ‾ ‾ ⋅ E 1 ‾ ‾ ⋅ A 2 ‾ ⋅ A 1 ‾ ⋅ A 0 ‾ ‾ надстрочный{Y_0} = надстрочный{E_3·надстрочный{надстрочный{E_2}}·надстрочный{надстрочный{E_1}}·надстрочный{A_2}·надстрочный{A_1}·надстрочный{A_0}}И0=Э3⋅Э2⋅Э1⋅А2⋅А1⋅А0 //000

Y 1 ‾ = E 3 ⋅ E 2 ‾ ‾ ⋅ E 1 ‾ ‾ ⋅ A 2 ‾ ⋅ A 1 ‾ ⋅ A 0 ‾ надстрочный{Y_1} = надстрочный{E_3·надстрочный{надстрочный{E_2}}·надстрочный{надстрочный{E_1}}·надстрочный{A_2}·надстрочный{A_1}·A_0}И1=Э3⋅Э2⋅Э1⋅А2⋅А1⋅А0 //001

Y 2 ‾ = E 3 ⋅ E 2 ‾ ‾ ⋅ E 1 ‾ ‾ ⋅ A 2 ‾ ⋅ A 1 ⋅ A 0 ‾ ‾ надстрочный{Y_2} = надстрочный{E_3·надстрочный{надстрочный{E_2}}·надстрочный{надстрочный{E_1}}·надстрочный{A_2}·A_1·надстрочный{A_0}}И2=Э3⋅Э2⋅Э1⋅А2⋅А1⋅А0 //010

Y 3 ‾ = E 3 ⋅ E 2 ‾ ‾ ⋅ E 1 ‾ ‾ ⋅ A 2 ‾ ⋅ A 1 ⋅ A 0 ‾ надстрочный{Y_3} = надстрочный{E_3·надстрочный{надстрочный{E_2}}·надстрочный{надстрочный{E_1}}·надстрочный{A_2}·A_1·A_0}И3=Э3⋅Э2⋅Э1⋅А2⋅А1⋅А0 //011

Y 4 ‾ = E 3 ⋅ E 2 ‾ ‾ ⋅ E 1 ‾ ‾ ⋅ A 2 ⋅ A 1 ‾ ⋅ A 0 ‾ ‾ надстрочный{Y_4} = надстрочный{E_3·надстрочный{надстрочный{E_2}}·надстрочный{надстрочный{E_1}}·A_2·надстрочный{A_1}·надстрочный{A_0}}И4=Э3⋅Э2⋅Э1⋅А2⋅А1⋅А0 //100

Y 5 ‾ = E 3 ⋅ E 2 ‾ ‾ ⋅ E 1 ‾ ‾ ⋅ A 2 ⋅ A 1 ‾ ⋅ A 0 ‾ надстрочный{Y_5} = надстрочный{E_3·надстрочный{надстрочный{E_2}}·надстрочный{надстрочный{E_1}}·A_2·надстрочный{A_1}·A_0}И5=Э3⋅Э2⋅Э1⋅А2⋅А1⋅А0 //101

Y 6 ‾ = E 3 ⋅ E 2 ‾ ‾ ⋅ E 1 ‾ ‾ ⋅ A 2 ⋅ A 1 ⋅ A 0 ‾ ‾ надстрочный{Y_6} = надстрочный{E_3·надстрочный{надстрочный{E_2}}·надстрочный{надстрочный{E_1}}·A_2·A_1·надстрочный{A_0}}И6=Э3⋅Э2⋅Э1⋅А2⋅А1⋅А0 //110

Y 7 ‾ = E 3 ⋅ E 2 ‾ ‾ ⋅ E 1 ‾ ‾ ⋅ A 2 ⋅ A 1 ⋅ A 0 ‾ надстрочный{Y_7} = надстрочный{E_3·надстрочный{надстрочный{E_2}}·надстрочный{надстрочный{E_1}}·A_2·A_1·A_0}И7=Э3⋅Э2⋅Э1⋅А2⋅А1⋅А0 //111

L = A ‾ ⋅ C ‾ + A ⋅ B = A ‾ ⋅ B ‾ ⋅ C ‾ + A ‾ ⋅ B ⋅ C ‾ + A ⋅ B ⋅ C ‾ + ABC = m 0 + m 2 + m 6 + m 7 L=надстрочный{A}·надстрочный{C}+A·B =надстрочный{A}·надстрочный{B}·надстрочный{C}+надстрочный{A}·B·надстрочный{C} + A·B·надстрочный{C}+ABC = m_0+m_2+m_6+m_7Л=А⋅С+А⋅Б=А⋅Б⋅С+А⋅Б⋅С+А⋅Б⋅С+АДо нашей эры=м0+м2+м6+м7

Y 0 ‾ = E 3 ⋅ E 2 ‾ ‾ ⋅ E 1 ‾ ‾ ⋅ A 2 ‾ ⋅ A 1 ‾ ⋅ A 0 ‾ ‾ = E 3 ⋅ E 2 ‾ ‾ ⋅ E 1 ‾ ‾ ⋅ m 0 ‾ надстрочный{Y_0} = надстрочный{E_3·надстрочный{надстрочный{E_2}}·надстрочный{надстрочный{E_1}}·надстрочный{A_2}·надстрочный{A_1}·надстрочный{A_0}} = надстрочный{E_3·надстрочный{надстрочный{E_2}}·надстрочный{надстрочный{E_1}}·м_0}И0=Э3⋅Э2⋅Э1⋅А2⋅А1⋅А0=Э3⋅Э2⋅Э1⋅м0 //000

Y 1 ‾ = E 3 ⋅ E 2 ‾ ‾ ⋅ E 1 ‾ ‾ ⋅ A 2 ‾ ⋅ A 1 ‾ ⋅ A 0 ‾ = E 3 ⋅ E 2 ‾ ‾ ⋅ E 1 ‾ ‾ ⋅ m 1 ‾ надстрочный{Y_1} = надстрочный{E_3·надстрочный{надстрочный{E_2}}·надстрочный{надстрочный{E_1}}·надстрочный{A_2}·надстрочный{A_1}·A_0} = надстрочный{E_3·надстрочный{надстрочный{E_2}}·надстрочный{надстрочный{E_1}}·м_1}И1=Э3⋅Э2⋅Э1⋅А2⋅А1⋅А0=Э3⋅Э2⋅Э1⋅м1 //001

Y 2 ‾ = E 3 ⋅ E 2 ‾ ‾ ⋅ E 1 ‾ ‾ ⋅ A 2 ‾ ⋅ A 1 ⋅ A 0 ‾ ‾ = E 3 ⋅ E 2 ‾ ‾ ⋅ E 1 ‾ ‾ ⋅ m 2 ‾ надстрочный{Y_2} = надстрочный{E_3·надстрочный{надстрочный{E_2}}·надстрочный{надстрочный{E_1}}·надстрочный{A_2}·A_1·надстрочный{A_0}}= надстрочный{E_3·надстрочный{надстрочный{E_2}}·надстрочный{надстрочный{E_1}}·м_2}И2=Э3⋅Э2⋅Э1⋅А2⋅А1⋅А0=Э3⋅Э2⋅Э1⋅м2 //010

Y 3 ‾ = E 3 ⋅ E 2 ‾ ‾ ⋅ E 1 ‾ ‾ ⋅ A 2 ‾ ⋅ A 1 ⋅ A 0 ‾ = E 3 ⋅ E 2 ‾ ‾ ⋅ E 1 ‾ ‾ ⋅ m 3 ‾ надстрочный{Y_3} = надстрочный{E_3·надстрочный{надстрочный{E_2}}·надстрочный{надстрочный{E_1}}·надстрочный{A_2}·A_1·A_0}= надстрочный{E_3·надстрочный{надстрочный{E_2}}·надстрочный{надстрочный{E_1}}·м_3}И3=Э3⋅Э2⋅Э1⋅А2⋅А1⋅А0=Э3⋅Э2⋅Э1⋅м3 //011

Y 4 ‾ = E 3 ⋅ E 2 ‾ ‾ ⋅ E 1 ‾ ‾ ⋅ A 2 ⋅ A 1 ‾ ⋅ A 0 ‾ ‾ = E 3 ⋅ E 2 ‾ ‾ ⋅ E 1 ‾ ‾ ⋅ m 4 ‾ надстрочный{Y_4} = надстрочный{E_3·надстрочный{надстрочный{E_2}}·надстрочный{надстрочный{E_1}}·A_2·надстрочный{A_1}·надстрочный{A_0}}= надстрочный{E_3·надстрочный{надстрочный{E_2}}·надстрочный{надстрочный{E_1}}·m_4}И4=Э3⋅Э2⋅Э1⋅А2⋅А1⋅А0=Э3⋅Э2⋅Э1⋅м4 //100

Y 5 ‾ = E 3 ⋅ E 2 ‾ ‾ ⋅ E 1 ‾ ‾ ⋅ A 2 ⋅ A 1 ‾ ⋅ A 0 ‾ = E 3 ⋅ E 2 ‾ ‾ ⋅ E 1 ‾ ‾ ⋅ m 5 ‾ надстрочный{Y_5} = надстрочный{E_3·надстрочный{надстрочный{E_2}}·надстрочный{надстрочный{E_1}}·A_2·надстрочный{A_1}·A_0}= надстрочный{E_3·надстрочный{надстрочный{E_2}}·надстрочный{надстрочный{E_1}}·m_5}И5=Э3⋅Э2⋅Э1⋅А2⋅А1⋅А0=Э3⋅Э2⋅Э1⋅м5 //101

Y 6 ‾ = E 3 ⋅ E 2 ‾ ‾ ⋅ E 1 ‾ ‾ ⋅ A 2 ⋅ A 1 ⋅ A 0 ‾ ‾ = E 3 ⋅ E 2 ‾ ‾ ⋅ E 1 ‾ ‾ ⋅ m 6 ‾ надстрочный{Y_6} = надстрочный{E_3·надстрочный{надстрочный{E_2}}·надстрочный{надстрочный{E_1}}·A_2·A_1·надстрочный{A_0}}= надстрочный{E_3·надстрочный{надстрочный{E_2}}·надстрочный{надстрочный{E_1}}·m_6}И6=Э3⋅Э2⋅Э1⋅А2⋅А1⋅А0=Э3⋅Э2⋅Э1⋅м6 //110

Y 7 ‾ = E 3 ⋅ E 2 ‾ ‾ ⋅ E 1 ‾ ‾ ⋅ A 2 ⋅ A 1 ⋅ A 0 ‾ = E 3 ⋅ E 2 ‾ ‾ ⋅ E 1 ‾ ‾ ⋅ m 7 ‾ надстрочный{Y_7} = надстрочный{E_3·надстрочный{надстрочный{E_2}}·надстрочный{надстрочный{E_1}}·A_2·A_1·A_0}= надстрочный{E_3·надстрочный{надстрочный{E_2}}·надстрочный{надстрочный{E_1}}·m_7}И7=Э3⋅Э2⋅Э1⋅А2⋅А1⋅А0=Э3⋅Э2⋅Э1⋅м7 //111

Убедитесь, что E 3 = 1, E 2 = 0, E 1 = 0. Убедитесь, что E_3=1, E_2=0, E_1=0.убеждатьсяЭ3=1,Э2=0,Э1=0, то есть Y 0 ‾ = м 0 ‾ , Y 2 ‾ = м 2 ‾ , Y 6 ‾ = м 6 ‾ , Y 7 ‾ = м 7 ‾ надстрочный{Y_0}=надстрочный{m_0},надстрочный{Y_2}=надстрочный{m_2},надстрочный{Y_6}=надстрочный{m_6},надстрочный{Y_7}=надстрочный{m_7}И0=м0,И2=м2,И6=м6,И7=м7。

Преобразуйте логические функции по закону обращения

L = L ‾ ‾ = м 0 + м 2 + м 6 + м 7 ‾ ‾ = м 0 ‾ ⋅ м 2 ‾ ⋅ м 6 ‾ ⋅ м 7 ‾ ‾ = м 0 + м 2 + м 6 + м 7 ‾ ‾ = Y 0 ‾ ⋅ Y 2 ‾ ⋅ Y 6 ‾ ⋅ Y 7 ‾ ‾ L=overline{overline{L}} = overline{overline{m_0+m_2+m_6+m_7}} = overline{overline{m_0}·overline{m_2}·overline{m_6}·overline{m_7}} = надстрочный{надстрочный{m_0+m_2+m_6+m_7}} = надстрочный{надстрочный{Y_0}·надстрочный{Y_2}·надстрочный{Y_6}·надстрочный{Y_7}}Л=Л=м0+м2+м6+м7=м0⋅м2⋅м6⋅м7=м0+м2+м6+м7=И0⋅И2⋅И6⋅И7

Получить логическую схему

774HC42

4 входа

10 выходных клемм, выход активен на низком уровне, что соответствует десятичным числам 0–9.

4 входных терминала, всего 16 ситуаций

только м 0 , м 1 , м 2 . . . . . . м 9 м_0 ,м_1,м_2......м_9м0,м1,м2......м9Это действительный вход (соответствующий выходной контакт имеет низкий уровень 0, а остальные выходы имеют высокий уровень 1).

Среди оставшихся 6 м 10 , м 11 , м 12 . . . . . . м 15 м_{10} ,м_{11},м_{12}......м_{15}м10,м11,м12......м15Это означает, что нет действительного вывода декодирования (если он недействителен, все выходные данные имеют высокий уровень 1).

Нарисуйте диаграммы входных и выходных сигналов 74HC42.

Принцип цифровой трубки

Встроенный декодер семисегментного дисплея. 74HC4511 (общий катод) (загорается высокий уровень)

ЛЕ ЛЕЛЭВключение фиксации

LT ‾ надстрочный{LT}ЛТвход для проверки лампы, когда LT ‾ = 0 надстрочный{LT}=0ЛТ=0Когда , ag выводит все 1 и отображает шрифт «8».

BL ‾ надстрочный{BL}БЛВход выключения света, когда LT ‾ = 1 и BL ‾ = 1 надчеркивание{LT}=1 и надчеркивание{BL}=1ЛТ=1,иБЛ=1 Когда , ag все выходы 0. Может использоваться для гашения ненужного отображаемого нуля «0».

Д 3 Д 2 Д 1 Д 0 Д_3Д_2Д_1Д_0Д3Д2Д1Д0=0000, соответствующий выходной символ «0».

Д 3 Д 2 Д 1 Д 0 Д_3Д_2Д_1Д_0Д3Д2Д1Д0=0001, соответствующий выходной шрифт «1».

Д 3 Д 2 Д 1 Д 0 Д_3Д_2Д_1Д_0Д3Д2Д1Д0=0010, соответствующий выходной шрифт «2».

Д 3 Д 2 Д 1 Д 0 Д_3Д_2Д_1Д_0Д3Д2Д1Д0=0011, соответствующий выходной шрифт «3».

Д 3 Д 2 Д 1 Д 0 Д_3Д_2Д_1Д_0Д3Д2Д1Д0=0100, соответствующий выходной шрифт «4».

Д 3 Д 2 Д 1 Д 0 Д_3Д_2Д_1Д_0Д3Д2Д1Д0=0101, соответствующий выходной шрифт «5».

Д 3 Д 2 Д 1 Д 0 Д_3Д_2Д_1Д_0Д3Д2Д1Д0=0110, соответствующий выходной шрифт «6».

Д 3 Д 2 Д 1 Д 0 Д_3Д_2Д_1Д_0Д3Д2Д1Д0=0111, соответствующий выходной шрифт «7».

Д 3 Д 2 Д 1 Д 0 Д_3Д_2Д_1Д_0Д3Д2Д1Д0=1000, соответствующий выходной шрифт «8».

Д 3 Д 2 Д 1 Д 0 Д_3Д_2Д_1Д_0Д3Д2Д1Д0=1001, соответствующий выходной шрифт «9».

1010-1111, выходной

От одного ко многим данные по общей линии данных отправляются по разным каналам по мере необходимости.

Аналог "однополюсный многопозиционный переключатель"

Используя декодер уникальных адресов, реализуйте распределитель данных

Например, 74x138 объединяет декодер с 3 на 8 строк.

E 1 ‾ как надчеркивание ввода данных{E_1} как ввод данныхЭ1в качестве ввода данных

Г 0 Г 1 Г 2 Г 3 Г 4 Г 5 Г 6 Г 7 Г_0 Г_1 Г_2Г_3Г_4Г_5Г_6Г_7И0И1И2И3И4И5И6И78 каналов вывода данных

Y 2 ‾ = E 3 ⋅ E 2 ‾ ‾ ⋅ E 1 ‾ ‾ ⋅ A 2 ‾ ⋅ A 1 ⋅ A 0 ‾ ‾ надстрочный{Y_2} = надстрочный{E_3·надстрочный{надстрочный{E_2}}·надстрочный{надстрочный{E_1}}·надстрочный{A_2}·A_1·надстрочный{A_0}}И2=Э3⋅Э2⋅Э1⋅А2⋅А1⋅А0 //010

На фото выше, E 3 = 1 , E 2 ‾ = 0 E_3=1,надчеркнуть{E_2}=0Э3=1,Э2=0, когда адресная строка А 2 А 1 А 0 = 010 А_2А_1А_0=010А2А1А0=010час, Y 2 ‾ = E 1 ‾ надстрочный{Y_2}=надстрочный{E_1}И2=Э1

По тому же принципу мы можем сделать вывод:

Когда адресная строка А 2 А 1 А 0 = 000 А_2А_1А_0=000А2А1А0=000час, Y 0 ‾ = E 1 ‾ = D надстрочный{Y_0}=надстрочный{E_1}=DИ0=Э1=Д,другой Yx = 1 Y_x=1ИИкс=1。

Когда адресная строка А 2 А 1 А 0 = 001 А_2А_1А_0=001А2А1А0=001час, Y 1 ‾ = E 1 ‾ = D надстрочный{Y_1}=надстрочный{E_1}=DИ1=Э1=Д,другой Yx = 1 Y_x=1ИИкс=1。

Когда адресная строка А 2 А 1 А 0 = 010 А_2А_1А_0=010А2А1А0=010час, Y 2 ‾ = E 1 ‾ = D надстрочная черта{Y_2}=надстрочная черта{E_1}=DИ2=Э1=Д,другой Yx = 1 Y_x=1ИИкс=1。

Когда адресная строка А 2 А 1 А 0 = 011 А_2А_1А_0=011А2А1А0=011час, Y 3 ‾ = E 1 ‾ = D надстрочная черта{Y_3}=надстрочная черта{E_1}=DИ3=Э1=Д,другой Yx = 1 Y_x=1ИИкс=1。

Когда адресная строка А 2 А 1 А 0 = 100 А_2А_1А_0=100А2А1А0=100час, Y 4 ‾ = E 1 ‾ = D надстрочная черта{Y_4}=надстрочная черта{E_1}=DИ4=Э1=Д,другой Yx = 1 Y_x=1ИИкс=1。

Когда адресная строка А 2 А 1 А 0 = 101 А_2А_1А_0=101А2А1А0=101час, Y 5 ‾ = E 1 ‾ = D надстрочная черта{Y_5}=надстрочная черта{E_1}=DИ5=Э1=Д,другой Yx = 1 Y_x=1ИИкс=1。

Когда адресная строка А 2 А 1 А 0 = 110 А_2А_1А_0=110А2А1А0=110час, Y 6 ‾ = E 1 ‾ = D надстрочная черта{Y_6}=надстрочная черта{E_1}=DИ6=Э1=Д,другой Yx = 1 Y_x=1ИИкс=1。

Когда адресная строка А 2 А 1 А 0 = 111 А_2А_1А_0=111А2А1А0=111час, Y 7 ‾ = E 1 ‾ = D надстрочная черта{Y_7}=надстрочная черта{E_1}=DИ7=Э1=Д,другой Yx = 1 Y_x=1ИИкс=1。

Y = С 2 ‾ ⋅ С 1 ‾ ⋅ С 0 ‾ ⋅ Д 0 + С 2 ‾ ⋅ С 1 ‾ ⋅ С 0 ⋅ Д 1 + С 2 ‾ ⋅ С 1 ⋅ С 0 ‾ ⋅ Д 2 + С 2 ‾ ⋅ С 1 ⋅ С 0 ⋅ Д 3 + С 2 ⋅ С 1 ‾ ⋅ С 0 ‾ ⋅ Д 4 + С 2 ⋅ С 1 ‾ ⋅ С 0 ⋅ Д 5 + С 2 ⋅ С 1 ⋅ С 0 ‾ ⋅ Д 6 + С 2 ⋅ С 1 ⋅ С 0 ⋅ D 7 Y=надстрочный{S_2}·надстрочный{S_1}·надстрочный{S_0}·D_0 +надстрочный{S_2}·надстрочный{S_1}·S_0·D_1 +надстрочный{S_2}·S_1·надстрочный{S_0}·D_2 +надстрочный{S_2}·S_1·S_0·D_3 +S_2·надстрочный{S_1}·надстрочный{S_0}·D_4 +S_2·надстрочный{S_1}·S_0·D_5 +S_2·S_1·надстрочный{S_0}·D_6 +S_2·S_1·S_0·D_7И=С2⋅С1⋅С0⋅Д0+С2⋅С1⋅С0⋅Д1+С2⋅С1⋅С0⋅Д2+С2⋅С1⋅С0⋅Д3+С2⋅С1⋅С0⋅Д4+С2⋅С1⋅С0⋅Д5+С2⋅С1⋅С0⋅Д6+С2⋅С1⋅С0⋅Д7

Расширения для селекторов данных.

генератор логических функций

Известный селектор данных 8 к 1.

Y = С 2 ‾ ⋅ С 1 ‾ ⋅ С 0 ‾ ⋅ Д 0 + С 2 ‾ ⋅ С 1 ‾ ⋅ С 0 ⋅ Д 1 + С 2 ‾ ⋅ С 1 ⋅ С 0 ‾ ⋅ Д 2 + С 2 ‾ ⋅ С 1 ⋅ С 0 ⋅ Д 3 + С 2 ⋅ С 1 ‾ ⋅ С 0 ‾ ⋅ Д 4 + С 2 ⋅ С 1 ‾ ⋅ С 0 ⋅ Д 5 + С 2 ⋅ С 1 ⋅ С 0 ‾ ⋅ Д 6 + С 2 ⋅ С 1 ⋅ С 0 ⋅ D 7 Y=надстрочный{S_2}·надстрочный{S_1}·надстрочный{S_0}·D_0 +надстрочный{S_2}·надстрочный{S_1}·S_0·D_1 +надстрочный{S_2}·S_1·надстрочный{S_0}·D_2 +надстрочный{S_2}·S_1·S_0·D_3 +S_2·надстрочный{S_1}·надстрочный{S_0}·D_4 +S_2·надстрочный{S_1}·S_0·D_5 +S_2·S_1·надстрочный{S_0}·D_6 +S_2·S_1·S_0·D_7И=С2⋅С1⋅С0⋅Д0+С2⋅С1⋅С0⋅Д1+С2⋅С1⋅С0⋅Д2+С2⋅С1⋅С0⋅Д3+С2⋅С1⋅С0⋅Д4+С2⋅С1⋅С0⋅Д5+С2⋅С1⋅С0⋅Д6+С2⋅С1⋅С0⋅Д7

Y = м0 ⋅ Д0 + м1 ⋅ Д1 + м2 ⋅ Д2 + м3 ⋅ Д3 + м4 ⋅ Д4 + м5 ⋅ Д5 + м6 ⋅ Д6 + м7 ⋅ Д7 Y=м_0·Д_0 +м_1·Д_1 +м_2·Д_2 +м_3·Д_3 +м_4·Д_4 +м_5·Д_5 +м_6·Д_6 +м_7·Д_7И=м0⋅Д0+м1⋅Д1+м2⋅Д2+м3⋅Д3+м4⋅Д4+м5⋅Д5+м6⋅Д6+м7⋅Д7

логическая функция L = A ‾ BC + AB ‾ C + ABL=надстрочный{A}BC+Aнадстрочный{B}C+ABЛ=АДо нашей эры+АБС+АБ

L = A ‾ BC + AB ‾ C + AB = A ‾ BC + AB ‾ C + ABC ‾ + ABC = m 3 + m 5 + m 6 + m 7 L=надстрочная линия{A}BC+Aнадстрочная линия{B}C+AB=надстрочная линия{A}BC+Aнадстрочная линия{B}C+ABнадстрочная линия{C}+ABC=m_3+m_5+m_6+m_7Л=АДо нашей эры+АБС+АБ=АДо нашей эры+АБС+АБС+АДо нашей эры=м3+м5+м6+м7

Используйте селектор данных 8 к 1 для реализации вышеуказанной функции L

L = Y = м 3 + м 5 + м 6 + м 7 , где Д 7 Д 6 Д 5 Д 3 = 1111 , Д 4 Д 2 Д 1 Д 0 = 0000 L=Y=m_3+m_5+m_6+m_7, Среди них D_7D_6D_5D_3=1111, D_4D_2D_1D_0=0000Л=И=м3+м5+м6+м7,вД7Д6Д5Д3=1111,Д4Д2Д1Д0=0000

Параллельные данные для последовательных данных

| А | Б | ФА > Б Ф_{А>Б}ФА>Б | ФА < Б Ф_{АФА<Б | ФА = = Б Ф_{А==Б}ФА==Б |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 1 |

| 0 | 1 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 0 |

| 1 | 1 | 0 | 0 | 1 |

| А 1 ? Б 1 А _1?Б_1А1?Б1 | А 0 ? Б 0 А_0?Б_0А0?Б0 | ФА > Б Ф_{А>Б}ФА>Б | ФА < Б Ф_{АФА<Б | ФА = = Б Ф_{А==Б}ФА==Б |

|---|---|---|---|---|

| А 1 > Б 1 А_1>Б_1А1>Б1 | Икс | 1 | 0 | 0 |

| А 1 < Б 1 А_1А1<Б1 | Икс | 0 | 1 | 0 |

| А 1 = = Б 1 А_1==Б_1А1==Б1 | А 0 > Б 0 А_0>Б_0А0>Б0 | 1 | 0 | 0 |

| А 1 = = Б 1 А_1==Б_1А1==Б1 | А 0 < Б 0 А_0А0<Б0 | 0 | 1 | 0 |

| А 1 = = Б 1 А_1==Б_1А1==Б1 | А 0 = = Б 0 А_0==Б_0А0==Б0 | 0 | 0 | 1 |

логическое выражение

ФА > В = ФА 1 > В 1 + ФА 1 = = В 1 ⋅ ФА 0 > В 0 F_{A>B} = F_{A_1>B_1} +F_{A_1==B_1}·F_{A_0>B_0}ФА>Б=ФА1>Б1+ФА1==Б1⋅ФА0>Б0

ФА < В = ФА 1 < В 1 + ФА 1 = = В 1 ⋅ ФА 0 < В 0 F_{AФА<Б=ФА1<Б1+ФА1==Б1⋅ФА0<Б0

ФА = = Б = ФА 1 = = Б 1 ⋅ ФА 0 = = Б 0 Ф_{А==Б} = Ф_{А_1==Б_1}·Ф_{А_0==Б_0}ФА==Б=ФА1==Б1⋅ФА0==Б0

логическая схема

Последовательное соединение, расширенное до 8-битного числового компаратора

Параллельное соединение, расширенное до 16-битного числового компаратора.

При параллельном подключении скорость высокая.