le mie informazioni di contatto

Posta[email protected]

2024-07-12

한어Русский языкEnglishFrançaisIndonesianSanskrit日本語DeutschPortuguêsΕλληνικάespañolItalianoSuomalainenLatina

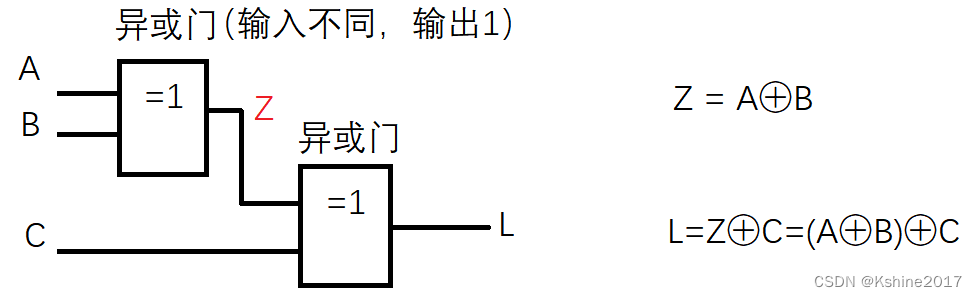

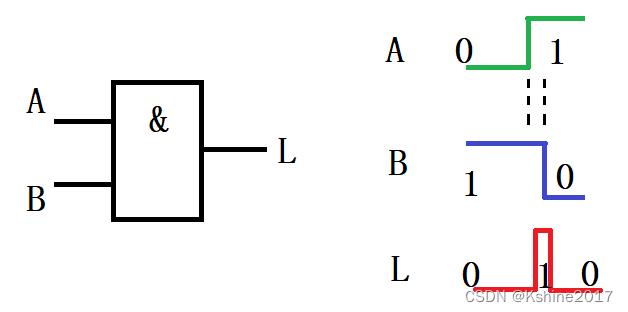

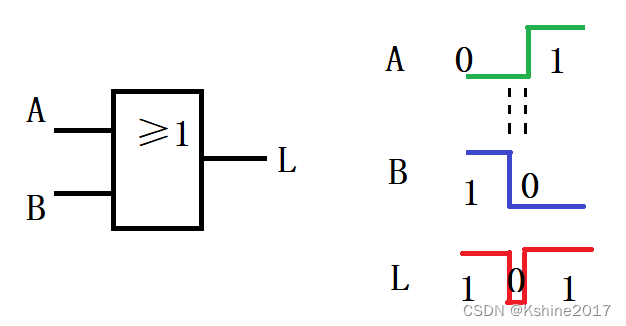

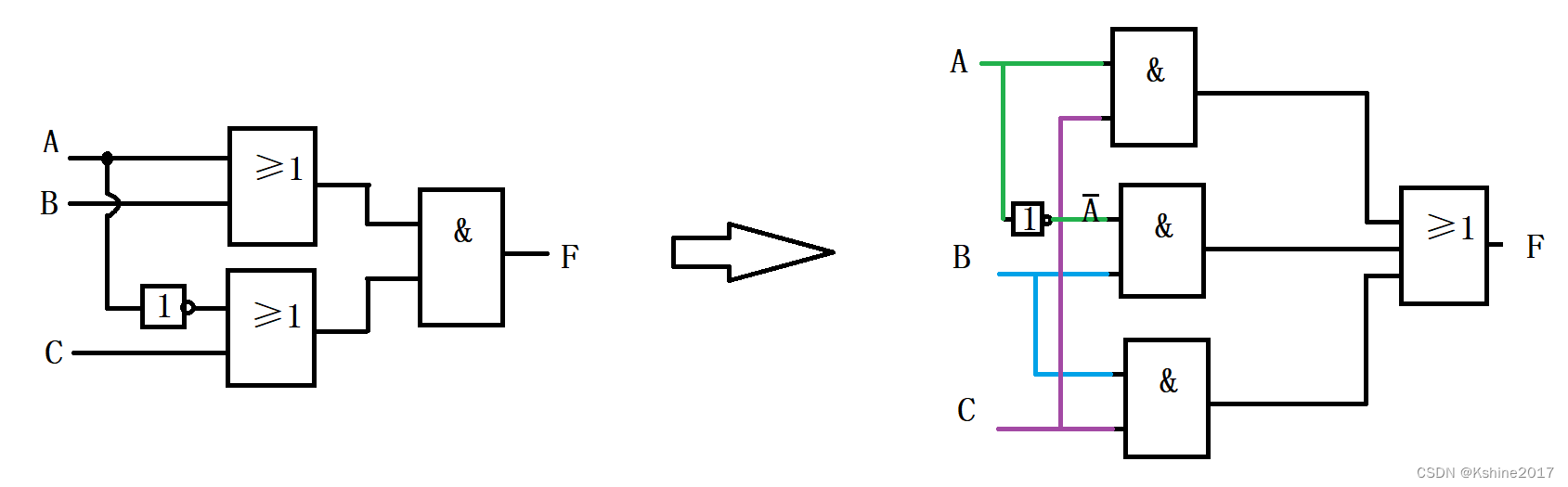

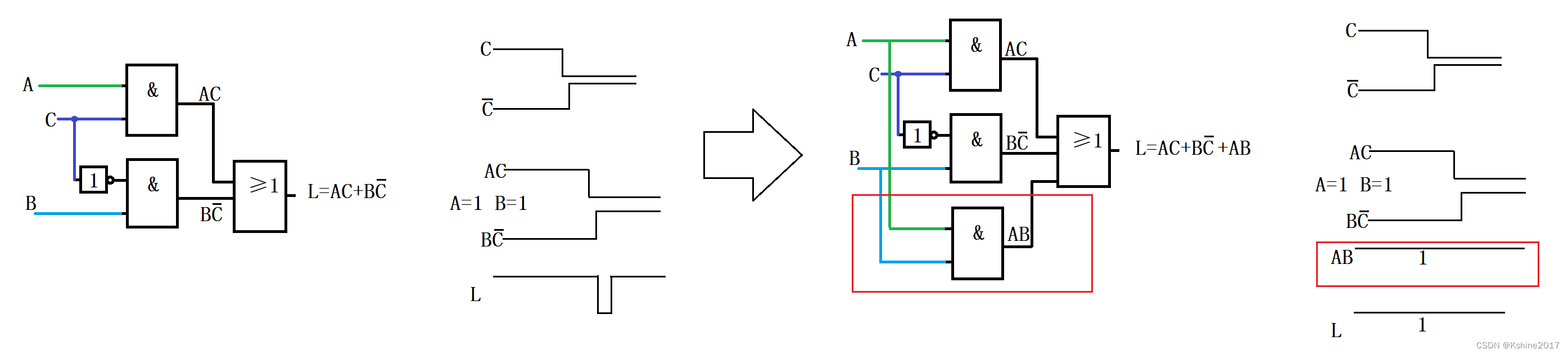

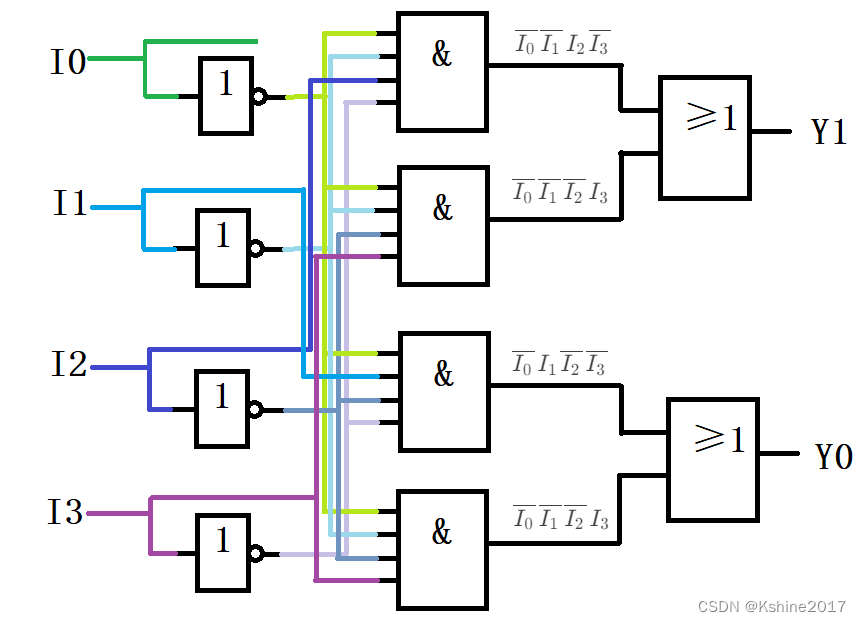

(1) Come mostrato nella figura seguente.

(2) Elenca la tabella della verità

| UN | B | C | La | L |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 | 1 |

| 0 | 1 | 0 | 1 | 1 |

| 0 | 1 | 1 | 1 | 0 |

| 1 | 0 | 0 | 1 | 1 |

| 1 | 0 | 1 | 1 | 0 |

| 1 | 1 | 0 | 0 | 0 |

| 1 | 1 | 1 | 0 | 1 |

(3) AnalizzareCircuito a parità dispariFunzione.

(1) Sulla base del circuito a parità dispari, aggiungendo un inverter all'estremità di uscita, possiamo ottenereAnche circuito di parità。

| UN | B | C | X | E | La |

|---|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 | 0 | 1 |

| 0 | 1 | 0 | 0 | 1 | 0 |

| 0 | 1 | 1 | 0 | 1 | 1 |

| 1 | 0 | 0 | 1 | 1 | 1 |

| 1 | 0 | 1 | 1 | 1 | 0 |

| 1 | 1 | 0 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 | 0 | 0 |

Bisogno.

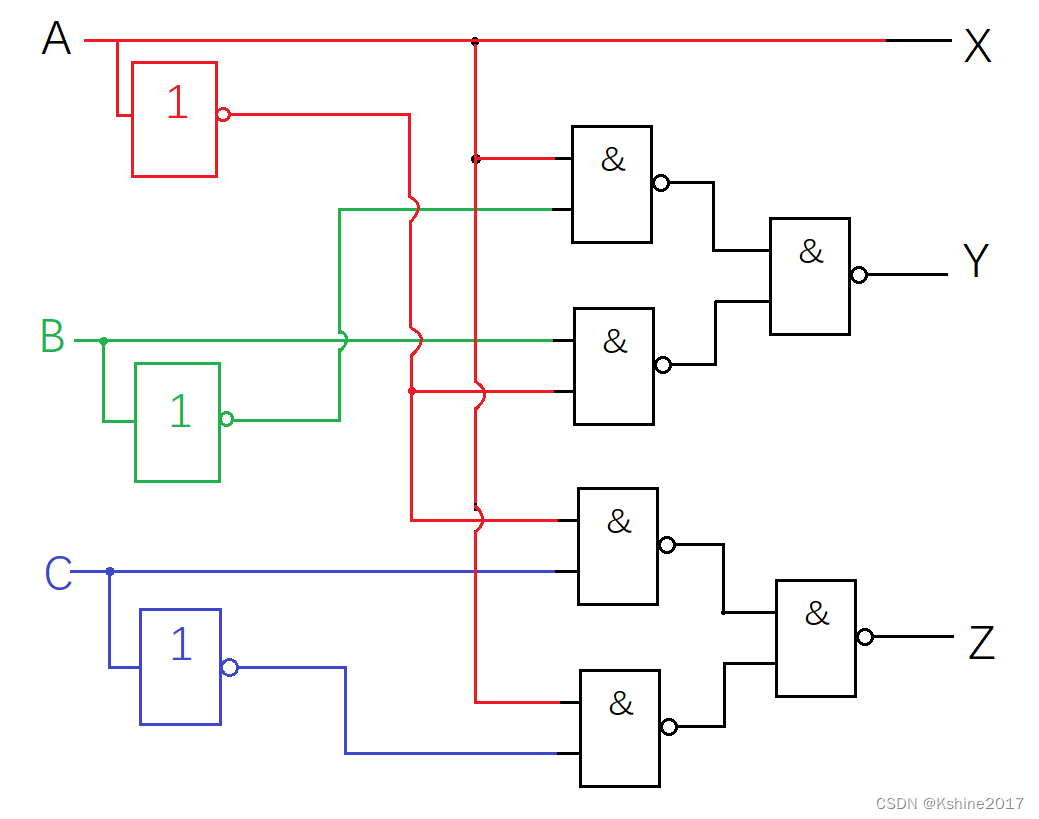

(1) Utilizzare 2 ingressiPorta NAND,invertitore.

(2) Indicatore luminoso n. 1, indicatore luminoso di arrivo del treno espresso. Priorità alta.

(3) Indicatore luminoso n. 2, indicatore luminoso diretto che entra nella stazione. In priorità.

(4) Indicatore luminoso n. 3, indicatore luminoso del treno lento che entra nella stazione. Bassa priorità.

(5) Può essere accesa al massimo una spia contemporaneamente.

Definire le variabili di input e output.

(1) Segnale di ingresso, I 0 richiesta espressa, I 1 richiesta espressa diretta, I 2 richiesta treno locale I_0 richiesta espressa, I_1 richiesta espressa diretta, I_2 richiesta treno localeIOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOO0richiesta espressa,IOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOO1Basta richiederlo rapidamente,IOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOO2Richiesta di treno lento . 1 significa che c'è una richiesta in entrata, 0 significa che non c'è nessuna richiesta in entrata.

(2) Segnale di uscita, L 0 spia fermata rapida, L 1 spia fermata rapida diretta, L 2 spia fermata treno locale L_0 spia fermata rapida, L_1 spia fermata rapida diretta, L_2 spia fermata treno localeL0Luce di arrivo espresso,L1Spia di arresto diretta,L2Spia di arrivo treno lento . 1 significa che la luce è accesa, 0 significa che la luce è spenta.

Tavola della verità.

| accedere | produzione | ||||

| Io_0 | Io_1 | Io_2 | L_0 | L_1 | L_2 |

| 0 | 0 | 0 | 0 | 0 | 0 |

| 1 | X | X | 1 | 0 | 0 |

| 0 | 1 | X | 0 | 1 | 0 |

| 0 | 0 | 1 | 0 | 0 | 1 |

Elenca le espressioni logiche

L 0 = Io 0 L_0 = Io_0L0=IOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOO0

L 1 = I 0 ‾ ⋅ I 1 L_1 = sopralinea{I_0}·I_1L1=IOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOO0⋅IOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOO1

L 2 = I 0 ‾ ⋅ I 1 ‾ ⋅ I 2 L_2 = sopralinea{I_0}·sopralinea{I_1}·I_2L2=IOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOO0⋅IOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOO1⋅IOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOO2

Convertire in formato NAND come richiesto.

L 0 = Io 0 L_0 = Io_0L0=IOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOO0

L 1 = I 0 ‾ ⋅ I 1 ‾ ‾ L_1 = linea di contorno{linea di contorno{linea di contorno{I_0}·I_1}}L1=IOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOO0⋅IOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOO1

L 2 = I 0 ‾ ⋅ I 1 ‾ ‾ ‾ ⋅ I 2 ‾ ‾ L_2 =overline{overline{overline{overline{overline{I_0}·overline{I_1}}}·I_2}}L2=IOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOO0⋅IOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOO1⋅IOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOO2

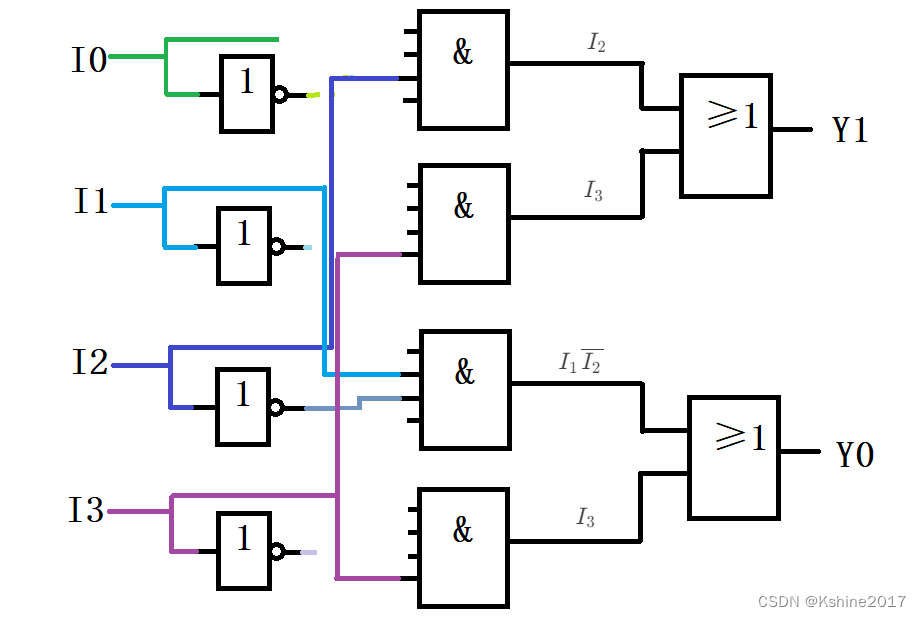

Disegna un diagramma logico.

(1) Un chip 74HC00 contiene quattro porte NAND CMOS a 2 ingressi.

(2) Un chip 74HC04 contiene 6 inverter CMOS.

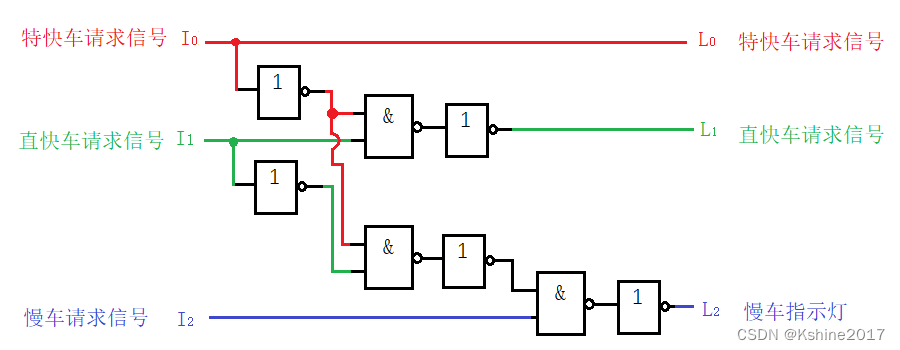

Bisogno.

(1) È possibile utilizzare qualsiasi circuito di porta logica.

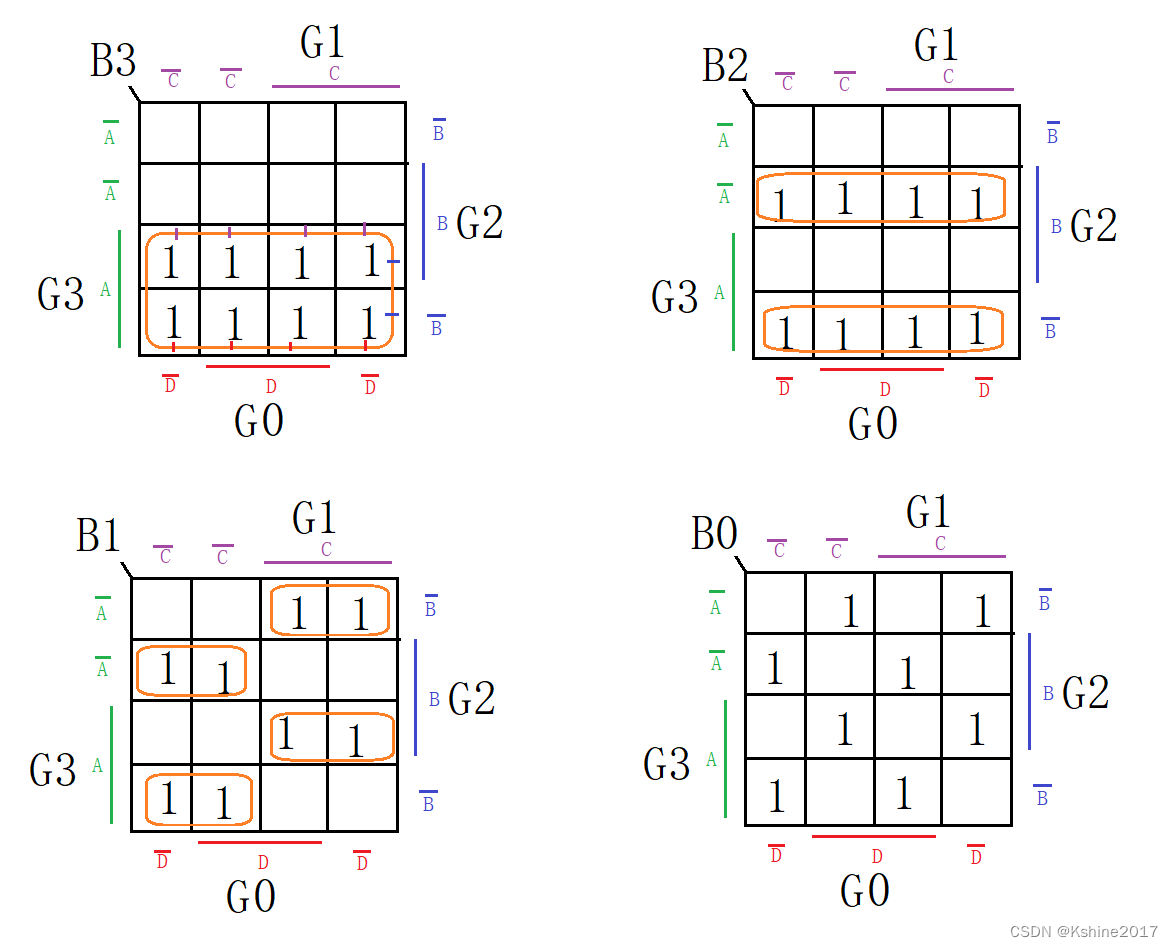

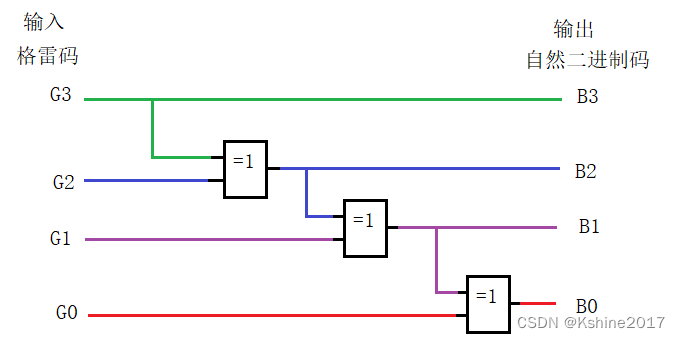

(2) Codice Gray a 4 bit, convertito in codice binario naturale.

Definire le variabili di input e output.

(1) Variabili di ingresso, G3, G2, G1, G0 G_3,G_2,G_1,G_0G3,G2,G1,G0。

(2) Variabili di output, B3, B2, B1, B0 B_3,B_2,B_1,B_0B3,B2,B1,B0。

Elenca la tavola della verità.

| accedere | produzione | ||||||

| G_3 | G_2 | G_1 | G_0 | B_3 | B_2 | B_1 | B_0 |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 0 | 1 | 0 | 0 | 0 | 1 |

| 0 | 0 | 1 | 1 | 0 | 0 | 1 | 0 |

| 0 | 0 | 1 | 0 | 0 | 0 | 1 | 1 |

| 0 | 1 | 1 | 0 | 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 1 | 0 | 1 | 0 | 1 |

| 0 | 1 | 0 | 1 | 0 | 1 | 1 | 0 |

| 0 | 1 | 0 | 0 | 0 | 1 | 1 | 1 |

| 1 | 1 | 0 | 0 | 1 | 0 | 0 | 0 |

| 1 | 1 | 0 | 1 | 1 | 0 | 0 | 1 |

| 1 | 1 | 1 | 1 | 1 | 0 | 1 | 0 |

| 1 | 1 | 1 | 0 | 1 | 0 | 1 | 1 |

| 1 | 0 | 1 | 0 | 1 | 1 | 0 | 0 |

| 1 | 0 | 1 | 1 | 1 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 | 1 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 | 1 | 1 | 1 | 1 |

Disegna una mappa di Karnaugh basata sulla tavola della verità.

Elenca le espressioni logiche.

B3 = G3 B_3 = G_3B3=G3

B 2 = G 3 ‾ ⋅ G 2 + G 3 ⋅ G 2 ‾ = G 3 ⊕ G 2 B_2 = sopralinea{G_3}·G_2 + G_3·sopralinea{G_2}=G_3⊕G_2B2=G3⋅G2+G3⋅G2=G3⊕G2

Italiano: B 1 = G 3 ‾ G 2 G 1 ‾ + G 3 G 2 ‾ G 1 ‾ + G 3 ‾ G 2 ‾ G 1 + G 3 G 2 G 1 = ( G 3 G 2 ‾ + G 3 ‾ G 2 ) G 1 ‾ + ( G 3 G 2 ‾ + G 3 ‾ G 2 ) ‾ G 1 = G 3 ⊕ G 2 ⊕ G 1 B_1 = sopralinea{G_3}G_2sopralinea{G_1}+G_3sopralinea{G_2}sopralinea{G_1}+sopralinea{G_3}sopralinea{G_2}G_1+G_3G_2G_1=(G_3sopralinea{G_2}+sopralinea{G_3}G_2)sopralinea{G_1}+sopralinea{(G_3sopralinea{G_2}+sopralinea{G_3}G_2)}G_1=G_3⊕G_2⊕G_1B1=G3G2G1+G3G2G1+G3G2G1+G3G2G1=(G3G2+G3G2)G1+(G3G2+G3G2)G1=G3⊕G2⊕G1

B 0 = G 3 ⊕ G 2 ⊕ G 1 ⊕ G 0 B_0=G_3⊕G_2⊕G_1⊕G_0B0=G3⊕G2⊕G1⊕G0

Disegna un diagramma logico.

| Io 0 io_0IOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOO0 | Io 1 Io_1IOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOO1 | Io 2 io_2IOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOO2 | Io 3 Io_3IOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOO3 | E 1 E_1E1 | E 0 E_0E0 |

|---|---|---|---|---|---|

| 1 | 0 | 0 | 0 | 0 | 0 |

| 0 | 1 | 0 | 0 | 0 | 1 |

| 0 | 0 | 1 | 0 | 1 | 0 |

| 0 | 0 | 0 | 1 | 1 | 1 |

| Io 0 io_0IOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOO0 | Io 1 Io_1IOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOO1 | Io 2 io_2IOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOO2 | Io 3 Io_3IOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOO3 | E 1 E_1E1 | E 0 E_0E0 |

|---|---|---|---|---|---|

| 1 | 0 | 0 | 0 | 0 | 0 |

| X | 1 | 0 | 0 | 0 | 1 |

| X | X | 1 | 0 | 1 | 0 |

| X | X | X | 1 | 1 | 1 |

| L'9 L_9S9 | L'8 L_8S8 | L'uomo 7 L_7S7 | L'uomo 6 L_6S6 | L'uomo 5 L_5S5 | E 4 E_4S4 | E 3 E_3S3 | L2 L_2S2 | L1 L_1S1 | Il 0 Il_0S0 | aaUN | BBB | CCC | GGD | GSGS, il mio nome è G.S.GS | |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | |

| 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | |

| 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 0 | 0 | 0 | 1 | 1 | |

| 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 0 | 0 | 1 | 0 | 1 | |

| 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 0 | 0 | 1 | 1 | 1 | |

| 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 0 | 1 | 0 | 0 | 1 | |

| 1 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 0 | 1 | 1 | |

| 1 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 0 | 1 | |

| 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | |

| 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 1 | |

| 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 1 | 1 |

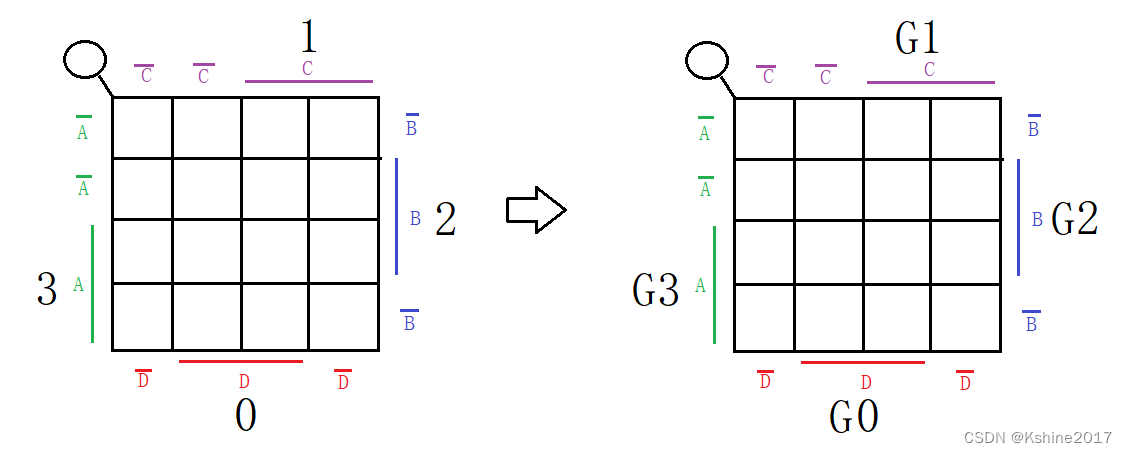

Tipico: codificatore prioritario CD4532 (fuori produzione)

L'encoder prioritario I 7 ha la priorità più alta e I 0 ha la priorità più bassa. L'encoder prioritario I_7 ha la priorità più alta e I_0 ha la priorità più bassa.codificatore prioritarioIOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOO7massima priorità,IOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOO0La priorità più bassa.

Quando EI=1, quando tutti gli ingressi sono di livello basso, nopriorità più bassa Ingresso di livello alto e uscita 000 in questo momento. In questo momento EO=1.

Solo quando EI=1 e tutti gli ingressi sono 0, EO=1. Dedicato all'EI in cascata con un altro dispositivo.

Quando EI=1, almeno uno dei terminali di ingresso è di livello alto 1 e GS=1.

Fare riferimento al libro per espressioni logiche specifiche e diagrammi a blocchi logici.

| EI consente la codifica EI consente la codificaEIOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOCodifica consentita | Io 7 Io_7IOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOO7 | Io 6 Io_6IOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOO6 | Io 5 Io_5IOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOO5 | Io 4 io_4IOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOO4 | Io 3 Io_3IOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOO3 | Io 2 io_2IOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOO2 | Io 1 Io_1IOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOO1 | Io 0 io_0IOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOO0 | E 2 E_2E2 | E 1 E_1E1 | E 0 E_0E0 | GS ha l'ingresso 1 GS ha l'ingresso 1GSC'è input1 | EO inserisce tutti gli 0 EO inserisce tutti gli 0EOInserisci tutto0 | |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 0 | X | X | X | X | X | X | X | X | 0 | 0 | 0 | 0 | 0 | |

| 1 | 1 | X | X | X | X | X | X | X | 1 | 1 | 1 | 1 | 0 | |

| 1 | 0 | 1 | X | X | X | X | X | X | 1 | 1 | 0 | 1 | 0 | |

| 1 | 0 | 0 | 1 | X | X | X | X | X | 1 | 0 | 1 | 1 | 0 | |

| 1 | 0 | 0 | 0 | 1 | X | X | X | X | 1 | 0 | 0 | 1 | 0 | |

| 1 | 0 | 0 | 0 | 0 | 1 | X | X | X | 0 | 1 | 1 | 1 | 0 | |

| 1 | 0 | 0 | 0 | 0 | 0 | 1 | X | X | 0 | 1 | 0 | 1 | 0 | |

| 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | X | 0 | 0 | 1 | 1 | 0 | |

| 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 1 | 0 | |

| 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 |

Quando EI 1 = 0, la sezione 1 è disabilitata. Y 2 Y 1 Y 0 = = 000 , GS 1 = 0 , EO 1 = 0 . EI 0 = 0, anche il chip 0 è disabilitato. Quando EI_1=0, la sezione 1 è disabilitata. Y_2Y_1Y_0==000, GS_1=0, EO_1=0. EI_0=0, anche la sezione 0 è disabilitata.QuandoEIOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOO1=0tempo, pellicola1Disabilitato.E2E1E0==000,GS1=0,ELo1=0。EIOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOO0=0,pezzo0Anche disabilitato.

Quando EI 1 = 1, è possibile codificare la fetta 1. Se I 15 − I 8 = 000...000, allora EO 1 = 1, quindi EI 0 = 1. La porzione 0 consente la codifica. Si può vedere che la codifica della sezione 1 ha una priorità più alta rispetto alla codifica della sezione 0. Quando EI_1=1, la codifica della sezione 1 è consentita Se I_{15} - I_8 = 000...000, allora EO_1= 1, quindi EI_0=1. La porzione 0 consente la codifica.Si può vedere che la priorità della codifica della porzione 1 è maggiore di quella della codifica della porzione 0.QuandoEIOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOO1=1tempo, pellicola1La codifica è consentita seIOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOO15−IOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOO8=000...000,in questo momentoELo1=1,in tal modoEIOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOO0=1 .pezzo0 La codifica è consentita.Si può vedere che il film1La codifica ha la priorità sulle porzioni0codifica。

Quando EI 1 = 1, la codifica è consentita sulla sezione 1. Se I 15 − I 8 ha almeno un 1, allora EO 1 = 0, quindi EI 0 = 0, e la codifica è vietata sulla sezione 0. Quando EI_1=1, la codifica è consentita sulla porzione 1. Se I_{15} - I_8 ha almeno un 1, allora EO_1=0, quindi EI_0=0, la codifica è vietata sulla porzione 0.QuandoEIOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOO1=1tempo, pellicola1La codifica è consentita seIOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOO15−IOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOO8almeno una1,in questo momentoELo1=0,in tal modoEIOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOO0=0,pezzo0La codifica è vietata.

| EI 1 consente la codifica EI_1 consente la codificaEIOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOO1Codifica consentita | EI 0 consente la codifica EI_0 consente la codificaEIOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOO0Codifica consentita | Io 15 io_{15}IOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOO15 | Io 14 Io_{14}IOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOO14 | Io 13 Io_{13}IOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOO13 | Io 12 Io_{12}IOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOO12 | Io 11 Io_{11}IOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOO11 | Io 10 io_{10}IOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOO10 | Io 9 Io_{9}IOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOO9 | Io 8 Io_8IOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOO8 | Io 7 Io_7IOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOO7 | Io 6 Io_6IOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOO6 | Io 5 Io_5IOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOO5 | Io 4 io_4IOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOO4 | Io 3 Io_3IOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOO3 | Io 2 io_2IOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOO2 | Io 1 Io_1IOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOO1 | Io 0 io_0IOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOO0 | E 2 1 E 2_1E21 | E 1 1 E1_1E11 | E 0 1 E0_1E01 | E 2 0 E 2_0E20 | E 1 0 E1_0E10 | E 0 0 E0_0E00 | EO 1 Immettere tutti gli 0 EO_1 Immettere tutti gli 0ELo1Inserisci tutto0 | EO 0 Immettere tutti gli 0 EO_0 Immettere tutti gli 0ELo0Inserisci tutto0 | GS 1 ha l'ingresso 1 GS_1 ha l'ingresso 1GS1C'è input1 | GS 0 ha ingresso 0 GS_0 ha ingresso 0GS0C'è input0 | L3 L_3L3 | L 2 L_2L2 | L 1 L_1L1 | L 0 L_0L0 | |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 0 (fetta 1 disabilitata) | EI 0 = EO 1 = 0 EI_0=EO_1=0EIOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOO0=ELo1=0(disabilitato sulla sezione 0) | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | |

| 1 | 0 | 1 | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 1 (il Chip 1 ha input) | 0 | 1 L3 = GS1 L_3 =GS_1L3=GS1 | 1 L2 = Y21 L_2 =Y2_1L2=E21 | 1 L1 = Y11 L_1 =Y1_1L1=E11 | 1 L 0 = Y 0 1 L_0 =Y0_1L0=E01 | |

| 1 | 0 | 0 | 1 | X | X | X | X | X | X | X | X | X | X | X | X | X | X | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 1 | 1 | 1 | 0 | |

| 1 | 0 | 0 | 0 | 1 | X | X | X | X | X | X | X | X | X | X | X | X | X | 1 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 1 | 1 | 0 | 1 | |

| 1 | 0 | 0 | 0 | 0 | 1 | X | X | X | X | X | X | X | X | X | X | X | X | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 1 | 1 | 0 | 0 | |

| 1 | 0 | 0 | 0 | 0 | 0 | 1 | X | X | X | X | X | X | X | X | X | X | X | 0 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 1 | 0 | 1 | 1 | |

| 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | X | X | X | X | X | X | X | X | X | X | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | |

| 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | X | X | X | X | X | X | X | X | X | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 1 | 0 | 0 | 1 | |

| 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | X | X | X | X | X | X | X | X | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 1 | 0 | 0 | 0 | |

| 1 | EI 0 = EO 1 = 1 EI_0=EO_1=1EIOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOOO0=ELo1=1(pezzo 0 lavoro) | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | X | X | X | X | X | X | X | 0 | 0 | 0 | 1 | 1 | 1 | 1 (l'ingresso del chip 1 è tutto 0) | 0 | 0 (codifica non valida per la sezione 1) | 1 | 0 L3 = GS1 L_3 =GS_1L3=GS1 | 1 L2 = Y20 L_2 =Y2_0L2=E20 | 1 L1 = Y10 L_1 =Y1_0L1=E10 | 1 L 0 = Y 0 0 L_0 =Y0_0L0=E00 | |

| 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | X | X | X | X | X | X | 0 | 0 | 0 | 1 | 1 | 0 | 1 | 0 | 0 | 1 | 0 | 1 | 1 | 0 | |

| 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | X | X | X | X | X | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 0 | 1 | 0 | 1 | 0 | 1 | |

| 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | X | X | X | X | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 0 | 1 | 0 | 1 | 0 | 0 | |

| 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | X | X | X | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 0 | 1 | 0 | 0 | 1 | 1 | |

| 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | X | X | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 0 | 1 | 0 | 0 | 1 | 0 | |

| 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | X | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 1 | |

| 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | |

| 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 (l'ingresso del chip 0 è tutto 0) | 0 | 0 (codifica della porzione 0 non valida) | 0 | 0 | 0 | 0 |

| accedere | produzione | |||||

| /E | A_1 | Un_0 | /Y_3 | /Y_2 | /Y_1 | /Y_0 |

| 1 proibito | X | X | 1 | 1 | 1 | 1 |

| 0 abilitato | 0 | 0 | 1 | 1 | 1 | 0 basso attivo |

| 0 abilitato | 0 | 1 | 1 | 1 | 0 basso efficace | 1 |

| 0 abilitato | 1 | 0 | 1 | 0 basso attivo | 1 | 1 |

| 0 abilitato | 1 | 1 | 0 basso attivo | 1 | 1 | 1 |

Y 0 ‾ = E ‾ ‾ ⋅ A 1 ‾ ⋅ A 0 ‾ ‾ sopraline{Y_0} = sopraline{sopraline{sopraline{E}}·sopraline{A_1}·sopraline{A_0}}E0=E⋅UN1⋅UN0 //00

Y 1 ‾ = E ‾ ‾ ⋅ A 1 ‾ ⋅ A 0 ‾ sopraline{Y_1} = sopraline{sopraline{sopraline{E}}·sopraline{A_1}·A_0}E1=E⋅UN1⋅UN0 //01

Y 2 ‾ = E ‾ ‾ ⋅ A 1 ⋅ A 0 ‾ ‾ sopraline{Y_2} = sopraline{sopraline{sopraline{E}}·A_1·sopraline{A_0}}E2=E⋅UN1⋅UN0 //10

Y 3 ‾ = E ‾ ‾ ⋅ A 1 ⋅ A 0 ‾ sopraline{Y_3} = sopraline{sopraline{sopraline{E}}·A_1·A_0}E3=E⋅UN1⋅UN0 //11

Y 0 ‾ = E 3 ⋅ E 2 ‾ ‾ ⋅ E 1 ‾ ‾ ⋅ A 2 ‾ ⋅ A 1 ‾ ⋅ A 0 ‾ ‾ sopraline{Y_0} = sopraline{E_3·sopraline{sopraline{E_2}}·sopraline{sopraline{E_1}}·sopraline{A_2}·sopraline{A_1}·sopraline{A_0}}E0=E3⋅E2⋅E1⋅UN2⋅UN1⋅UN0 //000

Y 1 ‾ = E 3 ⋅ E 2 ‾ ‾ ⋅ E 1 ‾ ‾ ⋅ A 2 ‾ ⋅ A 1 ‾ ⋅ A 0 ‾ sopraline{Y_1} = sopraline{E_3·sopraline{sopraline{E_2}}·sopraline{sopraline{E_1}}·sopraline{A_2}·sopraline{A_1}·A_0}E1=E3⋅E2⋅E1⋅UN2⋅UN1⋅UN0 //001

Y 2 ‾ = E 3 ⋅ E 2 ‾ ‾ ⋅ E 1 ‾ ‾ ⋅ A 2 ‾ ⋅ A 1 ⋅ A 0 ‾ ‾ sopraline{Y_2} = sopraline{E_3·sopraline{sopraline{E_2}}·sopraline{sopraline{E_1}}·sopraline{A_2}·A_1·sopraline{A_0}}E2=E3⋅E2⋅E1⋅UN2⋅UN1⋅UN0 //010

Y 3 ‾ = E 3 ⋅ E 2 ‾ ‾ ⋅ E 1 ‾ ‾ ⋅ A 2 ‾ ⋅ A 1 ⋅ A 0 ‾ sopraline{Y_3} = sopraline{E_3·sopraline{sopraline{E_2}}·sopraline{sopraline{E_1}}·sopraline{A_2}·A_1·A_0}E3=E3⋅E2⋅E1⋅UN2⋅UN1⋅UN0 //011

Y 4 ‾ = E 3 ⋅ E 2 ‾ ‾ ⋅ E 1 ‾ ‾ ⋅ A 2 ⋅ A 1 ‾ ⋅ A 0 ‾ ‾ sopraline{Y_4} = sopraline{E_3·sopraline{sopraline{E_2}}·sopraline{sopraline{E_1}}·A_2·sopraline{A_1}·sopraline{A_0}}E4=E3⋅E2⋅E1⋅UN2⋅UN1⋅UN0 //100

Y 5 ‾ = E 3 ⋅ E 2 ‾ ‾ ⋅ E 1 ‾ ‾ ⋅ A 2 ⋅ A 1 ‾ ⋅ A 0 ‾ sopraline{Y_5} = sopraline{E_3·sopraline{sopraline{E_2}}·sopraline{sopraline{E_1}}·A_2·sopraline{A_1}·A_0}E5=E3⋅E2⋅E1⋅UN2⋅UN1⋅UN0 //101

Y 6 ‾ = E 3 ⋅ E 2 ‾ ‾ ⋅ E 1 ‾ ‾ ⋅ A 2 ⋅ A 1 ⋅ A 0 ‾ ‾ sopraline{Y_6} = sopraline{E_3·sopraline{sopraline{E_2}}·sopraline{sopraline{E_1}}·A_2·A_1·sopraline{A_0}}E6=E3⋅E2⋅E1⋅UN2⋅UN1⋅UN0 //110

Y 7 ‾ = E 3 ⋅ E 2 ‾ ‾ ⋅ E 1 ‾ ‾ ⋅ A 2 ⋅ A 1 ⋅ A 0 ‾ sopraline{Y_7} = sopraline{E_3·sopraline{sopraline{E_2}}·sopraline{sopraline{E_1}}·A_2·A_1·A_0}E7=E3⋅E2⋅E1⋅UN2⋅UN1⋅UN0 //111

L = A ‾ ⋅ C ‾ + A ⋅ B = A ‾ ⋅ B ‾ ⋅ C ‾ + A ‾ ⋅ B ⋅ C ‾ + A ⋅ B ⋅ C ‾ + ABC = m 0 + m 2 + m 6 + m 7 L=sopralinea{A}·sopralinea{C}+A·B =sopralinea{A}·sopralinea{B}·sopralinea{C}+sopralinea{A}·B·sopralinea{C} + A·B·sopralinea{C}+ABC = m_0+m_2+m_6+m_7L=UN⋅C+UN⋅B=UN⋅B⋅C+UN⋅B⋅C+UN⋅B⋅C+UNAVANTI CRISTO=M0+M2+M6+M7

Y 0 ‾ = E 3 ⋅ E 2 ‾ ‾ ⋅ E 1 ‾ ‾ ⋅ A 2 ‾ ⋅ A 1 ‾ ⋅ A 0 ‾ ‾ = E 3 ⋅ E 2 ‾ ‾ ⋅ E 1 ‾ ‾ ⋅ m 0 ‾ sopraline{Y_0} = sopraline{E_3·sopraline{sopraline{E_2}}·sopraline{sopraline{E_1}}·sopraline{A_2}·sopraline{A_1}·sopraline{A_0}} = sopraline{E_3·sopraline{sopraline{E_2}}·sopraline{sopraline{E_1}}·m_0}E0=E3⋅E2⋅E1⋅UN2⋅UN1⋅UN0=E3⋅E2⋅E1⋅M0 //000

Y 1 ‾ = E 3 ⋅ E 2 ‾ ‾ ⋅ E 1 ‾ ‾ ⋅ A 2 ‾ ⋅ A 1 ‾ ⋅ A 0 ‾ = E 3 ⋅ E 2 ‾ ‾ ⋅ E 1 ‾ ‾ ⋅ m 1 ‾ sopraline{Y_1} = sopraline{E_3·sopraline{sopraline{E_2}}·sopraline{sopraline{E_1}}·sopraline{A_2}·sopraline{A_1}·A_0} = sopraline{E_3·sopraline{sopraline{E_2}}·sopraline{sopraline{E_1}}·m_1}E1=E3⋅E2⋅E1⋅UN2⋅UN1⋅UN0=E3⋅E2⋅E1⋅M1 //001

Y 2 ‾ = E 3 ⋅ E 2 ‾ ‾ ⋅ E 1 ‾ ‾ ⋅ A 2 ‾ ⋅ A 1 ⋅ A 0 ‾ ‾ = E 3 ⋅ E 2 ‾ ‾ ⋅ E 1 ‾ ‾ ⋅ m 2 ‾ sopraline{Y_2} = sopraline{E_3·sopraline{sopraline{E_2}}·sopraline{sopraline{E_1}}·sopraline{A_2}·A_1·sopraline{A_0}}= sopraline{E_3·sopraline{sopraline{E_2}}·sopraline{sopraline{E_1}}·m_2}E2=E3⋅E2⋅E1⋅UN2⋅UN1⋅UN0=E3⋅E2⋅E1⋅M2 //010

Y 3 ‾ = E 3 ⋅ E 2 ‾ ‾ ⋅ E 1 ‾ ‾ ⋅ A 2 ‾ ⋅ A 1 ⋅ A 0 ‾ = E 3 ⋅ E 2 ‾ ‾ ⋅ E 1 ‾ ‾ ⋅ m 3 ‾ sopraline{Y_3} = sopraline{E_3·sopraline{sopraline{E_2}}·sopraline{sopraline{E_1}}·sopraline{A_2}·A_1·A_0}= sopraline{E_3·sopraline{sopraline{E_2}}·sopraline{sopraline{E_1}}·m_3}E3=E3⋅E2⋅E1⋅UN2⋅UN1⋅UN0=E3⋅E2⋅E1⋅M3 //011

Y 4 ‾ = E 3 ⋅ E 2 ‾ ‾ ⋅ E 1 ‾ ‾ ⋅ A 2 ⋅ A 1 ‾ ⋅ A 0 ‾ ‾ = E 3 ⋅ E 2 ‾ ‾ ⋅ E 1 ‾ ‾ ⋅ m 4 ‾ sopraline{Y_4} = sopraline{E_3·sopraline{sopraline{E_2}}·sopraline{sopraline{E_1}}·A_2·sopraline{A_1}·sopraline{A_0}}= sopraline{E_3·sopraline{sopraline{E_2}}·sopraline{sopraline{E_1}}·m_4}E4=E3⋅E2⋅E1⋅UN2⋅UN1⋅UN0=E3⋅E2⋅E1⋅M4 //100

Y 5 ‾ = E 3 ⋅ E 2 ‾ ‾ ⋅ E 1 ‾ ‾ ⋅ A 2 ⋅ A 1 ‾ ⋅ A 0 ‾ = E 3 ⋅ E 2 ‾ ‾ ⋅ E 1 ‾ ‾ ⋅ m 5 ‾ sopraline{Y_5} = sopraline{E_3·sopraline{sopraline{E_2}}·sopraline{sopraline{E_1}}·A_2·sopraline{A_1}·A_0}= sopraline{E_3·sopraline{sopraline{E_2}}·sopraline{sopraline{E_1}}·m_5}E5=E3⋅E2⋅E1⋅UN2⋅UN1⋅UN0=E3⋅E2⋅E1⋅M5 //101

Y 6 ‾ = E 3 ⋅ E 2 ‾ ‾ ⋅ E 1 ‾ ‾ ⋅ A 2 ⋅ A 1 ⋅ A 0 ‾ ‾ = E 3 ⋅ E 2 ‾ ‾ ⋅ E 1 ‾ ‾ ⋅ m 6 ‾ sopraline{Y_6} = sopraline{E_3·sopraline{sopraline{E_2}}·sopraline{sopraline{E_1}}·A_2·A_1·sopraline{A_0}}= sopraline{E_3·sopraline{sopraline{E_2}}·sopraline{sopraline{E_1}}·m_6}E6=E3⋅E2⋅E1⋅UN2⋅UN1⋅UN0=E3⋅E2⋅E1⋅M6 //110

Y 7 ‾ = E 3 ⋅ E 2 ‾ ‾ ⋅ E 1 ‾ ‾ ⋅ A 2 ⋅ A 1 ⋅ A 0 ‾ = E 3 ⋅ E 2 ‾ ‾ ⋅ E 1 ‾ ‾ ⋅ m 7 ‾ sopraline{Y_7} = sopraline{E_3·sopraline{sopraline{E_2}}·sopraline{sopraline{E_1}}·A_2·A_1·A_0}= sopraline{E_3·sopraline{sopraline{E_2}}·sopraline{sopraline{E_1}}·m_7}E7=E3⋅E2⋅E1⋅UN2⋅UN1⋅UN0=E3⋅E2⋅E1⋅M7 //111

Assicurati che E 3 = 1, E 2 = 0, E 1 = 0 Assicurati che E_3=1,E_2=0,E_1=0assicurarsiE3=1,E2=0,E1=0, vale a dire Y 0 ‾ = m 0 ‾ , Y 2 ‾ = m 2 ‾ , Y 6 ‾ = m 6 ‾ , Y 7 ‾ = m 7 ‾ sopraline{Y_0}=sopraline{m_0},sopraline{Y_2}=sopraline{m_2},sopraline{Y_6}=sopraline{m_6},sopraline{Y_7}=sopraline{m_7}E0=M0,E2=M2,E6=M6,E7=M7。

Trasformare le funzioni logiche secondo la legge di inversione

L = L ‾ ‾ = m 0 + m 2 + m 6 + m 7 ‾ ‾ = m 0 ‾ ⋅ m 2 ‾ ⋅ m 6 ‾ ⋅ m 7 ‾ ‾ = m 0 + m 2 + m 6 + m 7 ‾ ‾ = Y 0 ‾ ⋅ Y 2 ‾ ⋅ Y 6 ‾ ⋅ Y 7 ‾ ‾ L=overline{overline{L}} = overline{overline{m_0+m_2+m_6+m_7}} = overline{overline{m_0}·overline{m_2}·overline{m_6}·overline{m_7}} = sopralinea{sopralinea{m_0+m_2+m_6+m_7}} = sopralinea{sopralinea{Y_0}·sopralinea{Y_2}·sopralinea{Y_6}·sopralinea{Y_7}}L=L=M0+M2+M6+M7=M0⋅M2⋅M6⋅M7=M0+M2+M6+M7=E0⋅E2⋅E6⋅E7

Ottieni il diagramma logico

774HC42

4 ingressi

10 terminali di uscita, l'uscita è attiva a livello basso, corrispondente ai numeri decimali 0~9.

4 terminali di ingresso, per un totale di 16 situazioni

soltanto m 0 , m 1 , m 2 . . . . . m 9 m_0 ,m_1,m_2......m_9M0,M1,M2......M9È un ingresso valido (il pin di uscita corrispondente emette basso 0 e le altre uscite sono alte 1).

Tra i restanti 6 m 10, m 11, m 12... m 15 m_{10}, m_{11}, m_{12}...... m_{15}M10,M11,M12......M15Significa che non esiste un output di decodifica valido (se non valido, l'output è tutto alto 1).

Disegna i diagrammi delle forme d'onda di ingresso e uscita del 74HC42.

Principio di visualizzazione del tubo digitale

Decoder display a sette segmenti integrato. 74HC4511 (catodo comune) (il livello alto si accende)

LE LELEAbilitazione del blocco

LT ‾ sopralineato{LT}LTingresso test lampada quando LT ‾ = 0 sopraline{LT}=0LT=0Quando , ag restituisce tutto 1 e visualizza il carattere "8".

BL ‾ sopralineato{BL}BLIngresso luce spenta, quando LT ‾ = 1, e BL ‾ = 1 sopralineato{LT}=1, e sopralineato{BL}=1LT=1,EBL=1 Quando , ag tutte le uscite 0. Può essere utilizzato per spegnere lo zero "0" non necessario visualizzato.

Il 3 Il 2 Il 1 Il 0 Il_3D_2D_1D_0D3D2D1D0=0000, il corrispondente glifo di uscita "0"

Il 3 Il 2 Il 1 Il 0 Il_3D_2D_1D_0D3D2D1D0=0001, il carattere di output corrispondente "1"

Il 3 Il 2 Il 1 Il 0 Il_3D_2D_1D_0D3D2D1D0=0010, il carattere di output corrispondente "2"

Il 3 Il 2 Il 1 Il 0 Il_3D_2D_1D_0D3D2D1D0=0011, il carattere di output corrispondente "3"

Il 3 Il 2 Il 1 Il 0 Il_3D_2D_1D_0D3D2D1D0=0100, il carattere di output corrispondente "4"

Il 3 Il 2 Il 1 Il 0 Il_3D_2D_1D_0D3D2D1D0=0101, il carattere di output corrispondente "5"

Il 3 Il 2 Il 1 Il 0 Il_3D_2D_1D_0D3D2D1D0=0110, il carattere di output corrispondente "6"

Il 3 Il 2 Il 1 Il 0 Il_3D_2D_1D_0D3D2D1D0=0111, il carattere di output corrispondente "7"

Il 3 Il 2 Il 1 Il 0 Il_3D_2D_1D_0D3D2D1D0=1000, il carattere di output corrispondente "8"

Il 3 Il 2 Il 1 Il 0 Il_3D_2D_1D_0D3D2D1D0=1001, il carattere di output corrispondente "9"

1010-1111, spento

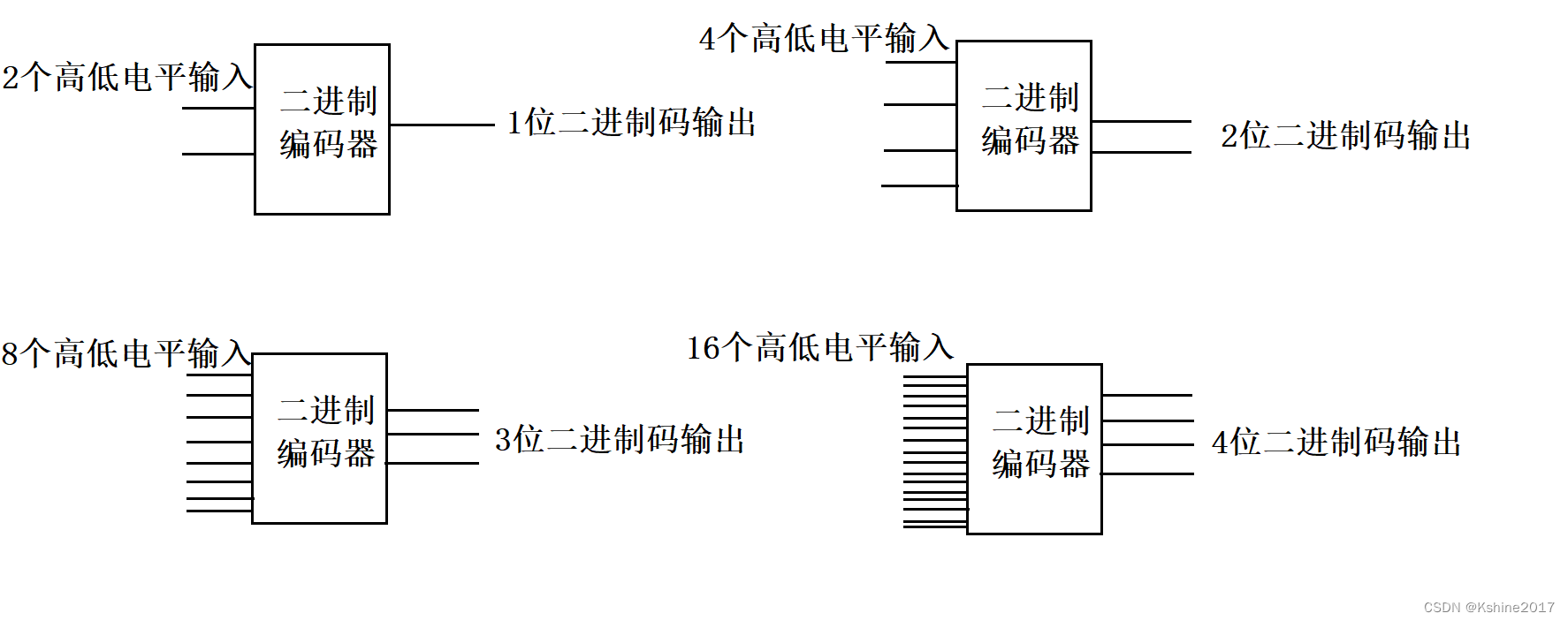

Da uno a molti, i dati sulla linea dati comune vengono inviati a canali diversi secondo necessità.

Simile a "interruttore multicorsa unipolare"

Utilizzando un decodificatore di indirizzi univoci, implementare l'allocatore di dati

Ad esempio, 74x138 integra un decoder da 3 a 8 linee.

E 1 ‾ come input dati sopra linea{E_1} come input datiE1come input di dati

A 0 A 1 A 2 A 3 A 4 A 5 A 6 A 7 A_0 A_1 A_2A_3A_4A_5A_6A_7E0E1E2E3E4E5E6E78 canali come uscita dati

Y 2 ‾ = E 3 ⋅ E 2 ‾ ‾ ⋅ E 1 ‾ ‾ ⋅ A 2 ‾ ⋅ A 1 ⋅ A 0 ‾ ‾ sopraline{Y_2} = sopraline{E_3·sopraline{sopraline{E_2}}·sopraline{sopraline{E_1}}·sopraline{A_2}·A_1·sopraline{A_0}}E2=E3⋅E2⋅E1⋅UN2⋅UN1⋅UN0 //010

Nella foto sopra, E 3 = 1, E 2 ‾ = 0 E_3=1, sopra {E_2}=0E3=1,E2=0, quando la riga dell'indirizzo Un 2 Un 1 Un 0 = 010 Un_2A_1A_0=010UN2UN1UN0=010ora, Y 2 ‾ = E 1 ‾ sopralinea{Y_2}=sopralinea{E_1}E2=E1

Allo stesso modo possiamo concludere:

Quando la riga dell'indirizzo Un 2 Un 1 Un 0 = 000 Un_2A_1A_0=000UN2UN1UN0=000ora, Y 0 ‾ = E 1 ‾ = D sopralinea{Y_0}=sopralinea{E_1}=DE0=E1=D,altro Yx = 1 Y_x=1EX=1。

Quando la riga dell'indirizzo Un 2 Un 1 Un 0 = 001 Un_2Un_1Un_0=001UN2UN1UN0=001ora, Y 1 ‾ = E 1 ‾ = D sopralinea{Y_1}=sopralinea{E_1}=DE1=E1=D,altro Yx = 1 Y_x=1EX=1。

Quando la riga dell'indirizzo Un 2 Un 1 Un 0 = 010 Un_2A_1A_0=010UN2UN1UN0=010ora, Y 2 ‾ = E 1 ‾ = D sopralinea{Y_2}=sopralinea{E_1}=DE2=E1=D,altro Yx = 1 Y_x=1EX=1。

Quando la riga dell'indirizzo Un 2 Un 1 Un 0 = 011 Un_2Un_1Un_0=011UN2UN1UN0=011ora, Y 3 ‾ = E 1 ‾ = D sopralinea{Y_3}=sopralinea{E_1}=DE3=E1=D,altro Yx = 1 Y_x=1EX=1。

Quando la riga dell'indirizzo Un 2 Un 1 Un 0 = 100 Un_2Un_1Un_0=100UN2UN1UN0=100ora, Y 4 ‾ = E 1 ‾ = D sopralinea{Y_4}=sopralinea{E_1}=DE4=E1=D,altro Yx = 1 Y_x=1EX=1。

Quando la riga dell'indirizzo Un 2 Un 1 Un 0 = 101 Un_2Un_1Un_0=101UN2UN1UN0=101ora, Y 5 ‾ = E 1 ‾ = D sopralinea{Y_5}=sopralinea{E_1}=DE5=E1=D,altro Yx = 1 Y_x=1EX=1。

Quando la riga dell'indirizzo Un 2 Un 1 Un 0 = 110 Un_2A_1A_0=110UN2UN1UN0=110ora, Y 6 ‾ = E 1 ‾ = D sopralinea{Y_6}=sopralinea{E_1}=DE6=E1=D,altro Yx = 1 Y_x=1EX=1。

Quando la riga dell'indirizzo Un 2 Un 1 Un 0 = 111 Un_2Un_1Un_0=111UN2UN1UN0=111ora, Y 7 ‾ = E 1 ‾ = D sopralinea{Y_7}=sopralinea{E_1}=DE7=E1=D,altro Yx = 1 Y_x=1EX=1。

Y = S 2 ‾ ⋅ S 1 ‾ ⋅ S 0 ‾ ⋅ D 0 + S 2 ‾ ⋅ S 1 ‾ ⋅ S 0 ⋅ D 1 + S 2 ‾ ⋅ S 1 ⋅ S 0 ‾ ⋅ D 2 + S 2 ‾ ⋅ S 1 ⋅ S 0 ⋅ D 3 + S 2 ⋅ S 1 ‾ ⋅ S 0 ‾ ⋅ D 4 + S 2 ⋅ S 1 ‾ ⋅ S 0 ⋅ D 5 + S 2 ⋅ S 1 ⋅ S 0 ‾ ⋅ D 6 + S 2 ⋅ S 1 ⋅ S 0 ⋅ D 7 Y=sopralinea{S_2}·sopralinea{S_1}·sopralinea{S_0}·D_0 +sopralinea{S_2}·sopralinea{S_1}·S_0·D_1 +sopralinea{S_2}·S_1·sopralinea{S_0}·D_2 +sopralinea{S_2}·S_1·S_0·D_3 +S_2·sopralinea{S_1}·sopralinea{S_0}·D_4 +S_2·sopralinea{S_1}·S_0·D_5 +S_2·S_1·sopralinea{S_0}·D_6 +S_2·S_1·S_0·D_7E=S2⋅S1⋅S0⋅D0+S2⋅S1⋅S0⋅D1+S2⋅S1⋅S0⋅D2+S2⋅S1⋅S0⋅D3+S2⋅S1⋅S0⋅D4+S2⋅S1⋅S0⋅D5+S2⋅S1⋅S0⋅D6+S2⋅S1⋅S0⋅D7

Estensioni per selettori di dati.

generatore di funzioni logiche

Selettore dati noto, 8 a 1.

Y = S 2 ‾ ⋅ S 1 ‾ ⋅ S 0 ‾ ⋅ D 0 + S 2 ‾ ⋅ S 1 ‾ ⋅ S 0 ⋅ D 1 + S 2 ‾ ⋅ S 1 ⋅ S 0 ‾ ⋅ D 2 + S 2 ‾ ⋅ S 1 ⋅ S 0 ⋅ D 3 + S 2 ⋅ S 1 ‾ ⋅ S 0 ‾ ⋅ D 4 + S 2 ⋅ S 1 ‾ ⋅ S 0 ⋅ D 5 + S 2 ⋅ S 1 ⋅ S 0 ‾ ⋅ D 6 + S 2 ⋅ S 1 ⋅ S 0 ⋅ D 7 Y=sopralinea{S_2}·sopralinea{S_1}·sopralinea{S_0}·D_0 +sopralinea{S_2}·sopralinea{S_1}·S_0·D_1 +sopralinea{S_2}·S_1·sopralinea{S_0}·D_2 +sopralinea{S_2}·S_1·S_0·D_3 +S_2·sopralinea{S_1}·sopralinea{S_0}·D_4 +S_2·sopralinea{S_1}·S_0·D_5 +S_2·S_1·sopralinea{S_0}·D_6 +S_2·S_1·S_0·D_7E=S2⋅S1⋅S0⋅D0+S2⋅S1⋅S0⋅D1+S2⋅S1⋅S0⋅D2+S2⋅S1⋅S0⋅D3+S2⋅S1⋅S0⋅D4+S2⋅S1⋅S0⋅D5+S2⋅S1⋅S0⋅D6+S2⋅S1⋅S0⋅D7

Y = m 0 ⋅ D 0 + m 1 ⋅ D 1 + m 2 ⋅ D 2 + m 3 ⋅ D 3 + m 4 ⋅ D 4 + m 5 ⋅ D 5 + m 6 ⋅ D 6 + m 7 ⋅ D 7 Y=m_0·D_0 +m_1·D_1 +m_2·D_2 +m_3·D_3 +m_4·D_4 +m_5·D_5 +m_6·D_6 +m_7·D_7E=M0⋅D0+M1⋅D1+M2⋅D2+M3⋅D3+M4⋅D4+M5⋅D5+M6⋅D6+M7⋅D7

funzione logica L = A ‾ BC + AB ‾ C + ABL=overline{A}BC+Aoverline{B}C+ABL=UNAVANTI CRISTO+UNBC+UNB

L = A ‾ BC + AB ‾ C + AB = A ‾ BC + AB ‾ C + ABC ‾ + ABC = m 3 + m 5 + m 6 + m 7 L=overline{A}BC+Aoverline{B}C+AB=overline{A}BC+Aoverline{B}C+ABoverline{C}+ABC=m_3+m_5+m_6+m_7L=UNAVANTI CRISTO+UNBC+UNB=UNAVANTI CRISTO+UNBC+UNBC+UNAVANTI CRISTO=M3+M5+M6+M7

Utilizzare il selettore dati 8 a 1 per implementare la funzione L di cui sopra

L = Y = m 3 + m 5 + m 6 + m 7 , dove D 7 D 6 D 5 D 3 = 1111 , D 4 D 2 D 1 D 0 = 0000 L=Y=m_3+m_5+m_6+m_7, Tra questi D_7D_6D_5D_3=1111, D_4D_2D_1D_0=0000L=E=M3+M5+M6+M7,InD7D6D5D3=1111,D4D2D1D0=0000

Dati paralleli a dati seriali

| UN | B | FA > B F_{A>B}FUN>B | FA < B F_{AFUN<B | FA = = B F_{A==B}FUN==B |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 1 |

| 0 | 1 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 0 |

| 1 | 1 | 0 | 0 | 1 |

| Un 1? B 1 Un _1? B_1UN1?B1 | Un 0? Un 0 A_0?B_0UN0?B0 | FA > B F_{A>B}FUN>B | FA < B F_{AFUN<B | FA = = B F_{A==B}FUN==B |

|---|---|---|---|---|

| Un 1 > B 1 Un_1>B_1UN1>B1 | X | 1 | 0 | 0 |

| Un 1 < B 1 Un_1UN1<B1 | X | 0 | 1 | 0 |

| Un 1 = = B 1 Un_1==B_1UN1==B1 | Un 0 > B 0 Un_0>B_0UN0>B0 | 1 | 0 | 0 |

| Un 1 = = B 1 Un_1==B_1UN1==B1 | Un 0 < B 0 Un_0UN0<B0 | 0 | 1 | 0 |

| Un 1 = = B 1 Un_1==B_1UN1==B1 | Un 0 = = B 0 Un_0==B_0UN0==B0 | 0 | 0 | 1 |

espressione logica

FA > B = FA 1 > B 1 + FA 1 = = B 1 ⋅ FA 0 > B 0 F_{A>B} = F_{A_1>B_1} +F_{A_1==B_1}·F_{A_0>B_0}FUN>B=FUN1>B1+FUN1==B1⋅FUN0>B0

FA < B = FA 1 < B 1 + FA 1 = = B 1 ⋅ FA 0 < B 0 F_{AFUN<B=FUN1<B1+FUN1==B1⋅FUN0<B0

FA = = B = FA 1 = = B 1 ⋅ FA 0 = = B 0 F_{A==B} = F_{A_1==B_1}·F_{A_0==B_0}FUN==B=FUN1==B1⋅FUN0==B0

diagramma logico

Collegamento in serie, ampliato al comparatore numerico a 8 bit

Connessione parallela, estesa al comparatore numerico a 16 bit.

Quando collegato in parallelo, la velocità è elevata.