내 연락처 정보

우편메소피아@프로톤메일.com

2024-07-12

한어Русский языкEnglishFrançaisIndonesianSanskrit日本語DeutschPortuguêsΕλληνικάespañolItalianoSuomalainenLatina

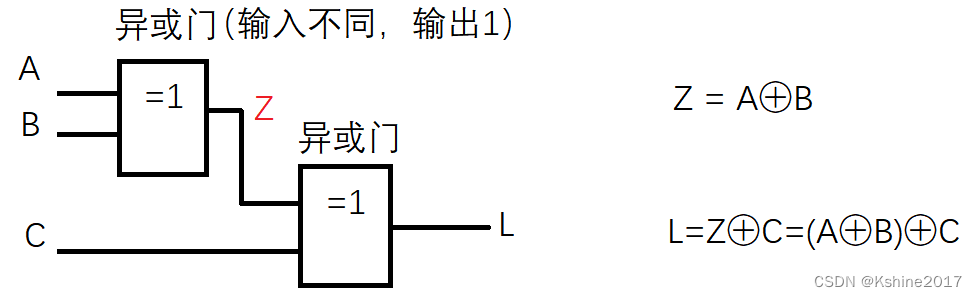

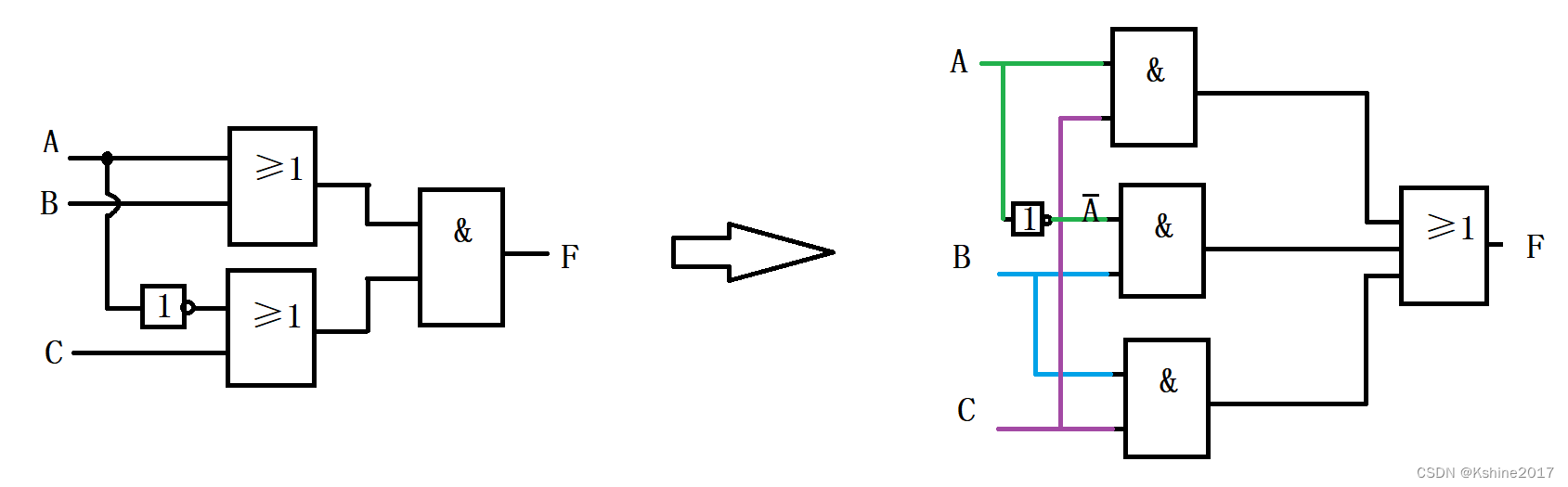

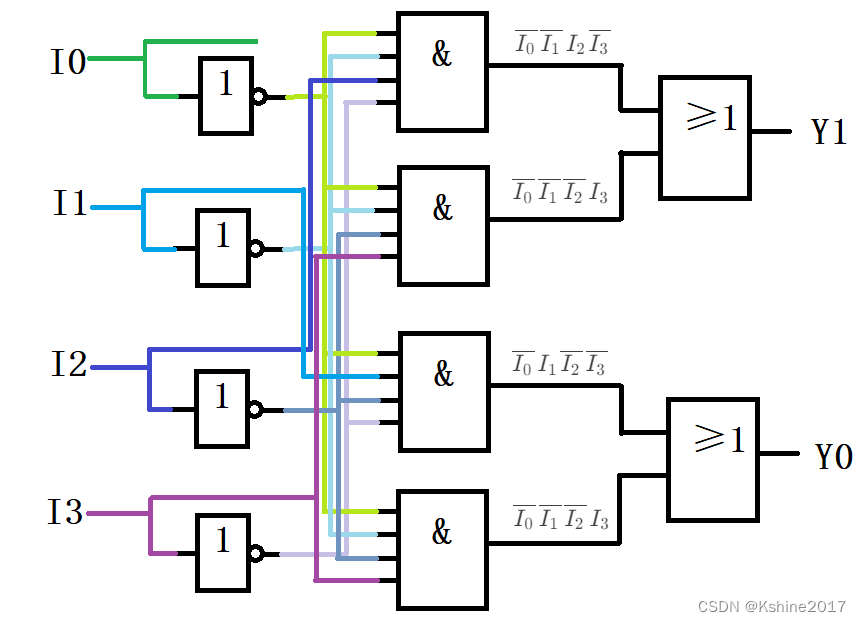

(1) 아래 그림과 같습니다.

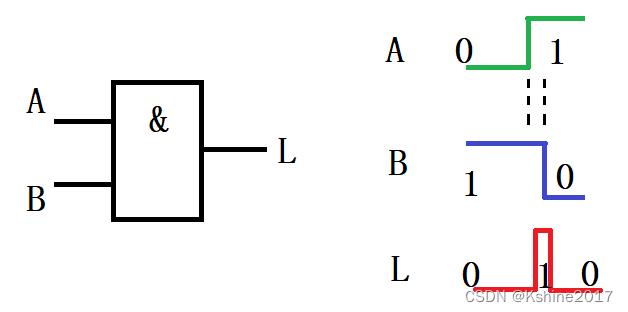

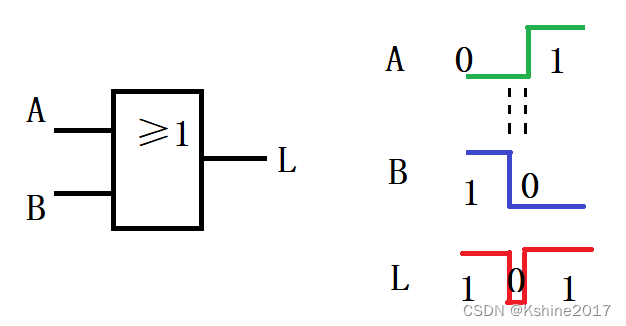

(2) 진리표를 나열하라

| ㅏ | 비 | 씨 | 지 | 엘 |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 | 1 |

| 0 | 1 | 0 | 1 | 1 |

| 0 | 1 | 1 | 1 | 0 |

| 1 | 0 | 0 | 1 | 1 |

| 1 | 0 | 1 | 1 | 0 |

| 1 | 1 | 0 | 0 | 0 |

| 1 | 1 | 1 | 0 | 1 |

(3) 분석하다홀수 패리티 회로기능.

(1) 홀수 패리티 회로를 기반으로 출력단에 인버터를 추가하면 다음을 얻을 수 있습니다.짝수 패리티 회로。

| ㅏ | 비 | 씨 | 엑스 | 와이 | 지 |

|---|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 | 0 | 1 |

| 0 | 1 | 0 | 0 | 1 | 0 |

| 0 | 1 | 1 | 0 | 1 | 1 |

| 1 | 0 | 0 | 1 | 1 | 1 |

| 1 | 0 | 1 | 1 | 1 | 0 |

| 1 | 1 | 0 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 | 0 | 0 |

필요.

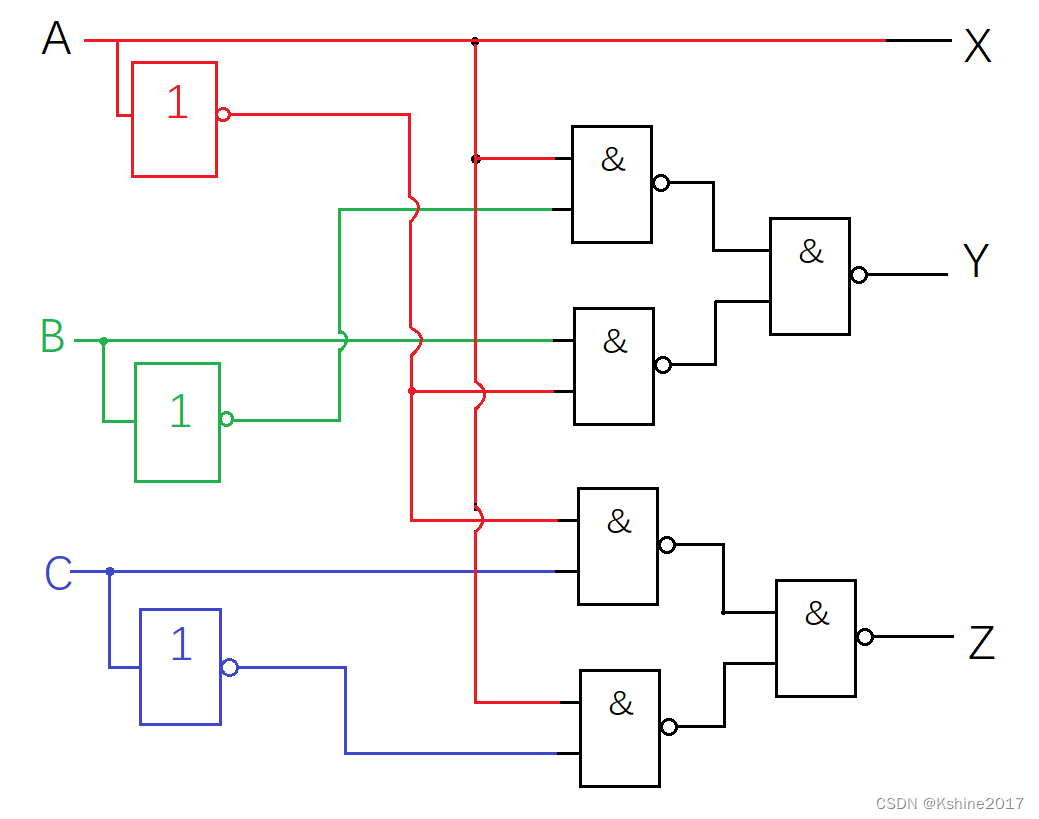

(1) 2개의 입력을 사용한다낸드 게이트,인버터.

(2) 1번 지시등, 급행열차 도착 지시등. 우선순위가 높습니다.

(3) 2번 지시등, 역 지시등에 진입하는 직행열차. 우선적으로.

(4) 3번 지시등, 역 지시등에 진입하는 느린 열차. 낮은 우선 순위.

(5) 동시에 최대 하나의 표시등이 켜질 수 있습니다.

입력 및 출력 변수를 정의합니다.

(1) 입력 신호, I 0 급행 요청, I 1 직행 급행 요청, I 2 완행 열차 요청 I_0 급행 요청, I_1 직행 급행 요청, I_2 완행 열차 요청나0명시적인 요청,나1빨리 요청해 보세요.나2느린 열차 요청 . 1은 인바운드 요청이 있음을 의미하고, 0은 인바운드 요청이 없음을 의미합니다.

(2) 출력 신호, L 0 급행 정지 지시등, L 1 직행 급행 정지 지시등, L 2 완행 열차 정류장 지시등 L_0 급행 정지 지시등, L_1 직행 급행 정지 지시등, L_2 보통 열차 정차 지시등엘0익스프레스 도착 빛,엘1직접 정지 표시 등,엘2느린 열차 도착 표시등 . 1은 표시등이 켜져 있음을 의미하고, 0은 표시등이 꺼져 있음을 의미합니다.

진실표.

| 입력하다 | 산출 | ||||

| 나_0 | 나_1 | 나_2 | 엘_0 | 엘_1 | L_2 |

| 0 | 0 | 0 | 0 | 0 | 0 |

| 1 | 엑스 | 엑스 | 1 | 0 | 0 |

| 0 | 1 | 엑스 | 0 | 1 | 0 |

| 0 | 0 | 1 | 0 | 0 | 1 |

논리식 나열

L 0 = I 0 L_0 = I_0엘0=나0

L 1 = I 0 ⋅ I 1 L_1 = 윗줄{I_0}·I_1엘1=나0⋅나1

L 2 = I 0 ⋅ I 1 ⋅ I 2 L_2 = 윗줄{I_0}·윗줄{I_1}·I_2엘2=나0⋅나1⋅나2

필요에 따라 NAND 형식으로 변환합니다.

L 0 = I 0 L_0 = I_0엘0=나0

L 1 = I 0 ‾ ⋅ I 1 ‾ ‾ L_1 = 윗줄{윗줄{윗줄{I_0}·I_1}}엘1=나0⋅나1

L 2 = I 0 ⋅ I 1 ⋅ I 2 ⋅ ‾ ‾ L_2 =윗줄{윗줄{윗줄{윗줄{윗줄{I_0}·윗줄{I_1}}}·I_2}}엘2=나0⋅나1⋅나2

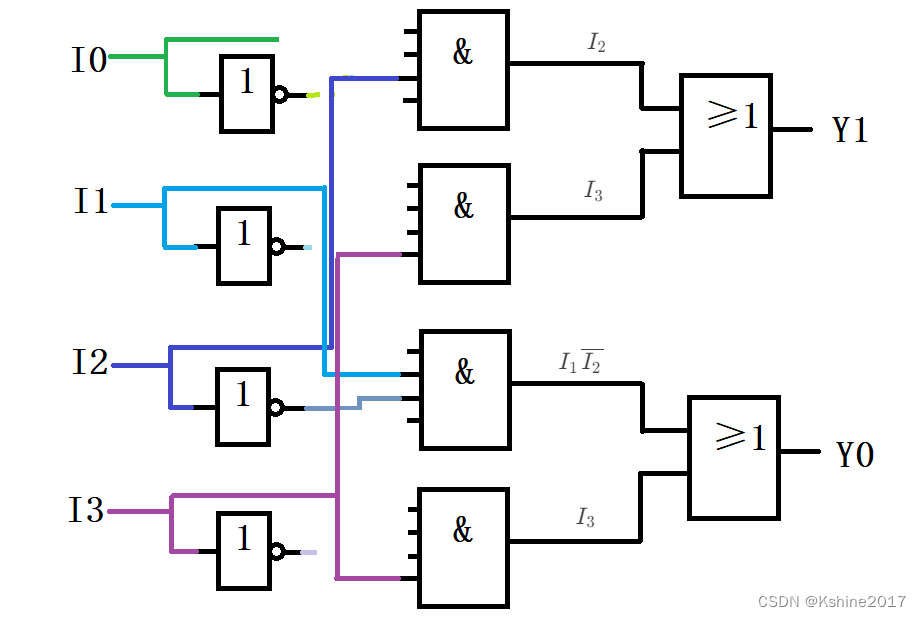

논리도를 그려보세요.

(1) 74HC00 칩에는 4개의 2입력 CMOS NAND 게이트가 포함되어 있습니다.

(2) 74HC04 칩에는 6개의 CMOS 인버터가 포함되어 있습니다.

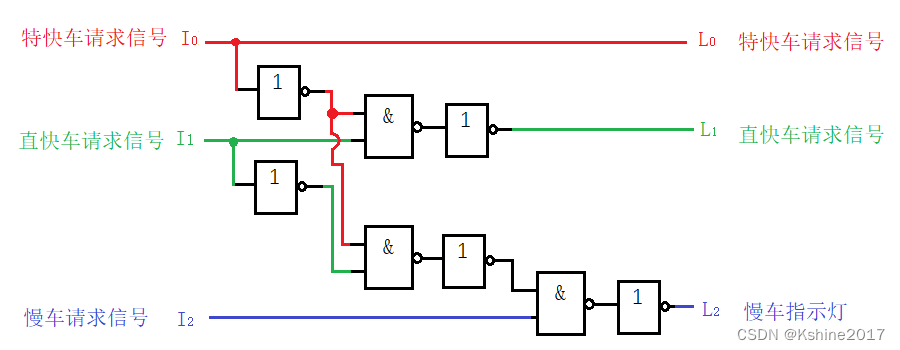

필요.

(1) 모든 논리 게이트 회로를 사용할 수 있습니다.

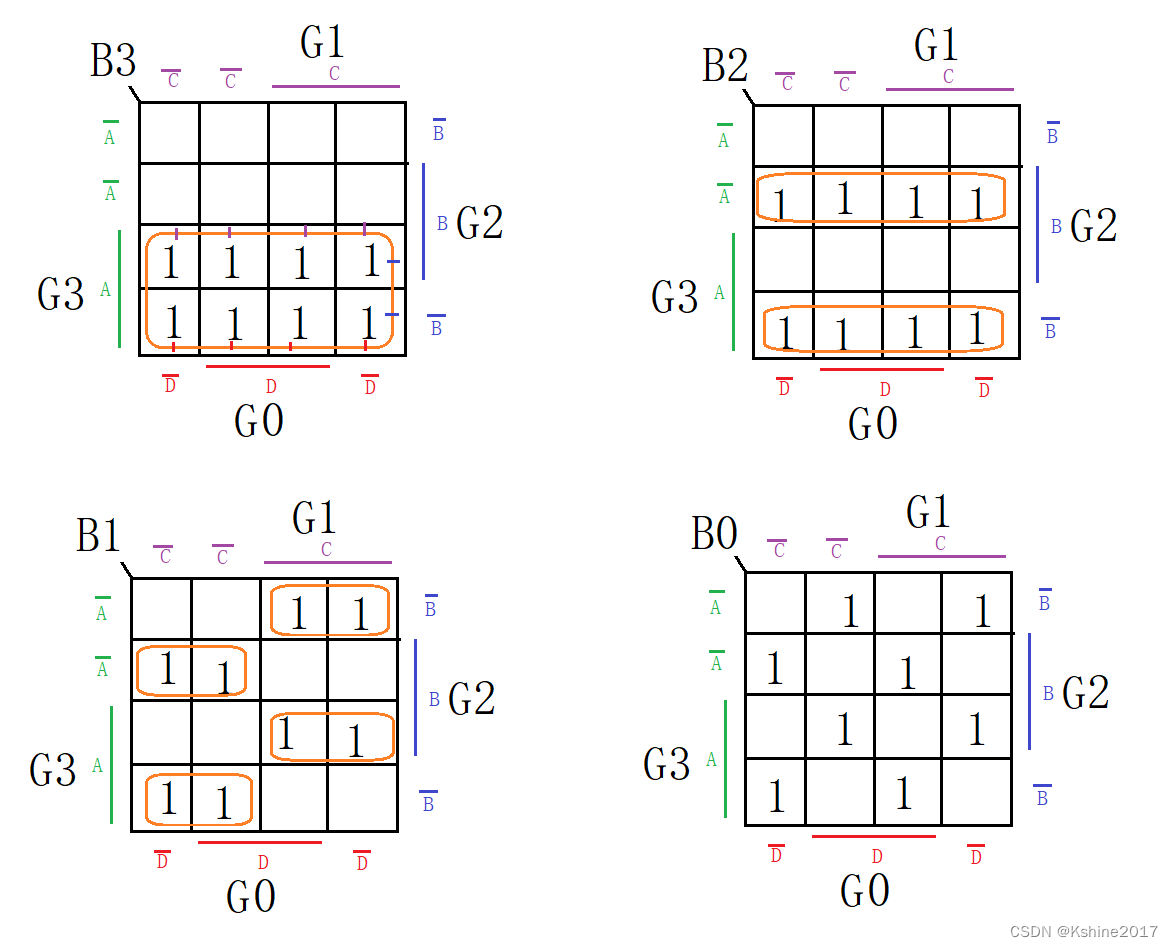

(2) 4비트 그레이 코드, 자연 바이너리 코드로 변환.

입력 및 출력 변수를 정의합니다.

(1) 입력변수, G3, G2, G1, G0 G_3,G_2,G_1,G_0G3,G2,G1,G0。

(2) 출력 변수, B3, B2, B1, B0 B_3,B_2,B_1,B_0비3,비2,비1,비0。

진리표를 나열해 보세요.

| 입력하다 | 산출 | ||||||

| G_3 | G_2 | G_1 | G_0 | 비_3 | B_2 | 비_1 | 비_0 |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 0 | 1 | 0 | 0 | 0 | 1 |

| 0 | 0 | 1 | 1 | 0 | 0 | 1 | 0 |

| 0 | 0 | 1 | 0 | 0 | 0 | 1 | 1 |

| 0 | 1 | 1 | 0 | 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 1 | 0 | 1 | 0 | 1 |

| 0 | 1 | 0 | 1 | 0 | 1 | 1 | 0 |

| 0 | 1 | 0 | 0 | 0 | 1 | 1 | 1 |

| 1 | 1 | 0 | 0 | 1 | 0 | 0 | 0 |

| 1 | 1 | 0 | 1 | 1 | 0 | 0 | 1 |

| 1 | 1 | 1 | 1 | 1 | 0 | 1 | 0 |

| 1 | 1 | 1 | 0 | 1 | 0 | 1 | 1 |

| 1 | 0 | 1 | 0 | 1 | 1 | 0 | 0 |

| 1 | 0 | 1 | 1 | 1 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 | 1 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 | 1 | 1 | 1 | 1 |

진리표를 바탕으로 Karnaugh 지도를 그립니다.

논리식을 나열합니다.

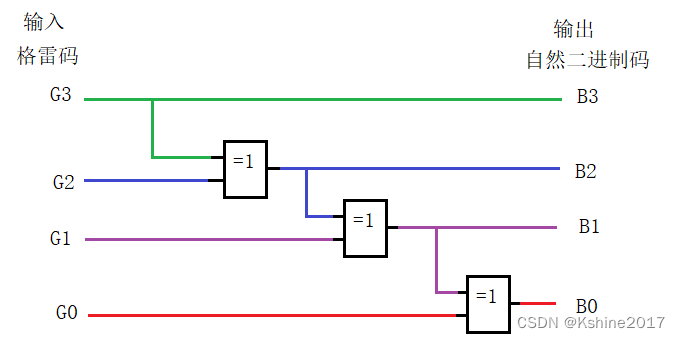

B3 = G3 B_3 = G_3비3=G3

B 2 = G 3 ⋅ G 2 + G 3 ⋅ G 2 ‾ = G 3 ⊕ G 2 B_2 = 윗줄{G_3}·G_2 + G_3·윗줄{G_2}=G_3⊕G_2비2=G3⋅G2+G3⋅G2=G3⊕G2

B 1 = G 3 ‾ G 2 G 1 ‾ + G 3 G 2 ‾ G 1 ‾ + G 3 ‾ G 2 ‾ G 1 + G 3 G 2 G 1 = ( G 3 G 2 ‾ + G 3 ‾ G 2 ) G 1 ‾ + ( G 3 G 2 ‾ + G 3 ‾ G 2 ) ‾ G 1 = G 3 ⊕ G 2 ⊕ G 1 B_1 = 오버라인{G_3}G_2오버라인{G_1}+G_3오버라인{G_2}오버라인{G_1}+오버라인{G_3}오버라인{G_2}G_1+G_3G_2G_1=(G_3오버라인{G_2}+오버라인{G_3}G_2)오버라인{G_1}+오버라인{(G_3오버라인{G_2}+오버라인{G_3}G_2)}G_1=G_3⊕G_2⊕G_1비1=G3G2G1+G3G2G1+G3G2G1+G3G2G1=(G3G2+G3G2)G1+(G3G2+G3G2)G1=G3⊕G2⊕G1

B 0 = G 3 ⊕ G 2 ⊕ G 1 ⊕ G 0 B_0=G_3⊕G_2⊕G_1⊕G_0비0=G3⊕G2⊕G1⊕G0

논리도를 그려보세요.

| 나 0 나_0나0 | 나 1 나_1나1 | 나 2 나_2나2 | 나 3 나_3나3 | 와 1 와 1와이1 | 와 0 와 0와이0 |

|---|---|---|---|---|---|

| 1 | 0 | 0 | 0 | 0 | 0 |

| 0 | 1 | 0 | 0 | 0 | 1 |

| 0 | 0 | 1 | 0 | 1 | 0 |

| 0 | 0 | 0 | 1 | 1 | 1 |

| 나 0 나_0나0 | 나 1 나_1나1 | 나 2 나_2나2 | 나 3 나_3나3 | 와 1 와 1와이1 | 와 0 와 0와이0 |

|---|---|---|---|---|---|

| 1 | 0 | 0 | 0 | 0 | 0 |

| 엑스 | 1 | 0 | 0 | 0 | 1 |

| 엑스 | 엑스 | 1 | 0 | 1 | 0 |

| 엑스 | 엑스 | 엑스 | 1 | 1 | 1 |

| 에스 9 에스_9에스9 | 에스 8 에스_8에스8 | 에스 7 에스_7에스7 | 에스 6 에스_6에스6 | 에스5에스_5에스5 | 에스4에스_4에스4 | 에스3에스_3에스3 | 에스2에스_2에스2 | 에스 1 에스_1에스1 | 0 0 0에스0 | 금주 모임ㅏ | 비비비 | 참조씨 | 디.디.디 | GS GSGS | |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | |

| 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | |

| 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 0 | 0 | 0 | 1 | 1 | |

| 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 0 | 0 | 1 | 0 | 1 | |

| 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 0 | 0 | 1 | 1 | 1 | |

| 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 0 | 1 | 0 | 0 | 1 | |

| 1 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 0 | 1 | 1 | |

| 1 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 0 | 1 | |

| 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | |

| 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 1 | |

| 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 1 | 1 |

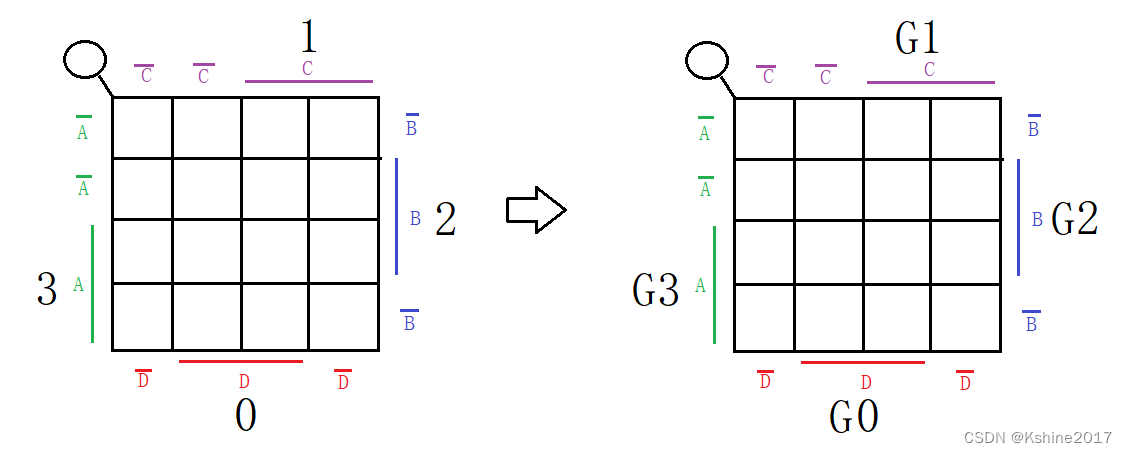

일반: CD4532 우선순위 인코더(단종됨)

우선순위 인코더 I 7은 가장 높은 우선순위를 가지며 I 0은 가장 낮은 우선순위를 갖습니다. 우선순위 인코더 I_7은 가장 높은 우선순위를 가지며 I_0은 가장 낮은 우선순위를 갖습니다.우선 순위 인코더나7최우선 순위,나0우선순위가 가장 낮습니다.

EI=1일 때 모든 입력이 로우 레벨이면낮은 우선순위 High 레벨을 입력하고 이때 000을 출력합니다. 이때 EO=1입니다.

EI=1이고 모든 입력이 0인 경우에만 EO=1입니다. 다른 장치와의 EI 캐스케이딩 전용입니다.

EI=1이면 입력 단자 중 적어도 하나가 하이 레벨 1이고 GS=1입니다.

구체적인 논리식과 논리 블록 다이어그램은 책을 참고하세요.

| EI는 인코딩을 허용합니다. EI는 인코딩을 허용합니다.이자형나인코딩이 허용됨 | 나 7 나_7나7 | 나 6 나_6나6 | 나 5 나_5나5 | 나 4 나_4나4 | 나 3 나_3나3 | 나 2 나_2나2 | 나 1 나_1나1 | 나 0 나_0나0 | 와 2 와 2와이2 | 와 1 와 1와이1 | 와 0 와 0와이0 | GS에는 입력 1이 있습니다. GS에는 입력 1이 있습니다.GS입력이 있습니다1 | EO는 모두 0을 입력합니다. EO는 모두 0을 입력합니다.이오모두 입력0 | |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 0 | 엑스 | 엑스 | 엑스 | 엑스 | 엑스 | 엑스 | 엑스 | 엑스 | 0 | 0 | 0 | 0 | 0 | |

| 1 | 1 | 엑스 | 엑스 | 엑스 | 엑스 | 엑스 | 엑스 | 엑스 | 1 | 1 | 1 | 1 | 0 | |

| 1 | 0 | 1 | 엑스 | 엑스 | 엑스 | 엑스 | 엑스 | 엑스 | 1 | 1 | 0 | 1 | 0 | |

| 1 | 0 | 0 | 1 | 엑스 | 엑스 | 엑스 | 엑스 | 엑스 | 1 | 0 | 1 | 1 | 0 | |

| 1 | 0 | 0 | 0 | 1 | 엑스 | 엑스 | 엑스 | 엑스 | 1 | 0 | 0 | 1 | 0 | |

| 1 | 0 | 0 | 0 | 0 | 1 | 엑스 | 엑스 | 엑스 | 0 | 1 | 1 | 1 | 0 | |

| 1 | 0 | 0 | 0 | 0 | 0 | 1 | 엑스 | 엑스 | 0 | 1 | 0 | 1 | 0 | |

| 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 엑스 | 0 | 0 | 1 | 1 | 0 | |

| 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 1 | 0 | |

| 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 |

EI 1 = 0이면 슬라이스 1이 비활성화됩니다. Y 2 Y 1 Y 0 = = 000 , GS 1 = 0 , EO 1 = 0 . EI 0 = 0, 칩 0도 비활성화됩니다. EI_1=0이면 슬라이스 1이 비활성화됩니다. Y_2Y_1Y_0==000, GS_1=0, EO_1=0. EI_0=0, 슬라이스 0도 비활성화됩니다.언제이자형나1=0시간, 영화1장애가 있는.와이2와이1와이0==000,G에스1=0,이자형영형1=0。이자형나0=0,조각0또한 비활성화되었습니다.

EI 1 = 1일 때 슬라이스 1은 인코딩이 허용됩니다. I 15 − I 8 = 000...000이면 EO 1 = 1이므로 EI 0 = 1입니다. 슬라이스 0은 인코딩을 허용합니다. 슬라이스 1의 인코딩이 슬라이스 0의 인코딩보다 우선순위가 높다는 것을 알 수 있습니다. EI_1=1이면 슬라이스 1의 인코딩이 허용됩니다. I_{15} - I_8 = 000...000이면 EO_1=입니다. 1이므로 EI_0=1입니다. 슬라이스 0은 인코딩을 허용합니다.슬라이스 1 인코딩의 우선순위가 슬라이스 0 인코딩의 우선순위보다 높다는 것을 알 수 있습니다.언제이자형나1=1시간, 영화1다음과 같은 경우 인코딩이 허용됩니다.나15−나8=000...000,이때이자형영형1=1,그것에 의하여이자형나0=1 .조각0 인코딩이 허용됩니다.영화라고 볼 수 있다1인코딩은 슬라이스보다 우선합니다.0코딩。

EI 1 = 1이면 슬라이스 1에서 인코딩이 허용됩니다. I 15 − I 8에 1이 하나 이상 있으면 EO 1 = 0이므로 EI 0 = 0이고 슬라이스 0에서는 인코딩이 금지됩니다. EI_1=1이면 슬라이스 1에서 인코딩이 허용됩니다. I_{15} - I_8에 1이 하나 이상 있으면 EO_1=0이므로 EI_0=0이면 슬라이스 0에서 인코딩이 금지됩니다.언제이자형나1=1시간, 영화1다음과 같은 경우 인코딩이 허용됩니다.나15−나8적어도 하나1,이때이자형영형1=0,그것에 의하여이자형나0=0,조각0인코딩이 금지되어 있습니다.

| EI 1은 인코딩을 허용합니다. EI_1은 인코딩을 허용합니다.이자형나1인코딩이 허용됨 | EI 0은 인코딩을 허용합니다. EI_0은 인코딩을 허용합니다.이자형나0인코딩이 허용됨 | 나 15 나_{15}나15 | 나 14 나_{14}나14 | 나 13 나_{13}나13 | 나 12 나_{12}나12 | 나 11 나_{11}나11 | 나 10 나_{10}나10 | 나 9 나_{9}나9 | 나 8 나_8나8 | 나 7 나_7나7 | 나 6 나_6나6 | 나 5 나_5나5 | 나 4 나_4나4 | 나 3 나_3나3 | 나 2 나_2나2 | 나 1 나_1나1 | 나 0 나_0나0 | 2 1 2_1 2_1와이21 | 1 1 Y1_1와이11 | 예 0 1 예 0_1와이01 | Y 2 0 Y2_0와이20 | 와 1 0 와 1_0와이10 | 예 0 0 예0_0와이00 | EO 1 0을 모두 입력하세요 EO_1 0을 모두 입력하세요이자형영형1모두 입력0 | EO 0 0을 모두 입력하세요 EO_0 0을 모두 입력하세요이자형영형0모두 입력0 | GS 1에는 입력 1이 있습니다. GS_1에는 입력 1이 있습니다.G에스1입력이 있습니다1 | GS 0에는 입력 0이 있습니다. GS_0에는 입력 0이 있습니다.G에스0입력이 있습니다0 | 엘 3 엘_3엘3 | 엘2엘_2엘2 | 엘 1 엘_1엘1 | 엘 0 엘_0엘0 | |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 0(슬라이스 1 비활성화됨) | EI 0 = EO 1 = 0 EI_0=EO_1=0이자형나0=이자형영형1=0(슬라이스 0에서는 비활성화됨) | 엑스 | 엑스 | 엑스 | 엑스 | 엑스 | 엑스 | 엑스 | 엑스 | 엑스 | 엑스 | 엑스 | 엑스 | 엑스 | 엑스 | 엑스 | 엑스 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | |

| 1 | 0 | 1 | 엑스 | 엑스 | 엑스 | 엑스 | 엑스 | 엑스 | 엑스 | 엑스 | 엑스 | 엑스 | 엑스 | 엑스 | 엑스 | 엑스 | 엑스 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 1(칩 1에 입력이 있음) | 0 | 1 L3 = GS1 L3 = GS1엘3=G에스1 | 1 L2 = Y2 1 L_2 = Y2_1엘2=와이21 | 1 L1 = Y1 1 L_1 = Y1_1엘1=와이11 | 1 L0 = Y01 L0 = Y0_1엘0=와이01 | |

| 1 | 0 | 0 | 1 | 엑스 | 엑스 | 엑스 | 엑스 | 엑스 | 엑스 | 엑스 | 엑스 | 엑스 | 엑스 | 엑스 | 엑스 | 엑스 | 엑스 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 1 | 1 | 1 | 0 | |

| 1 | 0 | 0 | 0 | 1 | 엑스 | 엑스 | 엑스 | 엑스 | 엑스 | 엑스 | 엑스 | 엑스 | 엑스 | 엑스 | 엑스 | 엑스 | 엑스 | 1 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 1 | 1 | 0 | 1 | |

| 1 | 0 | 0 | 0 | 0 | 1 | 엑스 | 엑스 | 엑스 | 엑스 | 엑스 | 엑스 | 엑스 | 엑스 | 엑스 | 엑스 | 엑스 | 엑스 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 1 | 1 | 0 | 0 | |

| 1 | 0 | 0 | 0 | 0 | 0 | 1 | 엑스 | 엑스 | 엑스 | 엑스 | 엑스 | 엑스 | 엑스 | 엑스 | 엑스 | 엑스 | 엑스 | 0 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 1 | 0 | 1 | 1 | |

| 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 엑스 | 엑스 | 엑스 | 엑스 | 엑스 | 엑스 | 엑스 | 엑스 | 엑스 | 엑스 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | |

| 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 엑스 | 엑스 | 엑스 | 엑스 | 엑스 | 엑스 | 엑스 | 엑스 | 엑스 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 1 | 0 | 0 | 1 | |

| 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 엑스 | 엑스 | 엑스 | 엑스 | 엑스 | 엑스 | 엑스 | 엑스 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 1 | 0 | 0 | 0 | |

| 1 | EI_0 = EO_1 = 1 EI_0 = EO_1 = 1이자형나0=이자형영형1=1(작품 0 작품) | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 엑스 | 엑스 | 엑스 | 엑스 | 엑스 | 엑스 | 엑스 | 0 | 0 | 0 | 1 | 1 | 1 | 1 (칩 1 입력은 모두 0) | 0 | 0(슬라이스 1에 대한 인코딩이 잘못됨) | 1 | 0 L3 = GS1 L3 = GS1엘3=G에스1 | 1 L2 = Y20 L_2 = Y2_0엘2=와이20 | 1 L1 = Y10 L_1 = Y1_0엘1=와이10 | 1 L0 = Y0 0 L_0 =Y0_0엘0=와이00 | |

| 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 엑스 | 엑스 | 엑스 | 엑스 | 엑스 | 엑스 | 0 | 0 | 0 | 1 | 1 | 0 | 1 | 0 | 0 | 1 | 0 | 1 | 1 | 0 | |

| 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 엑스 | 엑스 | 엑스 | 엑스 | 엑스 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 0 | 1 | 0 | 1 | 0 | 1 | |

| 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 엑스 | 엑스 | 엑스 | 엑스 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 0 | 1 | 0 | 1 | 0 | 0 | |

| 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 엑스 | 엑스 | 엑스 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 0 | 1 | 0 | 0 | 1 | 1 | |

| 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 엑스 | 엑스 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 0 | 1 | 0 | 0 | 1 | 0 | |

| 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 엑스 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 1 | |

| 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | |

| 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 (칩 0번 입력은 모두 0) | 0 | 0(슬라이스 0 잘못된 인코딩) | 0 | 0 | 0 | 0 |

| 입력하다 | 산출 | |||||

| /이자형 | 아_1 | 아_0 | /Y_3 | /Y_2 | /Y_1 | /Y_0 |

| 1 금지 | 엑스 | 엑스 | 1 | 1 | 1 | 1 |

| 0 활성화 | 0 | 0 | 1 | 1 | 1 | 0 낮음 활성 |

| 0 활성화 | 0 | 1 | 1 | 1 | 0 낮음 유효 | 1 |

| 0 활성화 | 1 | 0 | 1 | 0 낮음 활성 | 1 | 1 |

| 0 활성화 | 1 | 1 | 0 낮음 활성 | 1 | 1 | 1 |

Y 0 ‾ = E ‾ ‾ ⋅ A 1 ‾ ⋅ A 0 ‾ ‾ 윗줄{Y_0} = 윗줄{윗줄{윗줄{E}}·윗줄{A_1}·윗줄{A_0}}와이0=이자형⋅ㅏ1⋅ㅏ0 //00

Y 1 ‾ = E ‾ ‾ ⋅ A 1 ‾ ⋅ A 0 ‾ 윗줄{Y_1} = 윗줄{윗줄{윗줄{E}}·윗줄{A_1}·A_0}와이1=이자형⋅ㅏ1⋅ㅏ0 //01

Y 2 ‾ = E ‾ ‾ ⋅ A 1 ⋅ A 0 ‾ ‾ 윗줄{Y_2} = 윗줄{윗줄{윗줄{E}}·A_1·윗줄{A_0}}와이2=이자형⋅ㅏ1⋅ㅏ0 //10

Y 3 ‾ = E ‾ ‾ ⋅ A 1 ⋅ A 0 ‾ 윗줄{Y_3} = 윗줄{윗줄{윗줄{E}}·A_1·A_0}와이3=이자형⋅ㅏ1⋅ㅏ0 //11

Y 0 ‾ = E 3 ⋅ E 2 ‾ ‾ ⋅ E 1 ‾ ‾ ⋅ A 2 ‾ ⋅ A 1 ‾ ⋅ A 0 ‾ ‾ 윗줄{Y_0} = 윗줄{E_3·윗줄{윗줄{E_2}}·윗줄{윗줄{E_1}}·윗줄{A_2}·윗줄{A_1}·윗줄{A_0}}와이0=이자형3⋅이자형2⋅이자형1⋅ㅏ2⋅ㅏ1⋅ㅏ0 //000

Y 1 ‾ = E 3 ⋅ E 2 ‾ ‾ ⋅ E 1 ‾ ‾ ⋅ A 2 ‾ ⋅ A 1 ‾ ⋅ A 0 ‾ 윗줄{Y_1} = 윗줄{E_3·윗줄{윗줄{E_2}}·윗줄{윗줄{E_1}}·윗줄{A_2}·윗줄{A_1}·A_0}와이1=이자형3⋅이자형2⋅이자형1⋅ㅏ2⋅ㅏ1⋅ㅏ0 //001

Y 2 ‾ = E 3 ⋅ E 2 ‾ ‾ ⋅ E 1 ‾ ‾ ⋅ A 2 ‾ ⋅ A 1 ⋅ A 0 ‾ ‾ 윗줄{Y_2} = 윗줄{E_3·윗줄{윗줄{E_2}}·윗줄{윗줄{E_1}}·윗줄{A_2}·A_1·윗줄{A_0}}와이2=이자형3⋅이자형2⋅이자형1⋅ㅏ2⋅ㅏ1⋅ㅏ0 //010

Y 3 ‾ = E 3 ⋅ E 2 ‾ ‾ ⋅ E 1 ‾ ‾ ⋅ A 2 ‾ ⋅ A 1 ⋅ A 0 ‾ 윗줄{Y_3} = 윗줄{E_3·윗줄{윗줄{E_2}}·윗줄{윗줄{E_1}}·윗줄{A_2}·A_1·A_0}와이3=이자형3⋅이자형2⋅이자형1⋅ㅏ2⋅ㅏ1⋅ㅏ0 //011

Y 4 ‾ = E 3 ⋅ E 2 ‾ ‾ ⋅ E 1 ‾ ‾ ⋅ A 2 ⋅ A 1 ‾ ⋅ A 0 ‾ ‾ 윗줄{Y_4} = 윗줄{E_3·윗줄{윗줄{E_2}}·윗줄{윗줄{E_1}}·A_2·윗줄{A_1}·윗줄{A_0}}와이4=이자형3⋅이자형2⋅이자형1⋅ㅏ2⋅ㅏ1⋅ㅏ0 //100

Y 5 ‾ = E 3 ⋅ E 2 ‾ ‾ ⋅ E 1 ‾ ‾ ⋅ A 2 ⋅ A 1 ‾ ⋅ A 0 ‾ 윗줄{Y_5} = 윗줄{E_3·윗줄{윗줄{E_2}}·윗줄{윗줄{E_1}}·A_2·윗줄{A_1}·A_0}와이5=이자형3⋅이자형2⋅이자형1⋅ㅏ2⋅ㅏ1⋅ㅏ0 //101

Y 6 ‾ = E 3 ⋅ E 2 ‾ ‾ ⋅ E 1 ‾ ‾ ⋅ A 2 ⋅ A 1 ⋅ A 0 ‾ ‾ 윗줄{Y_6} = 윗줄{E_3·윗줄{윗줄{E_2}}·윗줄{윗줄{E_1}}·A_2·A_1·윗줄{A_0}}와이6=이자형3⋅이자형2⋅이자형1⋅ㅏ2⋅ㅏ1⋅ㅏ0 //110

Y 7 ‾ = E 3 ⋅ E 2 ‾ ‾ ⋅ E 1 ‾ ‾ ⋅ A 2 ⋅ A 1 ⋅ A 0 ‾ 윗줄{Y_7} = 윗줄{E_3·윗줄{윗줄{E_2}}·윗줄{윗줄{E_1}}·A_2·A_1·A_0}와이7=이자형3⋅이자형2⋅이자형1⋅ㅏ2⋅ㅏ1⋅ㅏ0 //111

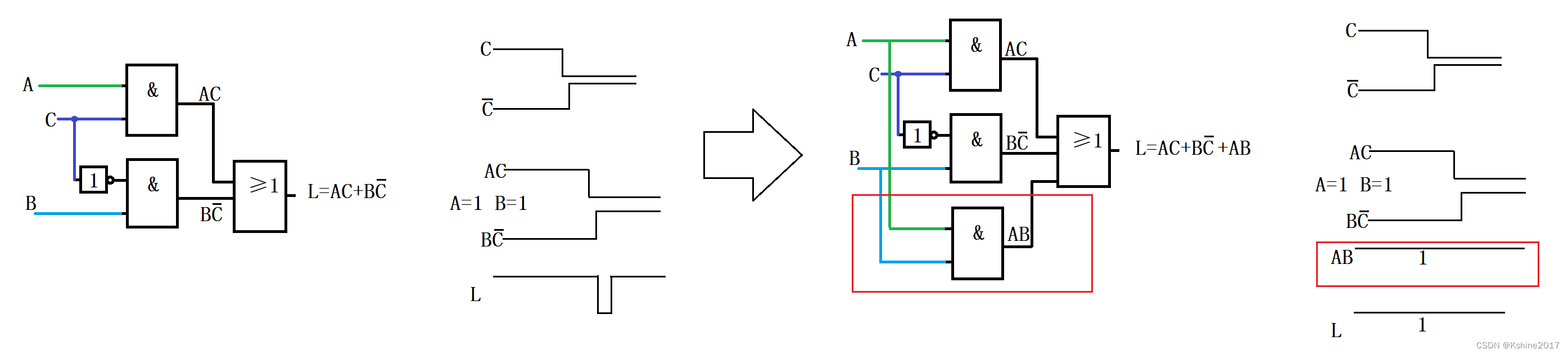

L = A‾ ⋅ C‾ + A ⋅ B = A‾ ⋅ B‾ ⋅ C‾ + A‾ ⋅ B ⋅ C‾ + A ⋅ B ⋅ C‾ + ABC = m 0 + m 2 + m 6 + m 7 L =윗줄{A}·윗줄{C}+A·B =윗줄{A}·윗줄{B}·윗줄{C}+윗줄{A}·B·윗줄{C} + A·B·윗줄{C}+ABC = m_0+m_2+m_6+m_7엘=ㅏ⋅씨+ㅏ⋅비=ㅏ⋅비⋅씨+ㅏ⋅비⋅씨+ㅏ⋅비⋅씨+ㅏ기원전=중0+중2+중6+중7

Y 0 ‾ = E 3 ⋅ E 2 ‾ ‾ ⋅ E 1 ‾ ‾ ⋅ A 2 ‾ ⋅ A 1 ‾ ⋅ A 0 ‾ ‾ = E 3 ⋅ E 2 ‾ ‾ ⋅ E 1 ‾ ‾ ⋅ m 0 ‾ 윗줄{Y_0} = 윗줄{E_3·윗줄{윗줄{E_2}}·윗줄{윗줄{E_1}}·윗줄{A_2}·윗줄{A_1}·윗줄{A_0}} = 윗줄{E_3·윗줄{윗줄{E_2}}·윗줄{E_1}}·m_0}와이0=이자형3⋅이자형2⋅이자형1⋅ㅏ2⋅ㅏ1⋅ㅏ0=이자형3⋅이자형2⋅이자형1⋅중0 //000

Y 1 ‾ = E 3 ⋅ E 2 ‾ ‾ ⋅ E 1 ‾ ‾ ⋅ A 2 ‾ ⋅ A 1 ‾ ⋅ A 0 ‾ = E 3 ⋅ E 2 ‾ ‾ ⋅ E 1 ‾ ‾ ⋅ m 1 ‾ 윗줄{Y_1} = 윗줄{E_3·윗줄{윗줄{E_2}}·윗줄{윗줄{E_1}}·윗줄{A_2}·윗줄{A_1}·A_0} = 윗줄{E_3·윗줄{윗줄{E_2}}·윗줄{윗줄{E_1}}·m_1}와이1=이자형3⋅이자형2⋅이자형1⋅ㅏ2⋅ㅏ1⋅ㅏ0=이자형3⋅이자형2⋅이자형1⋅중1 //001

Y 2 ‾ = E 3 ⋅ E 2 ‾ ‾ ⋅ E 1 ‾ ‾ ⋅ A 2 ‾ ⋅ A 1 ⋅ A 0 ‾ ‾ = E 3 ⋅ E 2 ‾ ‾ ⋅ E 1 ‾ ‾ ⋅ m 2 ‾ 윗줄{Y_2} = 윗줄{E_3·윗줄{윗줄{E_2}}·윗줄{윗줄{E_1}}·윗줄{A_2}·A_1·윗줄{A_0}}= 윗줄{E_3·윗줄{윗줄{E_2}}·윗줄{E_1}}·m_2}와이2=이자형3⋅이자형2⋅이자형1⋅ㅏ2⋅ㅏ1⋅ㅏ0=이자형3⋅이자형2⋅이자형1⋅중2 //010

Y 3 ‾ = E 3 ⋅ E 2 ‾ ‾ ⋅ E 1 ‾ ‾ ⋅ A 2 ‾ ⋅ A 1 ⋅ A 0 ‾ = E 3 ⋅ E 2 ‾ ‾ ⋅ E 1 ‾ ‾ ⋅ m 3 ‾ 윗줄{Y_3} = 윗줄{E_3·윗줄{윗줄{E_2}}·윗줄{윗줄{E_1}}·윗줄{A_2}·A_1·A_0}= 윗줄{E_3·윗줄{윗줄{E_2}}·윗줄{윗줄{E_1}}·m_3}와이3=이자형3⋅이자형2⋅이자형1⋅ㅏ2⋅ㅏ1⋅ㅏ0=이자형3⋅이자형2⋅이자형1⋅중3 //011

Y 4 ‾ = E 3 ⋅ E 2 ‾ ‾ ⋅ E 1 ‾ ‾ ⋅ A 2 ⋅ A 1 ‾ ⋅ A 0 ‾ ‾ = E 3 ⋅ E 2 ‾ ‾ ⋅ E 1 ‾ ‾ ⋅ m 4 ‾ 윗줄{Y_4} = 윗줄{E_3·윗줄{윗줄{E_2}}·윗줄{윗줄{E_1}}·A_2·윗줄{A_1}·윗줄{A_0}}= 윗줄{E_3·윗줄{윗줄{E_2}}·윗줄{E_1}}·m_4}와이4=이자형3⋅이자형2⋅이자형1⋅ㅏ2⋅ㅏ1⋅ㅏ0=이자형3⋅이자형2⋅이자형1⋅중4 //100

Y 5 ‾ = E 3 ⋅ E 2 ‾ ‾ ⋅ E 1 ‾ ‾ ⋅ A 2 ⋅ A 1 ‾ ⋅ A 0 ‾ = E 3 ⋅ E 2 ‾ ‾ ⋅ E 1 ‾ ‾ ⋅ m 5 ‾ 윗줄{Y_5} = 윗줄{E_3·윗줄{윗줄{E_2}}·윗줄{윗줄{E_1}}·A_2·윗줄{A_1}·A_0}= 윗줄{E_3·윗줄{윗줄{E_2}}·윗줄{윗줄{E_1}}·m_5}와이5=이자형3⋅이자형2⋅이자형1⋅ㅏ2⋅ㅏ1⋅ㅏ0=이자형3⋅이자형2⋅이자형1⋅중5 //101

Y 6 ‾ = E 3 ⋅ E 2 ‾ ‾ ⋅ E 1 ‾ ‾ ⋅ A 2 ⋅ A 1 ⋅ A 0 ‾ ‾ = E 3 ⋅ E 2 ‾ ‾ ⋅ E 1 ‾ ‾ ⋅ m 6 ‾ 윗줄{Y_6} = 윗줄{E_3·윗줄{윗줄{E_2}}·윗줄{윗줄{E_1}}·A_2·A_1·윗줄{A_0}}= 윗줄{E_3·윗줄{윗줄{E_2}}·윗줄{E_1}}·m_6}와이6=이자형3⋅이자형2⋅이자형1⋅ㅏ2⋅ㅏ1⋅ㅏ0=이자형3⋅이자형2⋅이자형1⋅중6 //110

Y 7 ‾ = E 3 ⋅ E 2 ‾ ‾ ⋅ E 1 ‾ ‾ ⋅ A 2 ⋅ A 1 ⋅ A 0 ‾ = E 3 ⋅ E 2 ‾ ‾ ⋅ E 1 ‾ ‾ ⋅ m 7 ‾ 윗줄{Y_7} = 윗줄{E_3·윗줄{윗줄{E_2}}·윗줄{윗줄{E_1}}·A_2·A_1·A_0}= 윗줄{E_3·윗줄{윗줄{E_2}}·윗줄{윗줄{E_1}}·m_7}와이7=이자형3⋅이자형2⋅이자형1⋅ㅏ2⋅ㅏ1⋅ㅏ0=이자형3⋅이자형2⋅이자형1⋅중7 //111

E 3 = 1 , E 2 = 0 , E 1 = 0인지 확인하세요 E_3=1,E_2=0,E_1=0인지 확인하세요확실하게 하다이자형3=1,이자형2=0,이자형1=0, 즉 말하자면 Y 0 ‾ = m 0 ‾ , Y 2 ‾ = m 2 ‾ , Y 6 ‾ = m 6 ‾ , Y 7 ‾ = m 7 ‾ 윗줄{Y_0}=윗줄{m_0},윗줄{Y_2}=윗줄{m_2},윗줄{Y_6}=윗줄{m_6},윗줄{Y_7}=윗줄{m_7}와이0=중0,와이2=중2,와이6=중6,와이7=중7。

반전 법칙에 따라 논리 함수를 변환합니다.

L = L‾‾ = m0 + m2 + m6 + m7‾‾ = m0‾ ⋅ m2‾ ⋅ m6‾ ⋅ m7‾ ‾ = m0 + m2 + m6 + m7‾ ‾ = Y0‾ ⋅ Y2‾ ⋅ Y6‾ ⋅ Y7‾ ‾ L=윗줄{윗줄{L}} = 윗줄{윗줄{m_0+m_2+m_6+m_7}} = 윗줄{윗줄{m_0}·윗줄{m_2}·윗줄{m_6}·윗줄{m_7}} = 윗줄{윗줄{m_0+m_2+m_6+m_7}} = 윗줄{윗줄{Y_0}·윗줄{Y_2}·윗줄{Y_6}·윗줄{Y_7}}엘=엘=중0+중2+중6+중7=중0⋅중2⋅중6⋅중7=중0+중2+중6+중7=와이0⋅와이2⋅와이6⋅와이7

논리 다이어그램 가져오기

774HC42

4개의 입력

10개의 출력 단자, 출력은 10진수 0~9에 해당하는 낮은 레벨에서 활성화됩니다.

4개의 입력 단자, 총 16가지 상황

오직 m 0 , m 1 , m 2 . . . . . . m 9 m_0 ,m_1,m_2......m_9중0,중1,중2......중9유효한 입력입니다(해당 출력 핀은 low 0을 출력하고 다른 출력은 high 1입니다).

나머지 6개 중 m 10 , m 11 , m 12 . . . . . . m 15 m_{10} ,m_{11},m_{12}......m_{15}중10,중11,중12......중15이는 유효한 디코딩 출력이 없음을 의미합니다(유효하지 않은 경우 출력은 모두 하이 1입니다).

74HC42의 입출력 파형도를 그려라.

디지털 튜브 디스플레이 원리

통합 7세그먼트 디스플레이 디코더. 74HC4511(공통 음극)(높은 수준의 점등)

르 르엘이자형래치 활성화

LT‾ 오버라인{LT}엘티램프 테스트 입력 시 LT‾ = 0 오버라인{LT}=0엘티=0이면 ag는 모두 1을 출력하고 글꼴 "8"을 표시합니다.

BL‾ 오버라인{BL}비엘소등 입력시 LT ‾ = 1, 그리고 BL ‾ = 1 윗줄{LT}=1, 윗줄{BL}=1엘티=1,그리고비엘=1 일 때, ag는 모두 0을 출력합니다. 불필요하게 표시된 0 "0"을 끄는 데 사용할 수 있습니다.

디 3 디 2 디 1 디 0 디_3디_2디_1디_0디3디2디1디0=0000, 해당 출력 문자 "0"

디 3 디 2 디 1 디 0 디_3디_2디_1디_0디3디2디1디0=0001, 해당 출력 글꼴 "1"

디 3 디 2 디 1 디 0 디_3디_2디_1디_0디3디2디1디0=0010, 해당 출력 글꼴 "2"

디 3 디 2 디 1 디 0 디_3디_2디_1디_0디3디2디1디0=0011, 해당 출력 글꼴 "3"

디 3 디 2 디 1 디 0 디_3디_2디_1디_0디3디2디1디0=0100, 해당 출력 글꼴 "4"

디 3 디 2 디 1 디 0 디_3디_2디_1디_0디3디2디1디0=0101, 해당 출력 글꼴 "5"

디 3 디 2 디 1 디 0 디_3디_2디_1디_0디3디2디1디0=0110, 해당 출력 글꼴 "6"

디 3 디 2 디 1 디 0 디_3디_2디_1디_0디3디2디1디0=0111, 해당 출력 글꼴 "7"

디 3 디 2 디 1 디 0 디_3디_2디_1디_0디3디2디1디0=1000, 해당 출력 글꼴 "8"

디 3 디 2 디 1 디 0 디_3디_2디_1디_0디3디2디1디0=1001, 해당 출력 글꼴 "9"

1010-1111, 꺼짐

하나부터 여러 개까지 공통 데이터 라인의 데이터는 필요에 따라 다른 채널로 전송됩니다.

"단극 다투 스위치"와 유사

고유한 주소 디코더를 사용하여 데이터 할당자를 구현합니다.

예를 들어 74x138은 3라인에서 8라인 디코더를 통합합니다.

E 1 ‾ 데이터 입력 overline{E_1} 데이터 입력이자형1데이터 입력으로

Y 0 Y 1 Y 2 Y 3 Y 4 Y 5 Y 6 Y 7 Y_0 Y_1 Y_2Y_3Y_4Y_5Y_6Y_7와이0와이1와이2와이3와이4와이5와이6와이7데이터 출력으로 8개 채널

Y 2 ‾ = E 3 ⋅ E 2 ‾ ‾ ⋅ E 1 ‾ ‾ ⋅ A 2 ‾ ⋅ A 1 ⋅ A 0 ‾ ‾ 윗줄{Y_2} = 윗줄{E_3·윗줄{윗줄{E_2}}·윗줄{윗줄{E_1}}·윗줄{A_2}·A_1·윗줄{A_0}}와이2=이자형3⋅이자형2⋅이자형1⋅ㅏ2⋅ㅏ1⋅ㅏ0 //010

위 사진은, E 3 = 1 , E 2 = 0 E_3=1,윗줄{E_2}=0이자형3=1,이자형2=0, 주소 입력란이 A2A1A0=010 A_2A_1A_0=010ㅏ2ㅏ1ㅏ0=010시간, Y 2 ‾ = E 1 ‾ 윗줄{Y_2}=윗줄{E_1}와이2=이자형1

동일한 토큰으로 다음과 같은 결론을 내릴 수 있습니다.

주소란에 A 2 A 1 A 0 = 000 A_2A_1A_0=000ㅏ2ㅏ1ㅏ0=000시간, Y 0 ‾ = E 1 ‾ = D 윗줄{Y_0}=윗줄{E_1}=D와이0=이자형1=디,다른 y_x = 1 y_x = 1 이다.와이엑스=1。

주소란에 A 2 A 1 A 0 = 001 A_2A_1A_0=001ㅏ2ㅏ1ㅏ0=001시간, Y 1‾ = E 1‾ = D 윗줄{Y_1}=윗줄{E_1}=D와이1=이자형1=디,다른 y_x = 1 y_x = 1 이다.와이엑스=1。

주소란에 A2A1A0=010 A_2A_1A_0=010ㅏ2ㅏ1ㅏ0=010시간, Y 2 ‾ = E 1 ‾ = D 윗줄{Y_2}=윗줄{E_1}=D와이2=이자형1=디,다른 y_x = 1 y_x = 1 이다.와이엑스=1。

주소란에 A2A1A0=011 A_2A_1A_0=011ㅏ2ㅏ1ㅏ0=011시간, Y 3‾ = E 1‾ = D 윗줄{Y_3}=윗줄{E_1}=D와이3=이자형1=디,다른 y_x = 1 y_x = 1 이다.와이엑스=1。

주소란에 A 2 A 1 A 0 = 100 A_2A_1A_0=100ㅏ2ㅏ1ㅏ0=100시간, Y 4‾ = E 1‾ = D 윗줄{Y_4}=윗줄{E_1}=D와이4=이자형1=디,다른 y_x = 1 y_x = 1 이다.와이엑스=1。

주소란에 A2A1A0=101 A_2A_1A_0=101ㅏ2ㅏ1ㅏ0=101시간, Y 5 ‾ = E 1 ‾ = D 윗줄{Y_5}=윗줄{E_1}=D와이5=이자형1=디,다른 y_x = 1 y_x = 1 이다.와이엑스=1。

주소란에 A2A1A0=110 A_2A_1A_0=110ㅏ2ㅏ1ㅏ0=110시간, Y 6‾ = E 1‾ = D 윗줄{Y_6}=윗줄{E_1}=D와이6=이자형1=디,다른 y_x = 1 y_x = 1 이다.와이엑스=1。

주소란에 A2A1A0=111 A_2A_1A_0=111ㅏ2ㅏ1ㅏ0=111시간, Y 7 ‾ = E 1 ‾ = D 윗줄{Y_7}=윗줄{E_1}=D와이7=이자형1=디,다른 y_x = 1 y_x = 1 이다.와이엑스=1。

Y = S 2 ‾ ⋅ S 1 ‾ ⋅ S 0 ‾ ⋅ D 0 + S 2 ‾ ⋅ S 1 ‾ ⋅ S 0 ⋅ D 1 + S 2 ‾ ⋅ S 1 ⋅ S 0 ‾ ⋅ D 2 + S 2 ‾ ⋅ S 1 ⋅ S 0 ⋅ D 3 + S 2 ⋅ S 1 ‾ ⋅ S 0 ‾ ⋅ D 4 + S 2 ⋅ S 1 ‾ ⋅ S 0 ⋅ D 5 + S 2 ⋅ S 1 ⋅ S 0 ‾ ⋅ D 6 + S 2 ⋅ S 1 ⋅ S 0 ⋅ D 7 Y = 윗줄{S_2}·윗줄{S_1}·윗줄{S_0}·D_0 +오버라인{S_2}·오버라인{S_1}·S_0·D_1 +오버라인{S_2}·S_1·오버라인{S_0}·D_2 +오버라인{S_2}·S_1·S_0·D_3 +S_2·오버라인{S_1}·오버라인{S_0}·D_4 +S_2·오버라인{S_1}·S_0·D_5 +S_2·S_1·오버라인{S_0}·D_6 +S_2·S_1·S_0·D_7와이=에스2⋅에스1⋅에스0⋅디0+에스2⋅에스1⋅에스0⋅디1+에스2⋅에스1⋅에스0⋅디2+에스2⋅에스1⋅에스0⋅디3+에스2⋅에스1⋅에스0⋅디4+에스2⋅에스1⋅에스0⋅디5+에스2⋅에스1⋅에스0⋅디6+에스2⋅에스1⋅에스0⋅디7

데이터 선택기의 확장입니다.

논리 함수 발생기

알려진 8대1 데이터 선택기.

Y = S 2 ‾ ⋅ S 1 ‾ ⋅ S 0 ‾ ⋅ D 0 + S 2 ‾ ⋅ S 1 ‾ ⋅ S 0 ⋅ D 1 + S 2 ‾ ⋅ S 1 ⋅ S 0 ‾ ⋅ D 2 + S 2 ‾ ⋅ S 1 ⋅ S 0 ⋅ D 3 + S 2 ⋅ S 1 ‾ ⋅ S 0 ‾ ⋅ D 4 + S 2 ⋅ S 1 ‾ ⋅ S 0 ⋅ D 5 + S 2 ⋅ S 1 ⋅ S 0 ‾ ⋅ D 6 + S 2 ⋅ S 1 ⋅ S 0 ⋅ D 7 Y = 윗줄{S_2}·윗줄{S_1}·윗줄{S_0}·D_0 +오버라인{S_2}·오버라인{S_1}·S_0·D_1 +오버라인{S_2}·S_1·오버라인{S_0}·D_2 +오버라인{S_2}·S_1·S_0·D_3 +S_2·오버라인{S_1}·오버라인{S_0}·D_4 +S_2·오버라인{S_1}·S_0·D_5 +S_2·S_1·오버라인{S_0}·D_6 +S_2·S_1·S_0·D_7와이=에스2⋅에스1⋅에스0⋅디0+에스2⋅에스1⋅에스0⋅디1+에스2⋅에스1⋅에스0⋅디2+에스2⋅에스1⋅에스0⋅디3+에스2⋅에스1⋅에스0⋅디4+에스2⋅에스1⋅에스0⋅디5+에스2⋅에스1⋅에스0⋅디6+에스2⋅에스1⋅에스0⋅디7

Y = m 0 ⋅ D 0 + m 1 ⋅ D 1 + m 2 ⋅ D 2 + m 3 ⋅ D 3 + m 4 ⋅ D 4 + m 5 ⋅ D 5 + m 6 ⋅ D 6 + m 7 ⋅ D 7 Y = m_0·D_0 +m_1·D_1 +m_2·D_2 +m_3·D_3 +m_4·D_4 +m_5·D_5 +m_6·D_6 +m_7·D_7와이=중0⋅디0+중1⋅디1+중2⋅디2+중3⋅디3+중4⋅디4+중5⋅디5+중6⋅디6+중7⋅디7

논리적 기능 L = A‾ BC + AB‾ C + ABL=윗줄{A}BC+A윗줄{B}C+AB엘=ㅏ기원전+ㅏ비씨+ㅏ비

L = A‾ BC + AB‾ C + AB = A‾ BC + AB‾ C + ABC‾ + ABC = m3 + m5 + m6 + m7 L = 오버라인{A}BC+A오버라인{B}C+AB=오버라인{A}BC+A오버라인{B}C+AB오버라인{C}+ABC=m_3+m_5+m_6+m_7엘=ㅏ기원전+ㅏ비씨+ㅏ비=ㅏ기원전+ㅏ비씨+ㅏ비씨+ㅏ기원전=중3+중5+중6+중7

8대1 데이터 선택기를 사용하여 위의 함수 L을 구현합니다.

L = Y = m 3 + m 5 + m 6 + m 7, 여기서 D 7 D 6 D 5 D 3 = 1111, D 4 D 2 D 1 D 0 = 0000 L=Y=m_3+m_5+m_6+m_7, 그 중 D_7D_6D_5D_3=1111, D_4D_2D_1D_0=0000엘=와이=중3+중5+중6+중7,안에디7디6디5디3=1111,디4디2디1디0=0000

병렬 데이터를 직렬 데이터로

| ㅏ | 비 | FA > B F_{A>B}에프ㅏ>비 | FA < B F_{A에프ㅏ<비 | FA = = B F_{A==B}에프ㅏ==비 |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 1 |

| 0 | 1 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 0 |

| 1 | 1 | 0 | 0 | 1 |

| A1?B1 A_1?B_1ㅏ1?비1 | A 0 ? B 0 A_0?B_0ㅏ0?비0 | FA > B F_{A>B}에프ㅏ>비 | FA < B F_{A에프ㅏ<비 | FA = = B F_{A==B}에프ㅏ==비 |

|---|---|---|---|---|

| A1 > B1 A_1>B_1ㅏ1>비1 | 엑스 | 1 | 0 | 0 |

| A 1 < B 1 A_1ㅏ1<비1 | 엑스 | 0 | 1 | 0 |

| A 1 = = B 1 A_1==B_1ㅏ1==비1 | A 0 > B 0 A_0>B_0ㅏ0>비0 | 1 | 0 | 0 |

| A 1 = = B 1 A_1==B_1ㅏ1==비1 | A0<B0A_0ㅏ0<비0 | 0 | 1 | 0 |

| A 1 = = B 1 A_1==B_1ㅏ1==비1 | A 0 = = B 0 A_0==B_0ㅏ0==비0 | 0 | 0 | 1 |

논리식

FA > B = FA 1 > B 1 + FA 1 = = B 1 ⋅ FA 0 > B 0 F_{A>B} = F_{A_1>B_1} +F_{A_1==B_1}·F_{A_0>B_0}에프ㅏ>비=에프ㅏ1>비1+에프ㅏ1==비1⋅에프ㅏ0>비0

FA < B = FA 1 < B 1 + FA 1 = = B 1 ⋅ FA 0 < B 0 F_{A에프ㅏ<비=에프ㅏ1<비1+에프ㅏ1==비1⋅에프ㅏ0<비0

FA = = B = FA 1 = = B 1 ⋅ FA 0 = = B 0 F_{A==B} = F_{A_1==B_1}·F_{A_0==B_0}에프ㅏ==비=에프ㅏ1==비1⋅에프ㅏ0==비0

논리도

직렬 연결, 8비트 수치 비교기로 확장

병렬 연결, 16비트 수치 비교기로 확장.

병렬로 연결하면 속도가 빠릅니다.