minhas informações de contato

Correspondência[email protected]

2024-07-12

한어Русский языкEnglishFrançaisIndonesianSanskrit日本語DeutschPortuguêsΕλληνικάespañolItalianoSuomalainenLatina

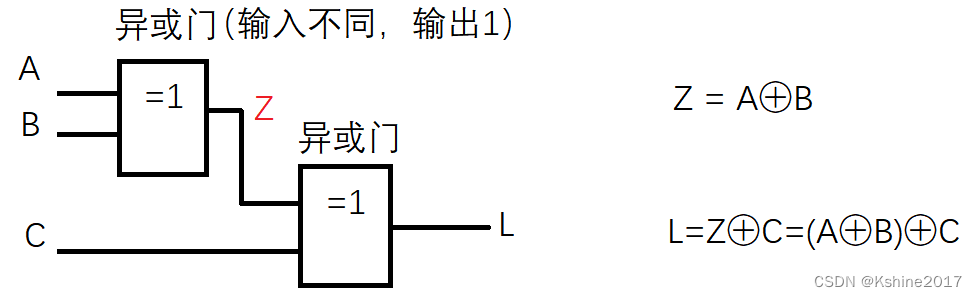

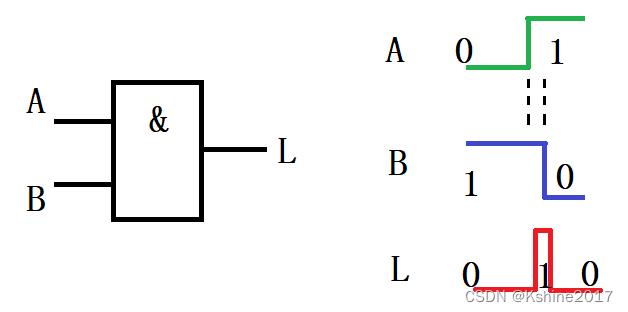

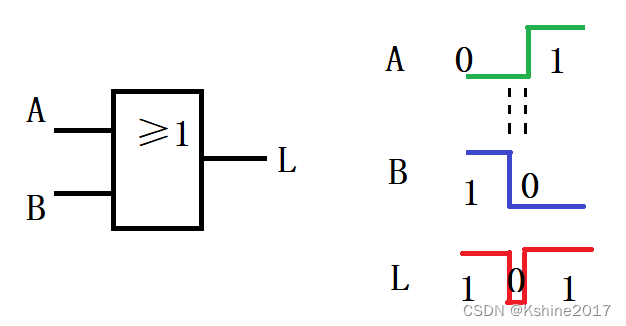

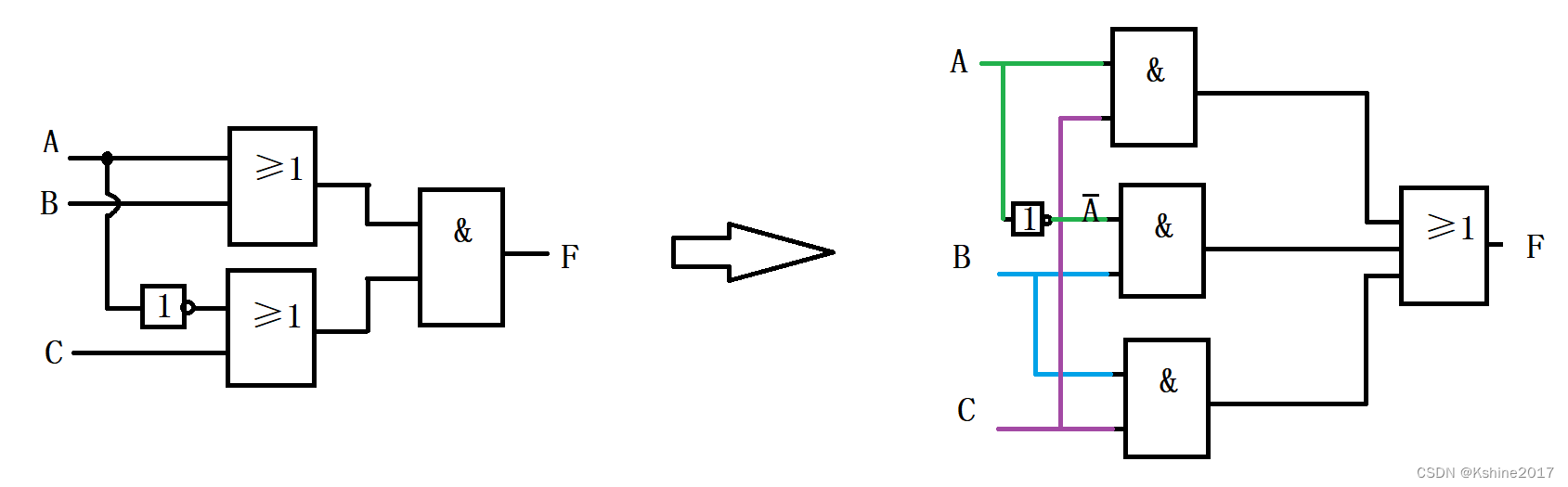

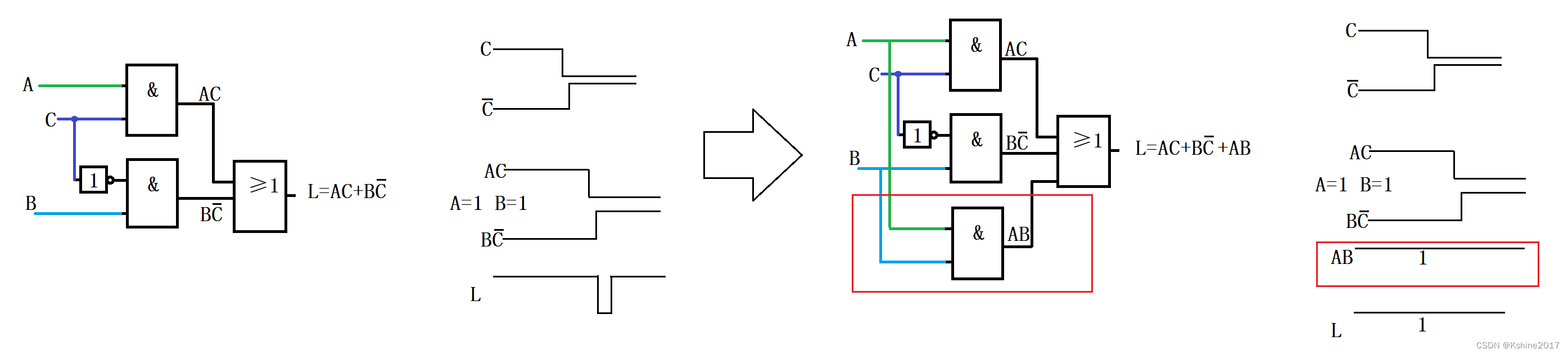

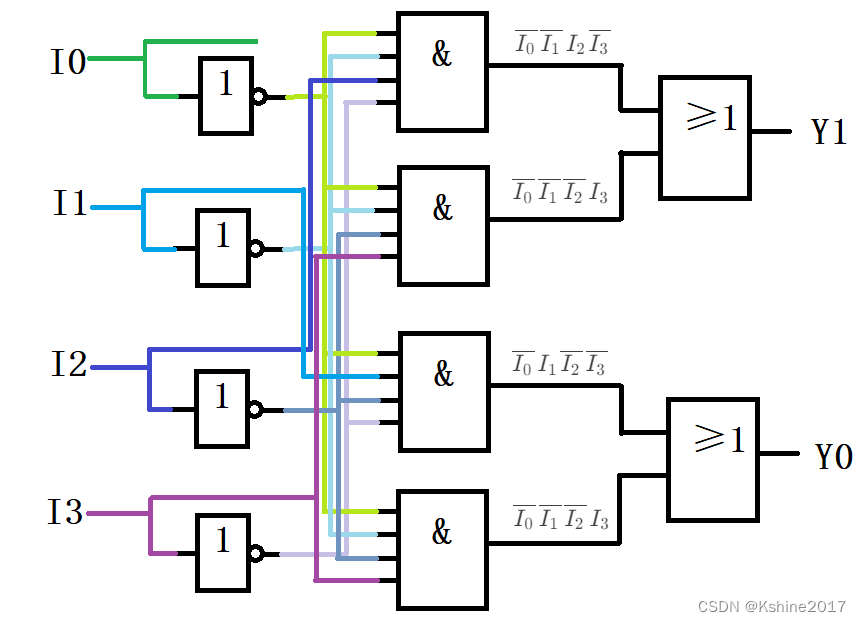

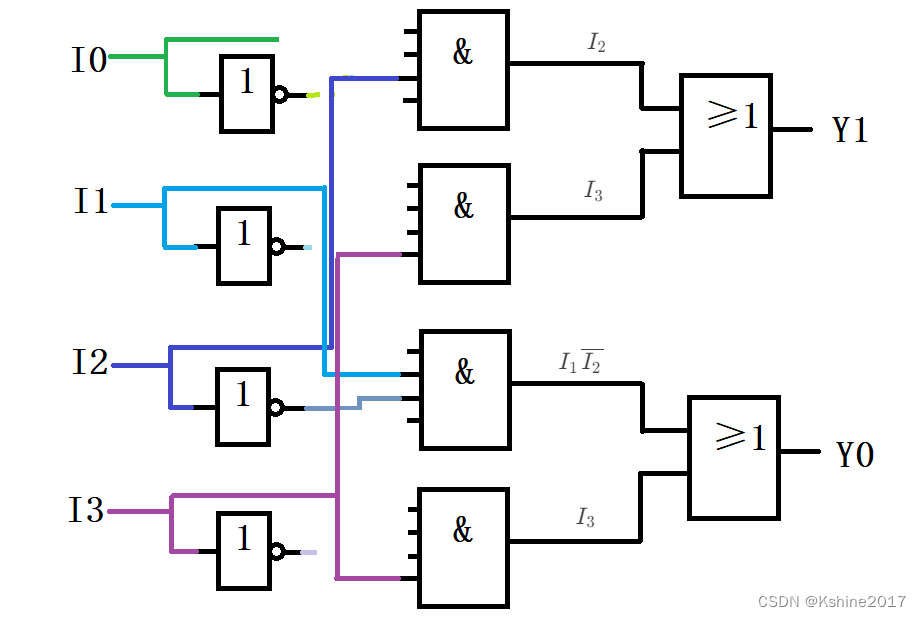

(1) Conforme mostrado na figura abaixo.

(2) Liste a tabela verdade

| A | B | C | Z | eu |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 | 1 |

| 0 | 1 | 0 | 1 | 1 |

| 0 | 1 | 1 | 1 | 0 |

| 1 | 0 | 0 | 1 | 1 |

| 1 | 0 | 1 | 1 | 0 |

| 1 | 1 | 0 | 0 | 0 |

| 1 | 1 | 1 | 0 | 1 |

(3) AnaliseCircuito de paridade ímparFunção.

(1) Com base no circuito de paridade ímpar, adicionando um inversor à extremidade de saída, podemos obterCircuito de paridade par。

| A | B | C | X | E | Z |

|---|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 | 0 | 1 |

| 0 | 1 | 0 | 0 | 1 | 0 |

| 0 | 1 | 1 | 0 | 1 | 1 |

| 1 | 0 | 0 | 1 | 1 | 1 |

| 1 | 0 | 1 | 1 | 1 | 0 |

| 1 | 1 | 0 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 | 0 | 0 |

precisar.

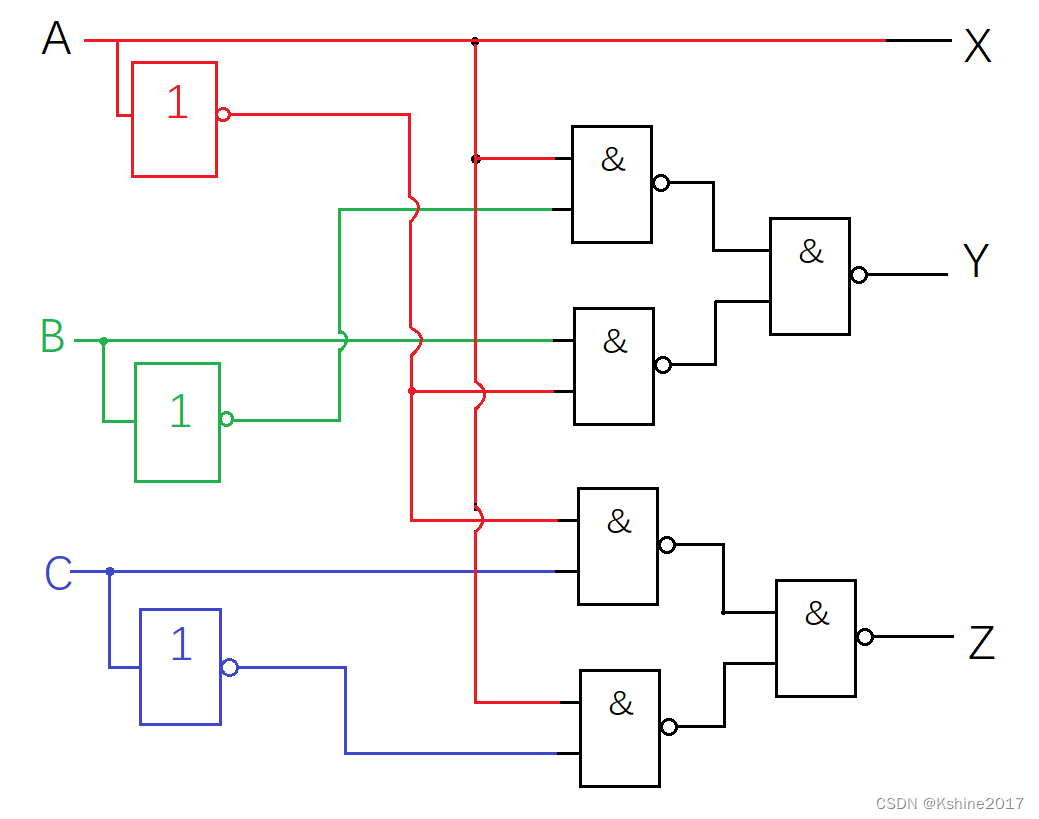

(1) Use 2 entradasPorta NAND,inversor.

(2) Luz indicadora nº 1, luz indicadora de chegada do trem expresso. Prioridade máxima.

(3) Luz indicadora nº 2, trem expresso direto entrando na luz indicadora da estação. Em prioridade.

(4) Luz indicadora nº 3, trem lento entrando na luz indicadora da estação. Baixa prioridade.

(5) No máximo uma luz indicadora pode acender ao mesmo tempo.

Defina variáveis de entrada e saída.

(1) sinal de entrada, I 0 solicitação expressa, I 1 solicitação expressa direta, I 2 solicitação de trem local I_0 solicitação expressa, I_1 solicitação expressa direta, I_2 solicitação de trem localEU0pedido expresso,EU1Basta solicitá-lo rapidamente,EU2Solicitação de trem lenta . 1 significa que há uma solicitação de entrada, 0 significa que não há solicitação de entrada.

(2) sinal de saída, Luz indicadora de parada expressa L 0, luz indicadora de parada expressa direta L 1, luz indicadora de parada de trem local L 2 Luz indicadora de parada expressa L_0, luz indicadora de parada rápida direta L_1, luz indicadora de parada de trem local L_2eu0Luz de chegada expressa,eu1Luz indicadora de parada direta,eu2Luz indicadora de chegada lenta do trem . 1 significa que a luz está acesa, 0 significa que a luz está apagada.

Tabela verdade.

| digitar | saída | ||||

| Eu_0 | Eu_1 | Eu_2 | Eu_0 | L_1 | L_2 |

| 0 | 0 | 0 | 0 | 0 | 0 |

| 1 | X | X | 1 | 0 | 0 |

| 0 | 1 | X | 0 | 1 | 0 |

| 0 | 0 | 1 | 0 | 0 | 1 |

Listar expressões lógicas

Eu 0 = Eu 0 Eu_0 = Eu_0eu0=EU0

L 1 = I 0 ‾ ⋅ I 1 L_1 = sobrelinha{I_0}·I_1eu1=EU0⋅EU1

L 2 = I 0 ‾ ⋅ I 1 ‾ ⋅ I 2 L_2 = sobrelinha{I_0}·sobrelinha{I_1}·I_2eu2=EU0⋅EU1⋅EU2

Converta para o formato NAND conforme necessário.

Eu 0 = Eu 0 Eu_0 = Eu_0eu0=EU0

L 1 = I 0 ‾ ⋅ I 1 ‾ ‾ L_1 = sobrelinha{sobrelinha{sobrelinha{I_0}·I_1}}eu1=EU0⋅EU1

L 2 = I 0 ‾ ⋅ I 1 ‾ ‾ ‾ ⋅ I 2 ‾ ‾ L_2 =sobrelinha{sobrelinha{sobrelinha{sobrelinha{sobrelinha{I_0}·sobrelinha{I_1}}}·I_2}}eu2=EU0⋅EU1⋅EU2

Desenhe um diagrama lógico.

(1) Um chip 74HC00 contém quatro portas CMOS NAND de 2 entradas.

(2) Um chip 74HC04 contém 6 inversores CMOS.

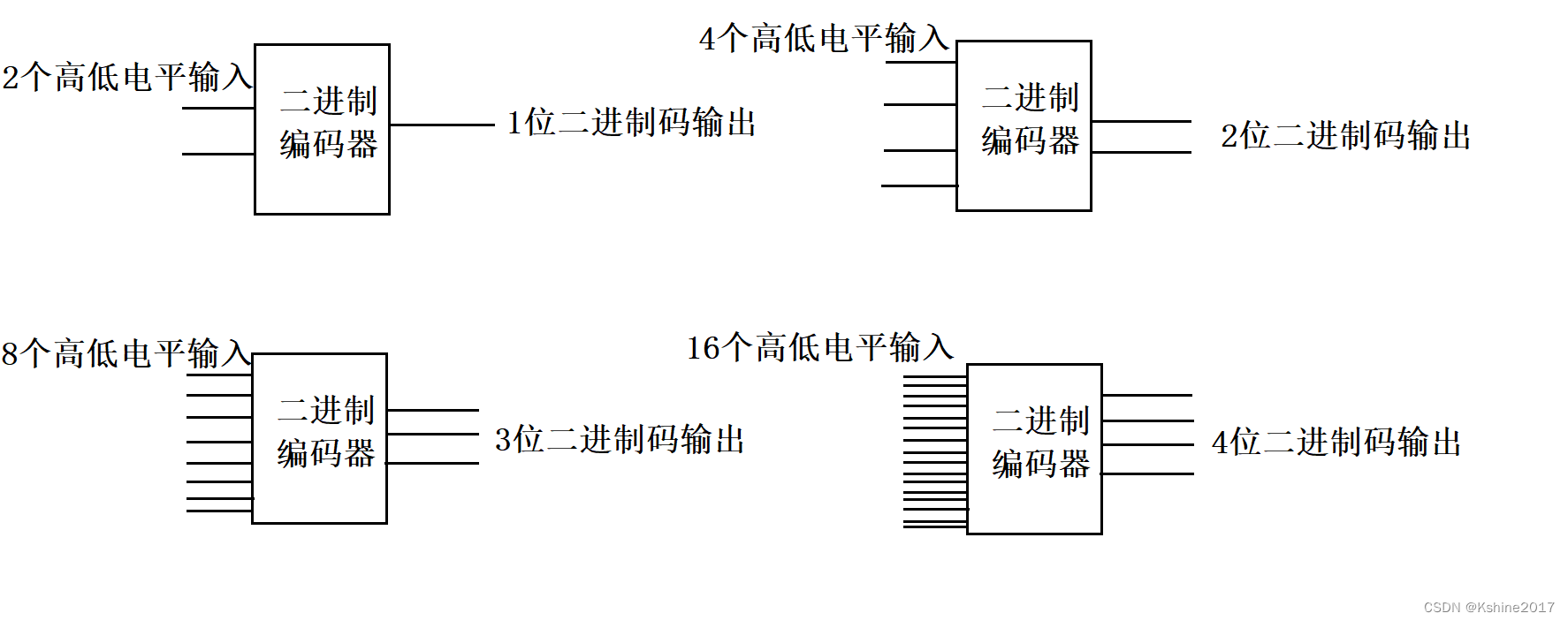

precisar.

(1) Qualquer circuito de porta lógica pode ser usado.

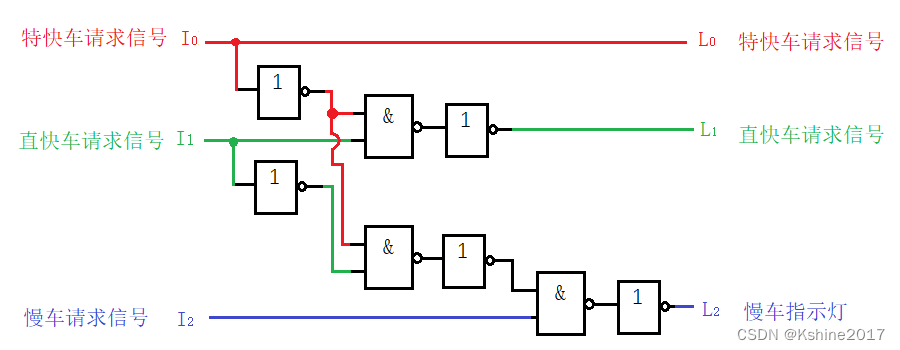

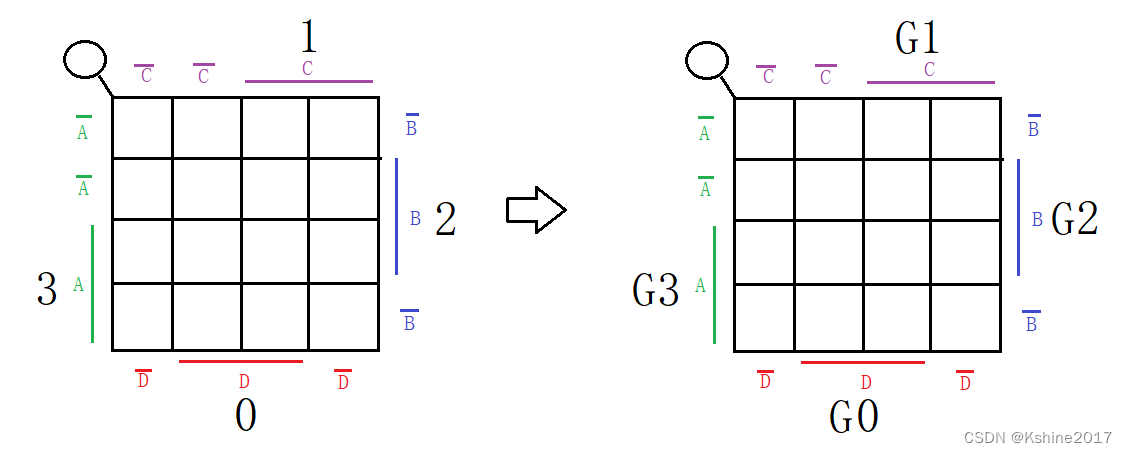

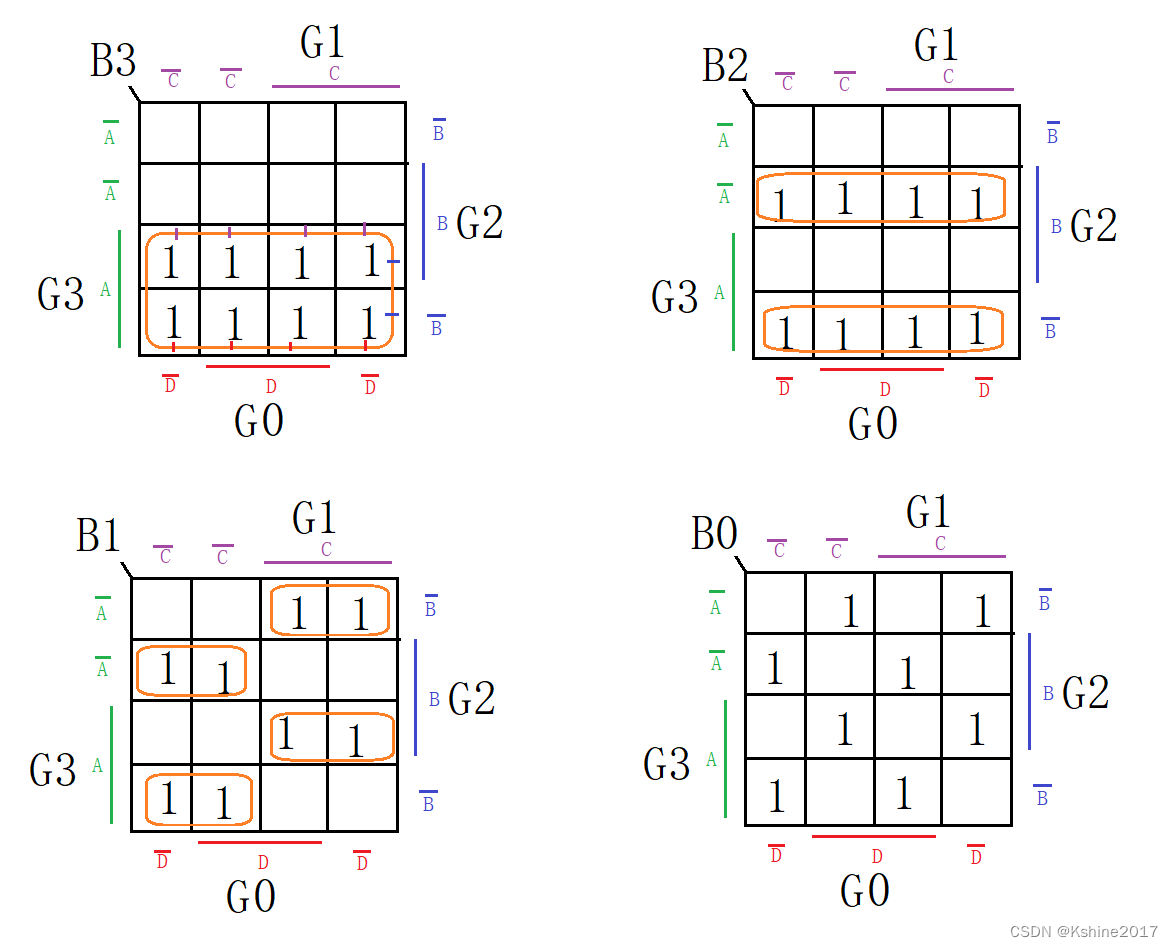

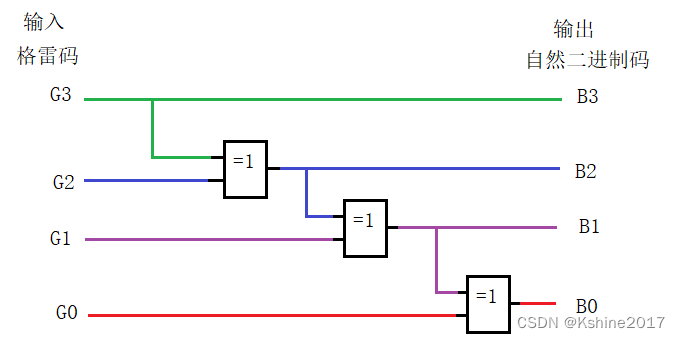

(2) Código Gray de 4 bits, convertido em código binário natural.

Defina variáveis de entrada e saída.

(1) Variáveis de entrada, G 3 , G 2 , G 1 , G 0 G_3,G_2,G_1,G_0G3,G2,G1,G0。

(2) Variáveis de saída, B3, B2, B1, B0 B_3,B_2,B_1,B_0B3,B2,B1,B0。

Liste a tabela verdade.

| digitar | saída | ||||||

| G_3 | G_2 | G_1 | G_0 | B_3 | B_2 | B_1 | B_0 |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 0 | 1 | 0 | 0 | 0 | 1 |

| 0 | 0 | 1 | 1 | 0 | 0 | 1 | 0 |

| 0 | 0 | 1 | 0 | 0 | 0 | 1 | 1 |

| 0 | 1 | 1 | 0 | 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 1 | 0 | 1 | 0 | 1 |

| 0 | 1 | 0 | 1 | 0 | 1 | 1 | 0 |

| 0 | 1 | 0 | 0 | 0 | 1 | 1 | 1 |

| 1 | 1 | 0 | 0 | 1 | 0 | 0 | 0 |

| 1 | 1 | 0 | 1 | 1 | 0 | 0 | 1 |

| 1 | 1 | 1 | 1 | 1 | 0 | 1 | 0 |

| 1 | 1 | 1 | 0 | 1 | 0 | 1 | 1 |

| 1 | 0 | 1 | 0 | 1 | 1 | 0 | 0 |

| 1 | 0 | 1 | 1 | 1 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 | 1 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 | 1 | 1 | 1 | 1 |

Desenhe um mapa de Karnaugh baseado na tabela verdade.

Liste expressões lógicas.

B 3 = G 3 B_3 = G_3B3=G3

B 2 = G 3 ‾ ⋅ G 2 + G 3 ⋅ G 2 ‾ = G 3 ⊕ G 2 B_2 = sobrelinha{G_3}·G_2 + G_3·sobrelinha{G_2}=G_3⊕G_2B2=G3⋅G2+G3⋅G2=G3⊕G2

B 1 = G 3 ‾ G 2 G 1 ‾ + G 3 G 2 ‾ G 1 ‾ + G 3 ‾ G 2 ‾ G 1 + G 3 G 2 G 1 = ( G 3 G 2 ‾ + G 3 ‾ G 2 ) G 1 ‾ + ( G 3 G 2 ‾ + G 3 ‾ G 2 ) ‾ G 1 = G 3 ⊕ G 2 ⊕ G 1 B_1 = sobrelinha{G_3}G_2sobrelinha{G_1}+G_3sobrelinha{G_2}sobrelinha{G_1}+sobrelinha{G_3}sobrelinha{G_2}G_1+G_3G_2G_1=(G_3sobrelinha{G_2}+sobrelinha{G_3}G_2)sobrelinha{G_1}+sobrelinha{(G_3sobrelinha{G_2}+sobrelinha{G_3}G_2)}G_1=G_3⊕G_2⊕G_1B1=G3G2G1+G3G2G1+G3G2G1+G3G2G1=(G3G2+G3G2)G1+(G3G2+G3G2)G1=G3⊕G2⊕G1

B 0 = G 3 ⊕ G 2 ⊕ G 1 ⊕ G 0 B_0=G_3⊕G_2⊕G_1⊕G_0B0=G3⊕G2⊕G1⊕G0

Desenhe um diagrama lógico.

| Eu 0 Eu_0EU0 | Eu 1 Eu_1EU1 | Eu 2 Eu_2EU2 | Eu 3 Eu_3EU3 | E 1 E_1E1 | E 0 E_0E0 |

|---|---|---|---|---|---|

| 1 | 0 | 0 | 0 | 0 | 0 |

| 0 | 1 | 0 | 0 | 0 | 1 |

| 0 | 0 | 1 | 0 | 1 | 0 |

| 0 | 0 | 0 | 1 | 1 | 1 |

| Eu 0 Eu_0EU0 | Eu 1 Eu_1EU1 | Eu 2 Eu_2EU2 | Eu 3 Eu_3EU3 | E 1 E_1E1 | E 0 E_0E0 |

|---|---|---|---|---|---|

| 1 | 0 | 0 | 0 | 0 | 0 |

| X | 1 | 0 | 0 | 0 | 1 |

| X | X | 1 | 0 | 1 | 0 |

| X | X | X | 1 | 1 | 1 |

| S 9 S_9S9 | S 8 S_8S8 | S 7 S_7S7 | S 6 S_6S6 | S 5 S_5S5 | S 4 S_4S4 | E 3 E_3S3 | S 2 S_2S2 | E 1 E_1S1 | S 0 S_0S0 | AAA | BBB | CCC | DDE | GS GSGS | |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | |

| 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | |

| 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 0 | 0 | 0 | 1 | 1 | |

| 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 0 | 0 | 1 | 0 | 1 | |

| 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 0 | 0 | 1 | 1 | 1 | |

| 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 0 | 1 | 0 | 0 | 1 | |

| 1 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 0 | 1 | 1 | |

| 1 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 0 | 1 | |

| 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | |

| 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 1 | |

| 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 1 | 1 |

Típico: codificador de prioridade CD4532 (descontinuado)

O codificador de prioridade I 7 tem a prioridade mais alta e I 0 tem a prioridade mais baixa. O codificador de prioridade I_7 tem a prioridade mais alta e I_0 tem a prioridade mais baixa.codificador de prioridadeEU7Prioridade máxima,EU0A prioridade mais baixa.

Quando EI=1, quando todas as entradas são de baixo nível, nãoprioridade mais baixa Insira alto nível e produza 000 neste momento. Neste momento EO=1.

Somente quando EI=1 e todas as entradas forem 0, EO=1. Dedicado ao EI em cascata com outro dispositivo.

Quando EI=1, pelo menos um dos terminais de entrada é de alto nível 1 e GS=1.

Consulte o livro para expressões lógicas específicas e diagramas de blocos lógicos.

| EI permite codificação EI permite codificaçãoEEUCodificação permitida | Eu 7 Eu_7EU7 | Eu 6 Eu_6EU6 | Eu 5 Eu_5EU5 | Eu 4 Eu_4EU4 | Eu 3 Eu_3EU3 | Eu 2 Eu_2EU2 | Eu 1 Eu_1EU1 | Eu 0 Eu_0EU0 | E 2 E_2E2 | E 1 E_1E1 | E 0 E_0E0 | GS tem entrada 1 GS tem entrada 1GSHá entrada1 | EO insere todos os 0s EO insere todos os 0sEODigite tudo0 | |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 0 | x | x | x | x | x | x | x | x | 0 | 0 | 0 | 0 | 0 | |

| 1 | 1 | x | x | x | x | x | x | x | 1 | 1 | 1 | 1 | 0 | |

| 1 | 0 | 1 | x | x | x | x | x | x | 1 | 1 | 0 | 1 | 0 | |

| 1 | 0 | 0 | 1 | x | x | x | x | x | 1 | 0 | 1 | 1 | 0 | |

| 1 | 0 | 0 | 0 | 1 | x | x | x | x | 1 | 0 | 0 | 1 | 0 | |

| 1 | 0 | 0 | 0 | 0 | 1 | x | x | x | 0 | 1 | 1 | 1 | 0 | |

| 1 | 0 | 0 | 0 | 0 | 0 | 1 | x | x | 0 | 1 | 0 | 1 | 0 | |

| 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | x | 0 | 0 | 1 | 1 | 0 | |

| 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 1 | 0 | |

| 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 |

Quando EI 1 = 0, o slice 1 é desabilitado. S 2 S 1 S 0 = = 000 , GS 1 = 0 , EO 1 = 0 . EI 0 = 0, chip 0 também está desabilitado. Quando EI_1=0, o slice 1 é desabilitado. Y_2Y_1Y_0==000, GS_1=0, EO_1=0. EI_0=0, a fatia 0 também está desabilitada.quandoEEU1=0tempo, filme1Desabilitado.E2E1E0==000,GS1=0,EO1=0。EEU0=0,pedaço0Também desativado.

Quando EI 1 = 1, a fatia 1 pode ser codificada. Se I 15 − I 8 = 000...000, então EO 1 = 1, então EI 0 = 1. A fatia 0 permite a codificação. Pode-se observar que a codificação da fatia 1 tem uma prioridade mais alta que a codificação da fatia 0. Quando EI_1=1, a codificação da fatia 1 é permitida. Se I_{15} - I_8 = 000...000, então EO_1=. 1, então EI_0=1. A fatia 0 permite a codificação.Pode-se observar que a prioridade da codificação da fatia 1 é maior do que a da codificação da fatia 0.quandoEEU1=1tempo, filme1A codificação é permitida seEU15−EU8=000...000,Neste momentoEO1=1,deste modoEEU0=1 .pedaço0 A codificação é permitida.Pode-se perceber que o filme1A codificação tem prioridade sobre fatias0codificação。

Quando EI 1 = 1, a codificação é permitida na fatia 1. Se I 15 − I 8 tiver pelo menos um 1, então EO 1 = 0, então EI 0 = 0, e a codificação é proibida na fatia 0. Quando EI_1=1, a codificação é permitida na fatia 1. Se I_{15} - I_8 tiver pelo menos um 1, então EO_1=0, então EI_0=0, a codificação é proibida na fatia 0.quandoEEU1=1tempo, filme1A codificação é permitida seEU15−EU8pelo menos um1,Neste momentoEO1=0,deste modoEEU0=0,pedaço0A codificação é proibida.

| EI 1 permite codificação EI_1 permite codificaçãoEEU1Codificação permitida | EI 0 permite codificação EI_0 permite codificaçãoEEU0Codificação permitida | Eu 15 Eu_{15}EU15 | Eu 14 Eu_{14}EU14 | Eu 13 Eu_{13}EU13 | Eu 12 Eu_{12}EU12 | Eu 11 Eu_{11}EU11 | Eu 10 Eu_{10}EU10 | Eu 9 Eu_{9}EU9 | Eu 8 Eu_8EU8 | Eu 7 Eu_7EU7 | Eu 6 Eu_6EU6 | Eu 5 Eu_5EU5 | Eu 4 Eu_4EU4 | Eu 3 Eu_3EU3 | Eu 2 Eu_2EU2 | Eu 1 Eu_1EU1 | Eu 0 Eu_0EU0 | E 2 1 E2_1E21 | E 1 1 E1_1E11 | E 0 1 E0_1E01 | E 2 0 E2_0E20 | E 1 0 E1_0E10 | E 0 0 E0_0E00 | EO 1 Insira todos os 0s EO_1 Insira todos os 0sEO1Digite tudo0 | EO 0 Insira todos os 0s EO_0 Insira todos os 0sEO0Digite tudo0 | GS 1 tem entrada 1 GS_1 tem entrada 1GS1Há entrada1 | GS 0 tem entrada 0 GS_0 tem entrada 0GS0Há entrada0 | E 3 E_3eu3 | E 2 E_2eu2 | E 1 E_1eu1 | Eu 0 Eu_0eu0 | |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 0 (fatia 1 desativada) | EI 0 = EO 1 = 0 EI_0=EO_1=0EEU0=EO1=0(desativado na fatia 0) | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | |

| 1 | 0 | 1 | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 1 (Chip 1 tem entrada) | 0 | 1 L 3 = GS 1 L_3 = GS_1eu3=GS1 | 1 Eu 2 = Y 2 1 Eu_2 = Y2_1eu2=E21 | 1 L 1 = Y 1 1 L_1 =Y1_1eu1=E11 | 1 Eu 0 = Y 0 1 L_0 =Y0_1eu0=E01 | |

| 1 | 0 | 0 | 1 | x | x | x | x | x | x | x | x | x | x | x | x | x | x | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 1 | 1 | 1 | 0 | |

| 1 | 0 | 0 | 0 | 1 | x | x | x | x | x | x | x | x | x | x | x | x | x | 1 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 1 | 1 | 0 | 1 | |

| 1 | 0 | 0 | 0 | 0 | 1 | x | x | x | x | x | x | x | x | x | x | x | x | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 1 | 1 | 0 | 0 | |

| 1 | 0 | 0 | 0 | 0 | 0 | 1 | x | x | x | x | x | x | x | x | x | x | x | 0 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 1 | 0 | 1 | 1 | |

| 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | x | x | x | x | x | x | x | x | x | x | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | |

| 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | x | x | x | x | x | x | x | x | x | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 1 | 0 | 0 | 1 | |

| 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | x | x | x | x | x | x | x | x | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 1 | 0 | 0 | 0 | |

| 1 | EI 0 = EO 1 = 1 EI_0=EO_1=1EEU0=EO1=1(peça 0 trabalho) | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | x | x | x | x | x | x | x | 0 | 0 | 0 | 1 | 1 | 1 | 1 (a entrada do chip 1 é toda 0) | 0 | 0 (Codificação inválida para fatia 1) | 1 | 0 L 3 = GS 1 L_3 = GS_1eu3=GS1 | 1 Eu 2 = Y 2 0 Eu_2 = Y2_0eu2=E20 | 1 L 1 = Y 1 0 L_1 = Y1_0eu1=E10 | 1 Eu 0 = Y 0 0 L_0 =Y0_0eu0=E00 | |

| 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | x | x | x | x | x | x | 0 | 0 | 0 | 1 | 1 | 0 | 1 | 0 | 0 | 1 | 0 | 1 | 1 | 0 | |

| 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | x | x | x | x | x | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 0 | 1 | 0 | 1 | 0 | 1 | |

| 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | x | x | x | x | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 0 | 1 | 0 | 1 | 0 | 0 | |

| 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | x | x | x | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 0 | 1 | 0 | 0 | 1 | 1 | |

| 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | x | x | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 0 | 1 | 0 | 0 | 1 | 0 | |

| 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | x | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 1 | |

| 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | |

| 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 (a entrada do chip 0 é toda 0) | 0 | 0 (codificação inválida da fatia 0) | 0 | 0 | 0 | 0 |

| digitar | saída | |||||

| /E | Um_1 | Um_0 | /Y_3 | /Y_2 | /Y_1 | /Y_0 |

| 1 proibido | X | X | 1 | 1 | 1 | 1 |

| 0 habilitar | 0 | 0 | 1 | 1 | 1 | 0 baixo ativo |

| 0 habilitar | 0 | 1 | 1 | 1 | 0 baixa eficácia | 1 |

| 0 habilitar | 1 | 0 | 1 | 0 baixo ativo | 1 | 1 |

| 0 habilitar | 1 | 1 | 0 baixo ativo | 1 | 1 | 1 |

Y 0 ‾ = E ‾ ‾ ⋅ A 1 ‾ ⋅ A 0 ‾ ‾ sobrelinha{Y_0} = sobrelinha{sobrelinha{sobrelinha{E}}·sobrelinha{A_1}·sobrelinha{A_0}}E0=E⋅A1⋅A0 //00

Y 1 ‾ = E ‾ ‾ ⋅ A 1 ‾ ⋅ A 0 ‾ sobrelinha{Y_1} = sobrelinha{sobrelinha{sobrelinha{E}}·sobrelinha{A_1}·A_0}E1=E⋅A1⋅A0 //01

Y 2 ‾ = E ‾ ‾ ⋅ A 1 ⋅ A 0 ‾ ‾ sobrelinha{Y_2} = sobrelinha{sobrelinha{sobrelinha{E}}·A_1·sobrelinha{A_0}}E2=E⋅A1⋅A0 //10

Y 3 ‾ = E ‾ ‾ ⋅ A 1 ⋅ A 0 ‾ sobrelinha{Y_3} = sobrelinha{sobrelinha{sobrelinha{E}}·A_1·A_0}E3=E⋅A1⋅A0 //11

Y 0 ‾ = E 3 ⋅ E 2 ‾ ‾ ⋅ E 1 ‾ ‾ ⋅ A 2 ‾ ⋅ A 1 ‾ ⋅ A 0 ‾ ‾ sobrelinha{Y_0} = sobrelinha{E_3·sobrelinha{sobrelinha{E_2}}·sobrelinha{sobrelinha{E_1}}·sobrelinha{A_2}·sobrelinha{A_1}·sobrelinha{A_0}}E0=E3⋅E2⋅E1⋅A2⋅A1⋅A0 //000

Y 1 ‾ = E 3 ⋅ E 2 ‾ ‾ ⋅ E 1 ‾ ‾ ⋅ A 2 ‾ ⋅ A 1 ‾ ⋅ A 0 ‾ sobrelinha{Y_1} = sobrelinha{E_3·sobrelinha{sobrelinha{E_2}}·sobrelinha{sobrelinha{E_1}}·sobrelinha{A_2}·sobrelinha{A_1}·A_0}E1=E3⋅E2⋅E1⋅A2⋅A1⋅A0 //001

Y 2 ‾ = E 3 ⋅ E 2 ‾ ‾ ⋅ E 1 ‾ ‾ ⋅ A 2 ‾ ⋅ A 1 ⋅ A 0 ‾ ‾ sobrelinha{Y_2} = sobrelinha{E_3·sobrelinha{sobrelinha{E_2}}·sobrelinha{sobrelinha{E_1}}·sobrelinha{A_2}·A_1·sobrelinha{A_0}}E2=E3⋅E2⋅E1⋅A2⋅A1⋅A0 //010

Y 3 ‾ = E 3 ⋅ E 2 ‾ ‾ ⋅ E 1 ‾ ‾ ⋅ A 2 ‾ ⋅ A 1 ⋅ A 0 ‾ sobrelinha{Y_3} = sobrelinha{E_3·sobrelinha{sobrelinha{E_2}}·sobrelinha{sobrelinha{E_1}}·sobrelinha{A_2}·A_1·A_0}E3=E3⋅E2⋅E1⋅A2⋅A1⋅A0 //011

Y 4 ‾ = E 3 ⋅ E 2 ‾ ‾ ⋅ E 1 ‾ ‾ ⋅ A 2 ⋅ A 1 ‾ ⋅ A 0 ‾ ‾ sobrelinha{Y_4} = sobrelinha{E_3·sobrelinha{sobrelinha{E_2}}·sobrelinha{sobrelinha{E_1}}·A_2·sobrelinha{A_1}·sobrelinha{A_0}}E4=E3⋅E2⋅E1⋅A2⋅A1⋅A0 //100

Y 5 ‾ = E 3 ⋅ E 2 ‾ ‾ ⋅ E 1 ‾ ‾ ⋅ A 2 ⋅ A 1 ‾ ⋅ A 0 ‾ sobrelinha{Y_5} = sobrelinha{E_3·sobrelinha{sobrelinha{E_2}}·sobrelinha{sobrelinha{E_1}}·A_2·sobrelinha{A_1}·A_0}E5=E3⋅E2⋅E1⋅A2⋅A1⋅A0 //101

Y 6 ‾ = E 3 ⋅ E 2 ‾ ‾ ⋅ E 1 ‾ ‾ ⋅ A 2 ⋅ A 1 ⋅ A 0 ‾ ‾ sobrelinha{Y_6} = sobrelinha{E_3·sobrelinha{sobrelinha{E_2}}·sobrelinha{sobrelinha{E_1}}·A_2·A_1·sobrelinha{A_0}}E6=E3⋅E2⋅E1⋅A2⋅A1⋅A0 //110

Y 7 ‾ = E 3 ⋅ E 2 ‾ ‾ ⋅ E 1 ‾ ‾ ⋅ A 2 ⋅ A 1 ⋅ A 0 ‾ sobrelinha{Y_7} = sobrelinha{E_3·sobrelinha{sobrelinha{E_2}}·sobrelinha{sobrelinha{E_1}}·A_2·A_1·A_0}E7=E3⋅E2⋅E1⋅A2⋅A1⋅A0 //111

L = A ‾ ⋅ C ‾ + A ⋅ B = A ‾ ⋅ B ‾ ⋅ C ‾ + A ‾ ⋅ B ⋅ C ‾ + A ⋅ B ⋅ C ‾ + ABC = m 0 + m 2 + m 6 + m 7 L=sobrelinha{A}·sobrelinha{C}+A·B =sobrelinha{A}·sobrelinha{B}·sobrelinha{C}+sobrelinha{A}·B·sobrelinha{C} + A·B·sobrelinha{C}+ABC = m_0+m_2+m_6+m_7eu=A⋅C+A⋅B=A⋅B⋅C+A⋅B⋅C+A⋅B⋅C+AAC=eu0+eu2+eu6+eu7

Y 0 ‾ = E 3 ⋅ E 2 ‾ ‾ ⋅ E 1 ‾ ‾ ⋅ A 2 ‾ ⋅ A 1 ‾ ⋅ A 0 ‾ ‾ = E 3 ⋅ E 2 ‾ ‾ ⋅ E 1 ‾ ‾ ⋅ m 0 ‾ sobrelinha{Y_0} = sobrelinha{E_3·sobrelinha{sobrelinha{E_2}}·sobrelinha{sobrelinha{E_1}}·sobrelinha{A_2}·sobrelinha{A_1}·sobrelinha{A_0}} = sobrelinha{E_3·sobrelinha{sobrelinha{E_2}}·sobrelinha{sobrelinha{E_1}}·m_0}E0=E3⋅E2⋅E1⋅A2⋅A1⋅A0=E3⋅E2⋅E1⋅eu0 //000

Y 1 ‾ = E 3 ⋅ E 2 ‾ ‾ ⋅ E 1 ‾ ‾ ⋅ A 2 ‾ ⋅ A 1 ‾ ⋅ A 0 ‾ = E 3 ⋅ E 2 ‾ ‾ ⋅ E 1 ‾ ‾ ⋅ m 1 ‾ sobrelinha{Y_1} = sobrelinha{E_3·sobrelinha{sobrelinha{E_2}}·sobrelinha{sobrelinha{E_1}}·sobrelinha{A_2}·sobrelinha{A_1}·A_0} = sobrelinha{E_3·sobrelinha{sobrelinha{E_2}}·sobrelinha{sobrelinha{E_1}}·m_1}E1=E3⋅E2⋅E1⋅A2⋅A1⋅A0=E3⋅E2⋅E1⋅eu1 //001

Y 2 ‾ = E 3 ⋅ E 2 ‾ ‾ ⋅ E 1 ‾ ‾ ⋅ A 2 ‾ ⋅ A 1 ⋅ A 0 ‾ ‾ = E 3 ⋅ E 2 ‾ ‾ ⋅ E 1 ‾ ‾ ⋅ m 2 ‾ sobrelinha{Y_2} = sobrelinha{E_3·sobrelinha{sobrelinha{E_2}}·sobrelinha{sobrelinha{E_1}}·sobrelinha{A_2}·A_1·sobrelinha{A_0}}= sobrelinha{E_3·sobrelinha{sobrelinha{E_2}}·sobrelinha{sobrelinha{E_1}}·m_2}E2=E3⋅E2⋅E1⋅A2⋅A1⋅A0=E3⋅E2⋅E1⋅eu2 //010

Y 3 ‾ = E 3 ⋅ E 2 ‾ ‾ ⋅ E 1 ‾ ‾ ⋅ A 2 ‾ ⋅ A 1 ⋅ A 0 ‾ = E 3 ⋅ E 2 ‾ ‾ ⋅ E 1 ‾ ‾ ⋅ m 3 ‾ sobrelinha{Y_3} = sobrelinha{E_3·sobrelinha{sobrelinha{E_2}}·sobrelinha{sobrelinha{E_1}}·sobrelinha{A_2}·A_1·A_0}= sobrelinha{E_3·sobrelinha{sobrelinha{E_2}}·sobrelinha{sobrelinha{E_1}}·m_3}E3=E3⋅E2⋅E1⋅A2⋅A1⋅A0=E3⋅E2⋅E1⋅eu3 //011

Y 4 ‾ = E 3 ⋅ E 2 ‾ ‾ ⋅ E 1 ‾ ‾ ⋅ A 2 ⋅ A 1 ‾ ⋅ A 0 ‾ ‾ = E 3 ⋅ E 2 ‾ ‾ ⋅ E 1 ‾ ‾ ⋅ m 4 ‾ sobrelinha{Y_4} = sobrelinha{E_3·sobrelinha{sobrelinha{E_2}}·sobrelinha{sobrelinha{E_1}}·A_2·sobrelinha{A_1}·sobrelinha{A_0}}= sobrelinha{E_3·sobrelinha{sobrelinha{E_2}}·sobrelinha{sobrelinha{E_1}}·m_4}E4=E3⋅E2⋅E1⋅A2⋅A1⋅A0=E3⋅E2⋅E1⋅eu4 //100

Y 5 ‾ = E 3 ⋅ E 2 ‾ ‾ ⋅ E 1 ‾ ‾ ⋅ A 2 ⋅ A 1 ‾ ⋅ A 0 ‾ = E 3 ⋅ E 2 ‾ ‾ ⋅ E 1 ‾ ‾ ⋅ m 5 ‾ sobrelinha{Y_5} = sobrelinha{E_3·sobrelinha{sobrelinha{E_2}}·sobrelinha{sobrelinha{E_1}}·A_2·sobrelinha{A_1}·A_0}= sobrelinha{E_3·sobrelinha{sobrelinha{E_2}}·sobrelinha{sobrelinha{E_1}}·m_5}E5=E3⋅E2⋅E1⋅A2⋅A1⋅A0=E3⋅E2⋅E1⋅eu5 //101

Y 6 ‾ = E 3 ⋅ E 2 ‾ ‾ ⋅ E 1 ‾ ‾ ⋅ A 2 ⋅ A 1 ⋅ A 0 ‾ ‾ = E 3 ⋅ E 2 ‾ ‾ ⋅ E 1 ‾ ‾ ⋅ m 6 ‾ sobrelinha{Y_6} = sobrelinha{E_3·sobrelinha{sobrelinha{E_2}}·sobrelinha{sobrelinha{E_1}}·A_2·A_1·sobrelinha{A_0}}= sobrelinha{E_3·sobrelinha{sobrelinha{E_2}}·sobrelinha{sobrelinha{E_1}}·m_6}E6=E3⋅E2⋅E1⋅A2⋅A1⋅A0=E3⋅E2⋅E1⋅eu6 //110

Y 7 ‾ = E 3 ⋅ E 2 ‾ ‾ ⋅ E 1 ‾ ‾ ⋅ A 2 ⋅ A 1 ⋅ A 0 ‾ = E 3 ⋅ E 2 ‾ ‾ ⋅ E 1 ‾ ‾ ⋅ m 7 ‾ sobrelinha{Y_7} = sobrelinha{E_3·sobrelinha{sobrelinha{E_2}}·sobrelinha{sobrelinha{E_1}}·A_2·A_1·A_0}= sobrelinha{E_3·sobrelinha{sobrelinha{E_2}}·sobrelinha{sobrelinha{E_1}}·m_7}E7=E3⋅E2⋅E1⋅A2⋅A1⋅A0=E3⋅E2⋅E1⋅eu7 //111

Certifique-se de E 3 = 1 , E 2 = 0 , E 1 = 0 Certifique-se de E_3=1,E_2=0,E_1=0certificar-seE3=1,E2=0,E1=0, isto é Y 0 ‾ = m 0 ‾ , Y 2 ‾ = m 2 ‾ , Y 6 ‾ = m 6 ‾ , Y 7 ‾ = m 7 ‾ sobrelinha{Y_0}=sobrelinha{m_0},sobrelinha{Y_2}=sobrelinha{m_2},sobrelinha{Y_6}=sobrelinha{m_6},sobrelinha{Y_7}=sobrelinha{m_7}E0=eu0,E2=eu2,E6=eu6,E7=eu7。

Transforme funções lógicas de acordo com a lei de inversão

L = L ‾ ‾ = m 0 + m 2 + m 6 + m 7 ‾ ‾ = m 0 ‾ ⋅ m 2 ‾ ⋅ m 6 ‾ ⋅ m 7 ‾ ‾ = m 0 + m 2 + m 6 + m 7 ‾ ‾ = Y 0 ‾ ⋅ Y 2 ‾ ⋅ Y 6 ‾ ⋅ Y 7 ‾ ‾ L=sobrelinha{sobrelinha{L}} = sobrelinha{sobrelinha{m_0+m_2+m_6+m_7}} = sobrelinha{sobrelinha{m_0}·sobrelinha{m_2}·sobrelinha{m_6}·sobrelinha{m_7}} = sobrelinha{sobrelinha{m_0+m_2+m_6+m_7}} = sobrelinha{sobrelinha{Y_0}·sobrelinha{Y_2}·sobrelinha{Y_6}·sobrelinha{Y_7}}eu=eu=eu0+eu2+eu6+eu7=eu0⋅eu2⋅eu6⋅eu7=eu0+eu2+eu6+eu7=E0⋅E2⋅E6⋅E7

Obtenha o diagrama lógico

774HC42

4 entradas

10 terminais de saída, a saída está ativa em nível baixo, correspondendo aos números decimais 0~9.

4 terminais de entrada, um total de 16 situações

apenas m 0 , m 1 , m 2 . . . . . . m 9 m_0 ,m_1,m_2......m_9eu0,eu1,eu2......eu9É uma entrada válida (o pino de saída correspondente produz 0 baixo e as outras saídas são 1 alto).

Entre os 6 restantes m 10 , m 11 , m 12 . . . . . . m 15 m_{10} ,m_{11},m_{12}......m_{15}eu10,eu11,eu12......eu15Isso significa que não há saída de decodificação válida (quando inválida, a saída é alta 1).

Desenhe os diagramas de forma de onda de entrada e saída do 74HC42.

Princípio de exibição de tubo digital

Decodificador de display integrado de sete segmentos. 74HC4511 (cátodo comum) (o nível alto acende)

O OeuEAtivação de trava

LT ‾ sobrelinhado{LT}euEentrada de teste da lâmpada quando LT ‾ = 0 sobrelinha{LT}=0euE=0Quando , ag gera tudo 1 e exibe a fonte "8".

BL ‾ sobrelinhado{BL}BeuEntrada de luz apagada, quando LT ‾ = 1 e BL ‾ = 1 linha superior{LT}=1 e linha superior{BL}=1euE=1,eBeu=1 Quando , ag todas as saídas 0. Pode ser usado para extinguir zero "0" desnecessário exibido.

E 3 E 2 E 1 E 0 E_3E_2E_1E_0E3E2E1E0=0000, o glifo de saída correspondente "0"

E 3 E 2 E 1 E 0 E_3E_2E_1E_0E3E2E1E0=0001, a fonte de saída correspondente "1"

E 3 E 2 E 1 E 0 E_3E_2E_1E_0E3E2E1E0=0010, a fonte de saída correspondente "2"

E 3 E 2 E 1 E 0 E_3E_2E_1E_0E3E2E1E0=0011, a fonte de saída correspondente "3"

E 3 E 2 E 1 E 0 E_3E_2E_1E_0E3E2E1E0=0100, a fonte de saída correspondente "4"

E 3 E 2 E 1 E 0 E_3E_2E_1E_0E3E2E1E0=0101, a fonte de saída correspondente "5"

E 3 E 2 E 1 E 0 E_3E_2E_1E_0E3E2E1E0=0110, a fonte de saída correspondente "6"

E 3 E 2 E 1 E 0 E_3E_2E_1E_0E3E2E1E0=0111, a fonte de saída correspondente "7"

E 3 E 2 E 1 E 0 E_3E_2E_1E_0E3E2E1E0=1000, a fonte de saída correspondente "8"

E 3 E 2 E 1 E 0 E_3E_2E_1E_0E3E2E1E0=1001, a fonte de saída correspondente "9"

1010-1111, desligado

De um para muitos, os dados na linha de dados comum são enviados para diferentes canais conforme necessário.

Semelhante a "interruptor multithrow monopolar"

Usando um decodificador de endereço exclusivo, implemente o alocador de dados

Por exemplo, 74x138 integra um decodificador de 3 a 8 linhas.

E 1 ‾ como linha de entrada de dados{E_1} como entrada de dadosE1como entrada de dados

S 0 S 1 S 2 S 3 S 4 S 5 S 6 S 7 S_0 S_1 S_2S_3S_4S_5S_6S_7E0E1E2E3E4E5E6E78 canais como saída de dados

Y 2 ‾ = E 3 ⋅ E 2 ‾ ‾ ⋅ E 1 ‾ ‾ ⋅ A 2 ‾ ⋅ A 1 ⋅ A 0 ‾ ‾ sobrelinha{Y_2} = sobrelinha{E_3·sobrelinha{sobrelinha{E_2}}·sobrelinha{sobrelinha{E_1}}·sobrelinha{A_2}·A_1·sobrelinha{A_0}}E2=E3⋅E2⋅E1⋅A2⋅A1⋅A0 //010

Na foto acima, E 3 = 1 , E 2 ‾ = 0 E_3=1,sobrelinha{E_2}=0E3=1,E2=0, quando a linha de endereço Um 2 Um 1 Um 0 = 010 Um_2Um_1Um_0=010A2A1A0=010hora, Y 2 ‾ = E 1 ‾ sobrelinha{Y_2}=sobrelinha{E_1}E2=E1

Da mesma forma podemos concluir:

Quando a linha de endereço Um 2 Um 1 Um 0 = 000 Um_2Um_1Um_0=000A2A1A0=000hora, Y 0 ‾ = E 1 ‾ = D sobrelinha{Y_0}=sobrelinha{E_1}=DE0=E1=E,outro Y x = 1 Y_x=1Ex=1。

Quando a linha de endereço Um 2 Um 1 Um 0 = 001 Um_2Um_1Um_0=001A2A1A0=001hora, Y 1 ‾ = E 1 ‾ = D sobrelinha{Y_1}=sobrelinha{E_1}=DE1=E1=E,outro Y x = 1 Y_x=1Ex=1。

Quando a linha de endereço Um 2 Um 1 Um 0 = 010 Um_2Um_1Um_0=010A2A1A0=010hora, Y 2 ‾ = E 1 ‾ = D sobrelinha{Y_2}=sobrelinha{E_1}=DE2=E1=E,outro Y x = 1 Y_x=1Ex=1。

Quando a linha de endereço Um 2 Um 1 Um 0 = 011 Um_2Um_1Um_0=011A2A1A0=011hora, Y 3 ‾ = E 1 ‾ = D sobrelinha{Y_3}=sobrelinha{E_1}=DE3=E1=E,outro Y x = 1 Y_x=1Ex=1。

Quando a linha de endereço Um 2 Um 1 Um 0 = 100 Um_2Um_1Um_0=100A2A1A0=100hora, Y 4 ‾ = E 1 ‾ = D sobrelinha{Y_4}=sobrelinha{E_1}=DE4=E1=E,outro Y x = 1 Y_x=1Ex=1。

Quando a linha de endereço Um 2 Um 1 Um 0 = 101 Um_2Um_1Um_0=101A2A1A0=101hora, Y 5 ‾ = E 1 ‾ = D sobrelinha{Y_5}=sobrelinha{E_1}=DE5=E1=E,outro Y x = 1 Y_x=1Ex=1。

Quando a linha de endereço Um 2 Um 1 Um 0 = 110 Um_2Um_1Um_0=110A2A1A0=110hora, Y 6 ‾ = E 1 ‾ = D sobrelinha{Y_6}=sobrelinha{E_1}=DE6=E1=E,outro Y x = 1 Y_x=1Ex=1。

Quando a linha de endereço Um 2 Um 1 Um 0 = 111 Um_2Um_1Um_0=111A2A1A0=111hora, Y 7 ‾ = E 1 ‾ = D sobrelinha{Y_7}=sobrelinha{E_1}=DE7=E1=E,outro Y x = 1 Y_x=1Ex=1。

Y = S 2 ‾ ⋅ S 1 ‾ ⋅ S 0 ‾ ⋅ D 0 + S 2 ‾ ⋅ S 1 ‾ ⋅ S 0 ⋅ D 1 + S 2 ‾ ⋅ S 1 ⋅ S 0 ‾ ⋅ D 2 + S 2 ‾ ⋅ S 1 ⋅ S 0 ⋅ D 3 + S 2 ⋅ S 1 ‾ ⋅ S 0 ‾ ⋅ D 4 + S 2 ⋅ S 1 ‾ ⋅ S 0 ⋅ D 5 + S 2 ⋅ S 1 ⋅ S 0 ‾ ⋅ D 6 + S 2 ⋅ S 1 ⋅ S 0 ⋅ D 7 Y=sobrelinha{S_2}·sobrelinha{S_1}·sobrelinha{S_0}·D_0 +sobrelinha{S_2}·sobrelinha{S_1}·S_0·D_1 +sobrelinha{S_2}·S_1·sobrelinha{S_0}·D_2 +sobrelinha{S_2}·S_1·S_0·D_3 +S_2·sobrelinha{S_1}·sobrelinha{S_0}·D_4 +S_2·sobrelinha{S_1}·S_0·D_5 +S_2·S_1·sobrelinha{S_0}·D_6 +S_2·S_1·S_0·D_7E=S2⋅S1⋅S0⋅E0+S2⋅S1⋅S0⋅E1+S2⋅S1⋅S0⋅E2+S2⋅S1⋅S0⋅E3+S2⋅S1⋅S0⋅E4+S2⋅S1⋅S0⋅E5+S2⋅S1⋅S0⋅E6+S2⋅S1⋅S0⋅E7

Extensões para seletores de dados.

gerador de função lógica

Seletor de dados 8 para 1 conhecido.

Y = S 2 ‾ ⋅ S 1 ‾ ⋅ S 0 ‾ ⋅ D 0 + S 2 ‾ ⋅ S 1 ‾ ⋅ S 0 ⋅ D 1 + S 2 ‾ ⋅ S 1 ⋅ S 0 ‾ ⋅ D 2 + S 2 ‾ ⋅ S 1 ⋅ S 0 ⋅ D 3 + S 2 ⋅ S 1 ‾ ⋅ S 0 ‾ ⋅ D 4 + S 2 ⋅ S 1 ‾ ⋅ S 0 ⋅ D 5 + S 2 ⋅ S 1 ⋅ S 0 ‾ ⋅ D 6 + S 2 ⋅ S 1 ⋅ S 0 ⋅ D 7 Y=sobrelinha{S_2}·sobrelinha{S_1}·sobrelinha{S_0}·D_0 +sobrelinha{S_2}·sobrelinha{S_1}·S_0·D_1 +sobrelinha{S_2}·S_1·sobrelinha{S_0}·D_2 +sobrelinha{S_2}·S_1·S_0·D_3 +S_2·sobrelinha{S_1}·sobrelinha{S_0}·D_4 +S_2·sobrelinha{S_1}·S_0·D_5 +S_2·S_1·sobrelinha{S_0}·D_6 +S_2·S_1·S_0·D_7E=S2⋅S1⋅S0⋅E0+S2⋅S1⋅S0⋅E1+S2⋅S1⋅S0⋅E2+S2⋅S1⋅S0⋅E3+S2⋅S1⋅S0⋅E4+S2⋅S1⋅S0⋅E5+S2⋅S1⋅S0⋅E6+S2⋅S1⋅S0⋅E7

E = m 0 ⋅ D 0 + m 1 ⋅ D 1 + m 2 ⋅ D 2 + m 3 ⋅ D 3 + m 4 ⋅ D 4 + m 5 ⋅ D 5 + m 6 ⋅ D 6 + m 7 ⋅ D 7 E=m_0·D_0 +m_1·D_1 +m_2·D_2 +m_3·D_3 +m_4·D_4 +m_5·D_5 +m_6·D_6 +m_7·D_7E=eu0⋅E0+eu1⋅E1+eu2⋅E2+eu3⋅E3+eu4⋅E4+eu5⋅E5+eu6⋅E6+eu7⋅E7

função lógica L = A ‾ BC + AB ‾ C + ABL=sobrelinha{A}BC+Asobrelinha{B}C+ABeu=AAC+ABC+AB

L = A ‾ BC + AB ‾ C + AB = A ‾ BC + AB ‾ C + ABC ‾ + ABC = m 3 + m 5 + m 6 + m 7 L=sobrelinha{A}BC+Asobrelinha{B}C+AB=sobrelinha{A}BC+Asobrelinha{B}C+ABsobrelinha{C}+ABC=m_3+m_5+m_6+m_7eu=AAC+ABC+AB=AAC+ABC+ABC+AAC=eu3+eu5+eu6+eu7

Use o seletor de dados 8 para 1 para implementar a função L acima

L = Y = m 3 + m 5 + m 6 + m 7 , onde D 7 D 6 D 5 D 3 = 1111 , D 4 D 2 D 1 D 0 = 0000 L=Y=m_3+m_5+m_6+m_7, Entre eles D_7D_6D_5D_3=1111, D_4D_2D_1D_0=0000eu=E=eu3+eu5+eu6+eu7,emE7E6E5E3=1111,E4E2E1E0=0000

Dados paralelos a dados seriais

| A | B | FA > B F_{A>B}FA>B | FA < B F_{AFA<B | FA = = B F_{A==B}FA==B |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 1 |

| 0 | 1 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 0 |

| 1 | 1 | 0 | 0 | 1 |

| Um 1 ? B 1 Um _1?B_1A1?B1 | Um 0 ? B 0 A_0?B_0A0?B0 | FA > B F_{A>B}FA>B | FA < B F_{AFA<B | FA = = B F_{A==B}FA==B |

|---|---|---|---|---|

| Um 1 > B 1 A_1>B_1A1>B1 | x | 1 | 0 | 0 |

| Um 1 < B 1 A_1A1<B1 | x | 0 | 1 | 0 |

| Um 1 = = B 1 Um 1 == B 1A1==B1 | Um 0 > B 0 A_0>B_0A0>B0 | 1 | 0 | 0 |

| Um 1 = = B 1 Um 1 == B 1A1==B1 | Um 0 < B 0 A_0A0<B0 | 0 | 1 | 0 |

| Um 1 = = B 1 Um 1 == B 1A1==B1 | Um 0 = = B 0 A_0==B_0A0==B0 | 0 | 0 | 1 |

expressão lógica

FA > B = FA 1 > B 1 + FA 1 = = B 1 ⋅ FA 0 > B 0 F_{A>B} = F_{A_1>B_1} +F_{A_1==B_1}·F_{A_0>B_0}FA>B=FA1>B1+FA1==B1⋅FA0>B0

FA < B = FA 1 < B 1 + FA 1 = = B 1 ⋅ FA 0 < B 0 F_{AFA<B=FA1<B1+FA1==B1⋅FA0<B0

FA = = B = FA 1 = = B 1 ⋅ FA 0 = = B 0 F_{A==B} = F_{A_1==B_1}·F_{A_0==B_0}FA==B=FA1==B1⋅FA0==B0

diagrama lógico

Conexão em série, expandida para comparador numérico de 8 bits

Conexão paralela, expandida para comparador numérico de 16 bits.

Quando conectado em paralelo, a velocidade é rápida.