2024-07-12

한어Русский языкEnglishFrançaisIndonesianSanskrit日本語DeutschPortuguêsΕλληνικάespañolItalianoSuomalainenLatina

Tällä hetkellä FPGA:lle on olemassa kaksi ratkaisua SDI-videokoodauksen ja -dekoodauksen toteuttamiseen: yksi on käyttää erillisiä koodaus- ja dekoodaussiruja, kuten tyypillinen vastaanotin GS2972, ja lähetin GS2972. Etuna on esimerkiksi GS2971-vastaanotin dekoodaa SDI:n rinnakkaiseksi YCrCb422:ksi ja GS2972 lähettää Laite koodaa rinnakkaisen YCrCb422:n suoraan SDI-videoksi FPGA-logiikkaresurssien osasto toteuttamaan SDI-koodauksen ja dekoodauksen ja käyttämään Xilinx-sarjan FPGA:n GTP/GTX-resursseja resursseja hyödynnetään kohtuullisesti ja GTP/GTX-resursseja ei käytetä turhaan. Mielenkiintoista on, että näillä kahdella ratkaisulla on vastaavat ratkaisut täällä tässä blogissa, mukaan lukien laitteiston FPGA-kehityslevyt, suunnittelun lähdekoodi jne.

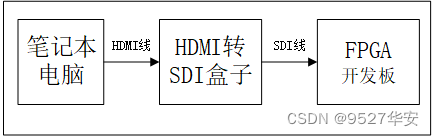

Tämä suunnittelu perustuu Zynq-sarjan Zynq7100 FPGA -kehityskorttiin, joka toteuttaa SDI-videokoodauksen ja -dekoodauksen + kuvan skaalaus + monikanavainen videoliitos. Tulolähdettä on kaksi, joista toinen on 3G-SDI-kamera, jonka resoluutio on 1920x1080@. 60 Hz, ja HD-SDI voidaan käyttää myös tai SD-SDI-kamera, koska tämä malli on mukautuva kolmeen toiseen HDMI-3G-SDI-laatikkoon, joka on kytketty kannettavaan SDI-kameran simuloimiseksi; SDI-videot liitetään FPGA-kehityslevyyn koaksiaalikaapelin BNC-liittimen kautta, ja sitten koaksiaalivideo kulkee sisäisen Gv8601a-sirun läpi toteuttaakseen yksipäisen muuntamisen differentiaali- ja balansoituihin taajuuskorjauksiin, minkä jälkeen differentiaalinen SDI-videosignaali tulee GTX:hen nopea resurssi FPGA:n sisällä nopean sarjamuunnoksen toteuttamiseksi. Bo kutsuu sitä deserialisoinniksi, ja sitten deserialisoitu rinnakkaisvideo lähetetään Xilinx-sarjan FPGA:n ainutlaatuiseen SMPTE SD/HD/3G SDI IP -ytimeen SDI:n suorittamiseksi. videon dekoodaustoiminto ja BT1120-videon lähtö Tässä vaiheessa SDI-videon dekoodaus on valmis ja voit suorittaa rutiininomaisia kuvankäsittelytoimintoja.

Tämän suunnittelun tarkoituksena on tuottaa dekoodattua SDI-videota kuvan skaalauksen + monikanavaisen videofuusion ja superposition jälkeen. Tämä blogi on suunnitellut kaksi lähtötapaa, joista toinen on HDMI-lähtö ja toinen on 3G-SDI-lähtö, molemmat menetelmät vaativat BT1120-videon dekoodauksen muuttamiseksi RGB:ksi ja kuvien välimuistitoiminnot, joissa käytetään BT1120-RGB-moduulia videomuodon muuntamiseksi kuvien välimuisti ja välimuisti Media on PS-puolen DDR3, ensimmäinen SDI-video kirjoitetaan DDR:hen VDMA:n kautta ja sitten luetaan ja lähetetään videofuusiopäällysmoduuliin. Toista SDI-videota ei lueta DDR:n kautta VDMA, mutta on peitetty videofuusion kautta. Moduuli lukee DDR3:sta. Tässä vaiheessa 2-kanavainen video on siirtynyt fuusio- ja peittomoduuliin ja lähettää sitten HDMI-näytön , joka on HDMI-lähtömenetelmä tai videomuoto toteutetaan RGB-BT1120-moduulin muuntamisen kautta, sitten video siirtyy SMPTE SD/HD/3G SDI -IP-ytimeen, suorittaa SDI-videokoodaustoiminnot ja lähettää SDI-videon. FPGA:n sisällä olevien nopeiden GTX-resurssien kautta toteuttaakseen rinnakkaisten tietojen muuntamisen nopeaksi sarjaportiksi, jota tämä blogi kutsuu sarjaksi. Differentiaalinen nopea signaali tulee sitten sisäiseen Gv8500-siruun toteuttaakseen differentiaalimuunnoksen toiminnot yksittäiseksi. -päättyi ja ajurin lisäys SDI-video lähetetään FPGA-kehityslevyn BNC-liitännän kautta, ja se on kytketty SDI-HDMI-koteloon HDMI-näytön SDI-lähtötavan kautta sarjat projektin lähdekoodit seuraavasti:

Yllä olevat kaksi projektin lähdekoodisarjaa selitetään seuraavasti lukijoiden ymmärtämisen helpottamiseksi:

Projektin lähdekoodi 1

Kehityslevyn FPGA-malli on Xilinx->Xilinx-Zynq7100-xc7z100ffg900-2, yksi on 3G-SDI-kamera, jonka resoluutio on 1920x1080@60Hz, ja toinen on HDMI - 3G-SDI; Boksi on kytketty kannettavaan SDI-kameraan, jonka resoluutio on 1920 x 1080 @ 60 Hz kahden GTX-kanavan kautta SDI-video sarjoitetaan rinnakkaisdataksi. Sitten SDI dekoodataan kahdeksi BT1120-kanavaksi ja sitten BT1120 muunnetaan RGB-moduuliksi; RGB888-videoon ja sitten 2-kanavaisen Xilinx-virallisen Video In To AXI4-Stream IP -ytimen kautta RGB888-tietojen muuntamiseksi AXI4-Stream-tietovirtaan ja kirjoita sitten video PS-puolen DDR3-välimuistiin 2-kanavaisen Xilinx-virallisen VDMA:n kautta; kuvan välimuistiratkaisu; sitten itse kehitetty HLS-pohjainen monikanavainen videofuusio- ja overlay-IP-ydin toteuttaa 2-kanavaisen videofuusio- ja päällekkäistoiminnon. Siirry sitten Xilinxin viralliseen AXI4-Stream To Video Out -IP-ydin muuntaaksesi AXI4-; Suoratoista videovirta alkuperäiseen videovirtaan ja lähetä sitten fuusiopeittovideo RGB-HDMI-moduuliin muuntaaksesi RGB888-videon HDMI-videoksi ja lähtöresoluutioksi Se on 1920 x 1080 @ 60 Hz. Katso tarkemmat näyttötehosteet artikkelin lopussa kuva näytetään HDMI-näytön kautta.

Projektin lähdekoodi 2

Kehityslevyn FPGA-malli on Xilinx->Xilinx-Zynq7100-xc7z100ffg900-2, yksi on 3G-SDI-kamera, jonka resoluutio on 1920x1080@60Hz, ja toinen on HDMI - 3G-SDI; Boksi on kytketty kannettavaan SDI-kameraan, jonka resoluutio on 1920 x 1080 @ 60 Hz kahden GTX-kanavan kautta SDI-video sarjoitetaan rinnakkaisdataksi. Sitten SDI dekoodataan kahdeksi BT1120-kanavaksi ja sitten BT1120 muunnetaan RGB-moduuliksi; RGB888-videoon ja sitten 2-kanavaisen Xilinx-virallisen Video In To AXI4-Stream IP -ytimen kautta RGB888-tietojen muuntamiseksi AXI4-Stream-tietovirtaan ja kirjoita sitten video PS-puolen DDR3-välimuistiin 2-kanavaisen Xilinx-virallisen VDMA:n kautta; kuvan välimuistiratkaisu; sitten itse kehitetty HLS-pohjainen monikanavainen videofuusio- ja overlay-IP-ydin toteuttaa 2-kanavaisen videofuusio- ja päällekkäistoiminnon. Siirry sitten Xilinxin viralliseen AXI4-Stream To Video Out -IP-ydin muuntaaksesi AXI4-; Suoratoista videovirta alkuperäiseen videovirtaan ja lähetä sitten fuusiopeittokuva RGB-BT1120-moduuliin, jotta voit muuntaa RGB888-videon BT1120-videoksi ja siirtää sitten SMPTE SD /HD/3G SDI -IP-ydin, joka koodaa BT1120-videon; sitten muuntaa SDI-rinnakkaisdatan nopeiksi sarjasignaaleiksi FPGA:n sisällä olevien nopeiden GTX-resurssien kautta ja käyttää sitten sisäänrakennettua Gv8500-sirua differentiaalimuunnoksen toteuttamiseen yksipäätteiseksi ja ohjaimeksi. lopuksi SDI-HDMI-laatikkoa käytetään liittämiseen HDMI-näyttöön. Tämä projekti vaatii SDI-SDI-skenaarioiden käyttämisen.

Tämä projekti ja sen lähdekoodi sisältävät sekä itse kirjoittamiani osia että julkisista Internet-kanavista hankittuja osia (mukaan lukien CSDN, Xilinxin virallinen verkkosivusto, Alteran virallinen verkkosivusto jne.), jos se on mielestäsi loukkaavaa, lähetä yksityisviesti osoitteeseen kritisoida ja kouluttaa tämän perusteella tämä projekti ja sen lähdekoodi on tarkoitettu vain lukijoiden tai fanien henkilökohtaiseen opiskeluun ja tutkimukseen, ja niitä ei saa käyttää kaupallisiin tarkoituksiin, jos lukijat tai fanit itse aiheuttavat oikeudellisia ongelmia , tällä blogilla ja bloggaajalla ei ole mitään tekemistä sen kanssa, joten käytä sitä varoen. . .

Blogini kotisivulla on SDI-videosarake, joka on täynnä FPGA-koodekkeja SDI-tekniikan lähdekoodia ja blogin esittelyä. Siellä on GS2971/GS2972-pohjaisia SDI-koodekkeja sekä GTP/GTX-resursseihin perustuvia SDI-koodekkeja; SDI, 6G-SDI, 12G-SDI jne. sarakkeen osoitelinkki on seuraava:

Siirry suoraan napsauttamalla

Tämä blogi on itse kehittänyt monikanavaisen videon yhdistämissovelluksen. Olen kirjoittanut blogin aiemmin. Blogin osoitelinkki on seuraava:

Siirry suoraan napsauttamalla

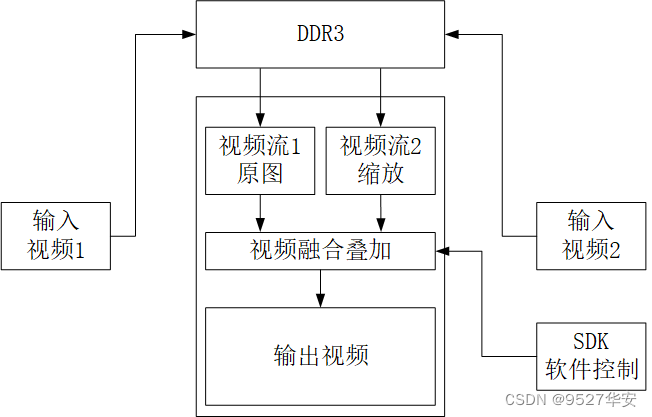

Suunnitteluperiaatteen lohkokaavio on seuraava:

Ilmoitus! ! ! !

Ilmoitus! ! ! !

Violetti nuoli: 3G-SDI-lähtöpolku

Punainen nuoli: HDMI-lähtöpolku

On olemassa kaksi SDI-tulolaitetta, jotka on kytketty FPGA-kehityslevyn 2-suuntaiseen SDI-videotuloliitäntään, yksi on 3G-SDI-kamera, jonka resoluutio on 1920x1080@60Hz voidaan käyttää tämän suunnittelun vuoksi. Se on mukautuva kolmen tyyppisiin SDI-videoihin, laatikko on liitetty kannettavaan tietokoneeseen SDI-kameran simuloimiseksi harkitse HDMI-SDI-laatikon käyttöä SDI-kameran simuloimiseen. Hezibao maksaa noin 100 yuania, kun käytät HDMI-SDI-laatikkoa. HDMI-SDI-boksi HDMI-kaapelilla ja liitä sitten HDMI-SDI-boksi SDI-kaapelilla SDI-lähtöliitäntä FPGA-kehityskorttiin on seuraava:

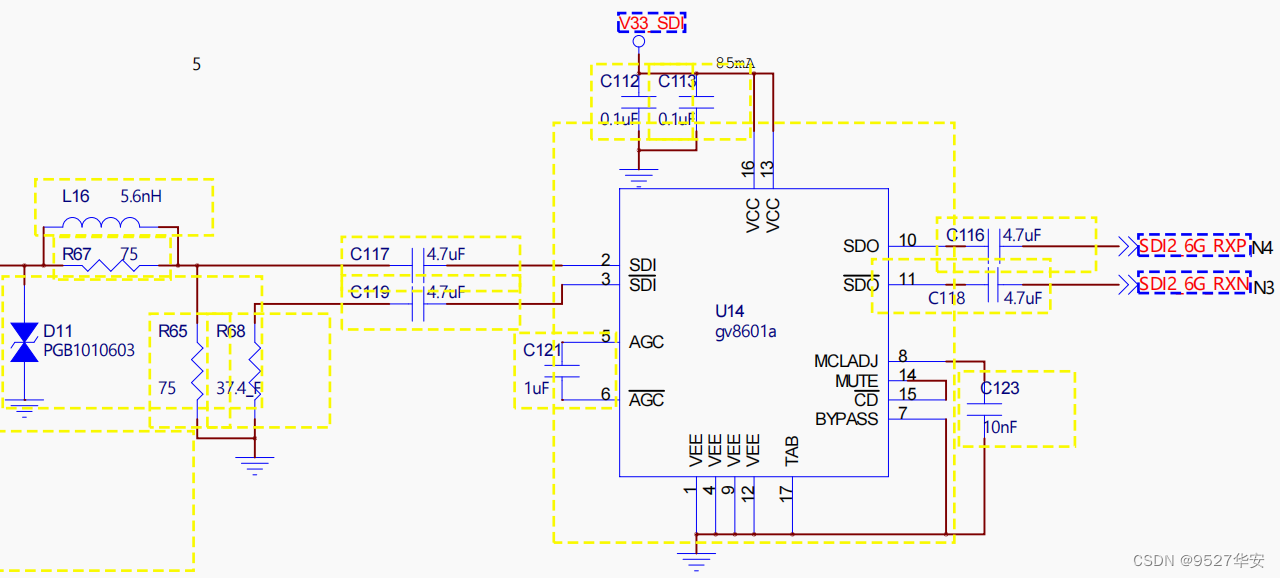

Gv8601a-siru toteuttaa yksipäisen muuntamisen differentiaaliseen ja tasapainotettuun taajuuskorjaimeen. Gv8601a on valittu tähän, koska se käyttää virallista Xilinx-ratkaisua. Gv8601a-taajuuskorjaimen kaavio on seuraava:

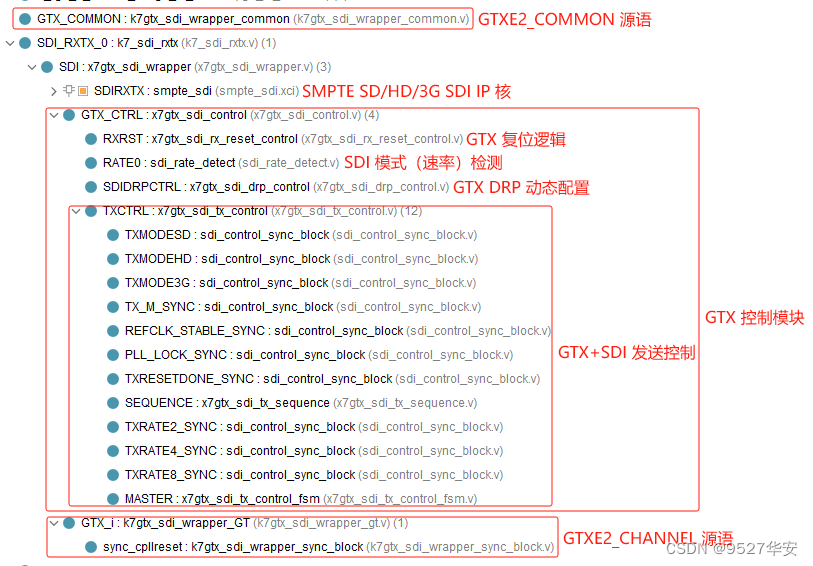

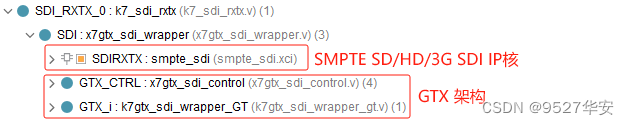

Tämä malli käyttää Xilinxin ainutlaatuisia nopeita GTX-signaalinkäsittelyresursseja SDI-differentiaalisen videosignaalin deserialisoimiseksi ja sarjoittamiseksi. SDI-videovastaanotossa GTX toimii deserialisoijana, eli dekoodaa sisäänmenon nopeat sarjadifferentiaalisignaalit rinnakkaisiksi digitaalisiksi. SDI-videolähetyksessä GTX toimii sarjoittavana eli sarjoittamalla tulon rinnakkaissignaali nopeaksi sarjadifferentiaalisignaaliksi GTX:n käyttö edellyttää yleensä GTX-IP-ytimen instantoimista käyttöliittymän konfiguroimisen kautta; käyttöliittymä, mutta tämä rakenne vaatii SD-SDI-, HD-SDI- ja 3G-SDI-videoiden automaattisen tunnistamisen ja mukautuvan käsittelyn, joten GTX:llä on oltava toiminto, joka muuttaa linjanopeutta dynaamisesti. Tämä toiminto voidaan määrittää DRP-liitännän kautta. Se voidaan määrittää myös GTX:n nopeusrajapinnan kautta, joten et voi käyttää vivadon käyttöliittymää. Sen sijaan voit luoda suoraan GTX:n lähdekielet GTXE2_CHANNEL ja GTXE2_COMMON ja käyttää GTX-resursseja suoraan. GTX-linjanopeuden dynaamiseen konfigurointiin tarvitset myös GTX-ohjausmoduulin, tämä moduuli viittaa Xilinxin viralliseen suunnittelusuunnitelmaan, ja siinä on SDI-tilan dynaaminen valvonta, DRP:n dynaaminen konfigurointi jne suunnitelma viittaa Xilinxin viralliseen suunnitteluun, GTX-sarjan sarjointi- ja serialisointimoduulin koodirakenne on seuraava:

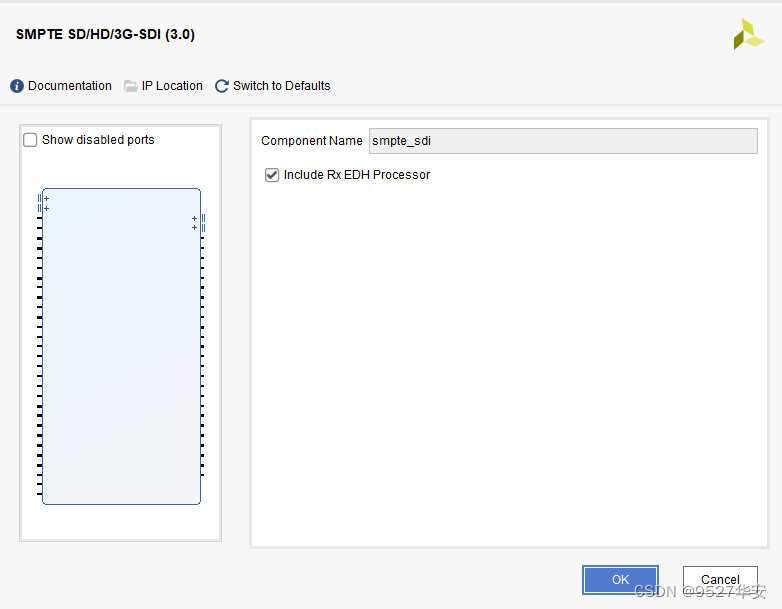

SMPTE SD/HD/3G SDI IP-ydin on ainutlaatuinen IP Xilinx-sarjan FPGA:iden SDI-videokoodaukseen ja dekoodaukseen. Vivadon käyttöliittymä on erittäin yksinkertainen.

SMPTE SD/HD/3G SDI IP-ydintä on käytettävä GTX:n kanssa SDI-videovastaanottoa varten IP vastaanottaa tiedot GTX:stä ja dekoodaa sitten SDI-videon BT1120-videolähtöön. IP vastaanottaa BT1120:n videodata käyttäjän puolelta ja koodaa sitten BT1120-videon SDI-videolähtöön. Tämä ratkaisu viittaa viralliseen Xilinx-malliin, jonka SMPTE SD/HD/3G SDI IP -ydinrakenne on seuraava:

BT1120-RGB-moduulin tehtävänä on muuntaa BT1120-videolähtö SMPTE SD/HD/3G SDI IP -ydindekoodauksella RGB888-videoksi. Se koostuu kolmesta moduulista: BT1120 - CEA861 -moduuli, YUV422 - YUV444 -moduuli ja RGB8448 -moduuli. Tämä ratkaisu viittaa BT1120-RGB-moduulin viralliseen malliin:

Tämän mallin videovälimuistiratkaisu käyttää 2-kanavaista Xilinxin virallista VDMA-kuvavälimuistiarkkitehtuuria. Välimuistiväline on PS-puolen DDR3, ensimmäinen SDI-video kirjoitetaan DDR:hen VDMA:n kautta ja lähetetään sitten videofuusiopäällysmoduuliin; Toinen SDI-video Kun DDR:ään on kirjoitettu VDMA:n kautta, sitä ei lueta ulos, vaan se luetaan DDR3:sta videofuusiopäällysmoduulin kautta. Esimerkkinä projektin lähdekoodista 1, VDMA on suunniteltu käyttämällä Xilinxin lohkosuunnittelua vivado, kuten alla näkyy:

Latenssin vähentämiseksi VDMA on asetettu välimuistiin 1 kehys seuraavasti:

Monikanavaisen videofuusiopeittokuvan lohkokaavio on seuraava:

Monikanavainen videofuusio ja peittokuva muodostetaan yhdistämällä ja päällekkäin taustalla oleva video ja peittovideo SDK-ohjelmisto määrittää dynaamisesti 2-kanavaisen videofuusion läpinäkyvyyden, peittovideon zoomauskoon, peittovideon näytön sijainnin ja muut tiedot HLS-ratkaisun C++-koodi, ja se on syntetisoitu RTL:ksi ja kapseloitu IP:ksi, jota voidaan käyttää Vivadossa. Lisätietoja tästä ratkaisusta on edellisessä blogissani.

Siirry suoraan napsauttamalla

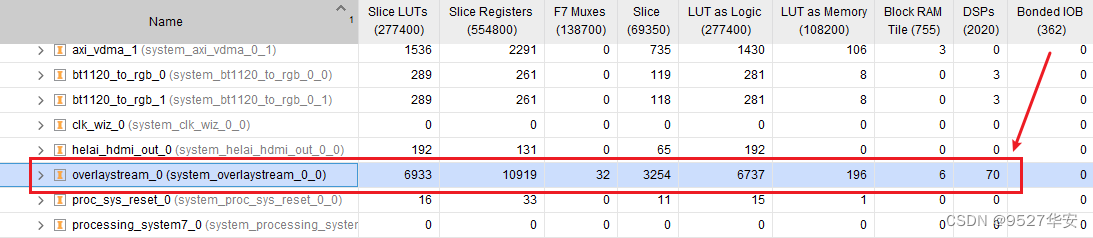

Tämän IP:n kattava resurssien käyttö in vivadossa on seuraava:

HLS-monikanavavideon peittokuvan on suoritettava ohjain- ja käyttäjäohjelma SDK:ssa toimiakseen oikein. Olen toimittanut projektiin C-kieliohjelman. Katso lisätietoja HLS-monikanavan kuvakaappauksesta. kanavan videofuusiopeittokutsu on seuraava:

HDMI-videolähtöarkkitehtuuri on seuraava:

Viitaten Xilinxin viralliseen suunnitteluun, käytä VTC+AXI4-Stream to Video Out -arkkitehtuuria muuntaaksesi ulostulovideon AXI4-Streamista alkuperäiseen muotoon ja käytä sitten RGB888-HDMI-moduulia, joka on toteutettu puhtaalla verilog-koodilla RGB888:n muuntamiseksi HDMI:ksi ja lopuksi näyttöön. sen näytön kautta, RGB888-HDMI-moduulin koodirakenne on seuraava:

Mitä tulee RGB888-HDMI-moduuliin, katso aikaisempi blogini, blogiosoite:Siirry suoraan napsauttamalla

SDI-videolähtöarkkitehtuurin on ensin muutettava VDMA:n lukema AXI4-Stream alkuperäiseen muotoon saatuaan RGB888-videon, se voi sitten muuntaa RGB:n BT1120:ksi BT1120-videoksi.

SDI-lähtötilassa VGA-ajoitusmoduulin pikselikello on SMPTE SD/HD/3G SDI -IP-ytimen lähettävän käyttäjän kello. Pikselikello on erilainen esimerkiksi 3G-SDI-tilassa , pikselikello on 148,5M HD-SDI 720P@60Hz -tilassa pikselikello on 74,25M.

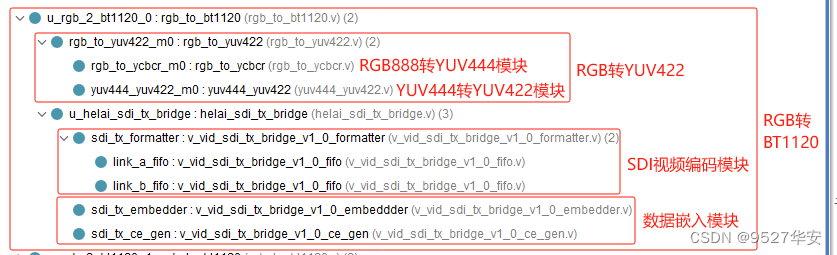

SDI-lähtötilassa RGB-BT1120-moduulia on käytettävä RGB-BT1200-moduulin tehtävänä on muuntaa käyttäjän puolella oleva RGB-video BT1200-videoksi ja lähettää se SMPTE SD/HD/3G SDI IP:hen; RGB-BT1120-moduuli koostuu RGB888-YUV444-moduulista, SDI-videokoodausmoduulista ja datan upotusmoduulista. Tämä ratkaisu viittaa Xilinx-moduulin koodirakenteeseen seuraavasti:

Nämä kaksi osaa jakavat vastaavat moduulit vastaanottoprosessin kanssa, jotka ovat toiminnallisesti vastaanottoprosessin käänteinen prosessi, eikä niitä kuvata uudelleen;

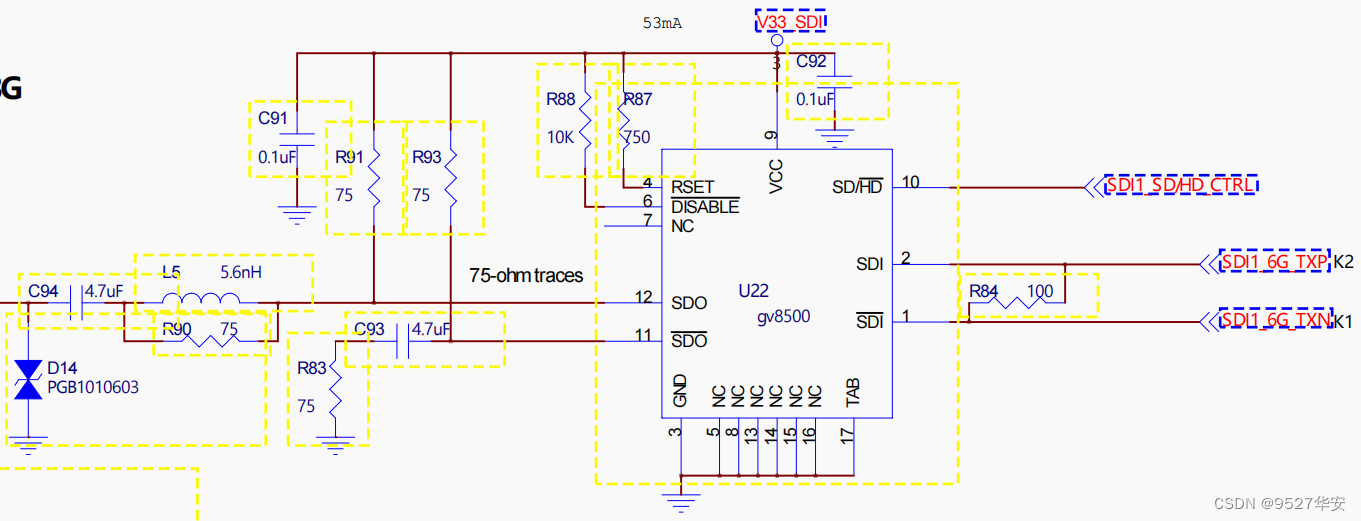

Gv8500-siru toteuttaa differentiaalimuunnostoiminnot yksipäätteiseksi ja parannelluksi ajuriksi. Gv8500 on valittu tähän, koska se käyttää virallista Xilinx-ratkaisua. Gv8500-ohjaimen kaavio on seuraava:

SDI-lähtötilassa sinun on käytettävä SDI-HDMI-laatikkoa, koska kädessäni olevalla näytöllä ei ole SDI-liitäntää, vain HDMI-liitäntä näytössäsi on SDI-liitäntä, voit suoraan Liitäntä osoittaa, että SDI-HDMI-laatikkoni ostettiin tietystä kaupasta alle 100 yuania;

Tämä blogi tarjoaa 2 sarjaa projektin lähdekoodia. Vivado Block Design -suunnittelu on seuraavanlainen.

Esimerkkinä projektin lähdekoodista 1, projektin lähdekoodin rakenne on seuraava.

Projektin lähdekoodin PL-sivukello tarjoaa Zynq-ydin, joten SDK on suoritettava Zynqin käynnistämiseksi. Lisäksi IP-ytimien, kuten videofuusiopeittokuvan ja VDMA:n, on suoritettava ohjelmisto-ajurit toimiakseen kunnolla SDK-ohjelmistokoodin rakenne on seuraava:

SDK-koodin kokoonpano on seuraava, käyttäjät voivat muokata sitä mielivaltaisesti omien tarpeidensa mukaan;

Ensimmäinen video on alimman kerroksen video, jonka resoluutio on 1920x1080;

Toinen kanavavideo on peittokuva, jonka resoluutio on 1920 x 1080. Ota 1000 x 800 alue peittokuvan koordinaateista (400, 200) peittokuvan fuusiovideon lähtökohtana.

Skaalaa edellisessä vaiheessa saatu 600 x 600 peittokuvan fuusiovideo kokoon 960 x 540;

Peitä 960 x 540 päällekkäinen fuusiovideo edellisessä vaiheessa alkaen alla olevan videon koordinaatista (0,0) ja aseta alla olevan ja päällekkäisen kerroksen läpinäkyvyydeksi 80;

Kehityslevyn FPGA-malli: Xilinx-Zynq7100–xc7z100ffg900-2;

Kehitysympäristö: Vivado2019.1;

Tulo: 3G-SDI-kamera tai HDMI-SDI-boksi, resoluutio 1920x1080@60Hz;

Lähtö: HDMI, resoluutio 1920x1080@60Hz;

Välimuistiratkaisu: Xilinxin virallinen VDMA-ratkaisu;

Välimuisti: PS-puolen DDR3;

Videofuusio- ja peittokuvaratkaisu: itse kehitetty monikanavainen videofuusio ja peittokuva, joka perustuu HLS:ään;

Projektin rooli: Tämän projektin tarkoituksena on antaa lukijoille mahdollisuus hallita Zynq-sarjan FPGA:n suunnittelukykyjä SDI:n ja HDMI:n välillä, jotta he voivat siirtää ja suunnitella omia projektejaan;

Lisätietoja projektilohkosuunnittelusta ja projektikoodiarkkitehtuurista on luvussa 3 kohdassa "Projektin lähdekoodiarkkitehtuuri";

Projektin resurssienkulutus ja virrankulutus ovat seuraavat:

Kehityslevyn FPGA-malli: Xilinx-Zynq7100–xc7z100ffg900-2;

Kehitysympäristö: Vivado2019.1;

Tulo: 3G-SDI-kamera tai HDMI-SDI-boksi, resoluutio 1920x1080@60Hz;

Lähtö: 3G-SDI, resoluutio 1920x1080@60Hz;

Välimuistiratkaisu: Xilinxin virallinen VDMA-ratkaisu;

Välimuisti: PS-puolen DDR3;

Videofuusio- ja peittokuvaratkaisu: itse kehitetty monikanavainen videofuusio ja peittokuva, joka perustuu HLS:ään;

Projektin rooli: Tämän projektin tarkoituksena on antaa lukijoille mahdollisuus hallita Zynq-sarjan FPGA:n suunnittelukykyjä SDI:n ja HDMI:n välillä, jotta he voivat siirtää ja suunnitella omia projektejaan;

Lisätietoja projektilohkosuunnittelusta ja projektikoodiarkkitehtuurista on luvussa 3 kohdassa "Projektin lähdekoodiarkkitehtuuri";

Projektin resurssienkulutus ja virrankulutus ovat seuraavat:

1: Jos vivado-versiosi on yhdenmukainen tämän projektin vivado-version kanssa, avaa projekti suoraan;

2: Jos vivado-versiosi on vanhempi kuin tämän projektin vivado-versio, sinun on avattava projekti ja napsautettava Tiedosto -> Tallenna nimellä. Tämä menetelmä ei kuitenkaan ole turvallisin tapa päivittää vivado-versiosi tämän projektin versiosta tai uudemmasta.

3: Jos vivado-versiosi on korkeampi kuin tämän projektin vivado-versio, ratkaisu on seuraava:

Projektin avaamisen jälkeen huomaat, että IP-osoitteet on lukittu seuraavasti:

Tällä hetkellä sinun on päivitettävä IP. Vaiheet ovat seuraavat:

Jos FPGA-mallisi on ristiriidassa minun kanssa, sinun on vaihdettava FPGA-malli seuraavasti:

FPGA-mallin vaihtamisen jälkeen IP-osoite on päivitettävä. IP:n päivitystapa on kuvattu aiemmin.

1: Koska jokaisen levyn DDR ei välttämättä ole täsmälleen sama, MIG IP on määritettävä oman kaaviosi mukaan. Voit jopa poistaa alkuperäisen projektini MIG:n ja lisätä IP-osoitteen uudelleen ja määrittää sen uudelleen.

2: Muokkaa pin rajoituksia oman kaavion mukaan ja muokkaa sitä xdc-tiedostossa;

3: Jos haluat siirtää puhtaan FPGA:n Zynqiin, sinun on lisättävä zynq soft core projektiin;

Laitteet, jotka on valmisteltava, ovat seuraavat:

FPGA-kehitys aluksella;

SDI-kamera tai HDMI SDI-laatikkoon;

SDI-HDMI-laatikko;

HDMI-näyttö;

Kehitystauluni on kytketty seuraavasti:

Kun otetaan esimerkkinä projektin lähdekoodi 1, tulos on seuraava:

Zynq-SDI-Video Fusion Overlay

Bonus: Suunnittelukoodin hankinta

Koodi on liian suuri eikä sitä voi lähettää sähköpostitse. Se lähetetään tietyn verkkolevylinkin kautta.

Tietojen hankkiminen: yksityisesti tai V-käyntikortti artikkelin lopussa.

Verkkolevyn tiedot ovat seuraavat:

Lisäksi monet ystävät ovat antaneet tälle bloggaajalle paljon mielipiteitä ja ehdotuksia, jotka haluavat rikastuttaa palvelun sisältöä ja vaihtoehtoja Koska eri ystävillä on erilaiset tarpeet, tämä bloggaaja tarjoaa myös seuraavat palvelut: