내 연락처 정보

우편메소피아@프로톤메일.com

2024-07-12

한어Русский языкEnglishFrançaisIndonesianSanskrit日本語DeutschPortuguêsΕλληνικάespañolItalianoSuomalainenLatina

현재 FPGA에서 SDI 비디오 인코딩 및 디코딩을 구현하는 솔루션은 두 가지가 있습니다. 하나는 일반적인 수신기 GS2971과 같은 전용 인코딩 및 디코딩 칩을 사용하는 것이고, 장점은 GS2971 수신기를 직접 사용하는 것입니다. SDI를 병렬 YCrCb422로 디코딩하고 GS2972는 병렬 YCrCb422를 SDI 비디오로 직접 인코딩합니다. 단점은 비용이 상대적으로 높다는 것입니다. Baidu에서 GS2971 및 GS2972의 가격을 검색할 수 있습니다. FPGA 로직 리소스 부서는 SDI 인코딩 및 디코딩을 구현하고 Xilinx 시리즈 FPGA의 GTP/GTX 리소스를 사용합니다. 역직렬화를 달성하려면 Xilinx 시리즈 FPGA의 SMPTE SDI 리소스를 사용하여 SDI 인코딩 및 디코딩을 구현한다는 장점이 있습니다. 리소스는 합리적으로 활용되며 GTP/GTX 리소스는 헛되이 사용되지 않습니다. 단점은 작업이 더 어렵고 FPGA 개발자의 더 높은 기술 수준이 필요하다는 것입니다. 흥미롭게도 이 두 솔루션에는 하드웨어 FPGA 개발 보드, 엔지니어링 소스 코드 등을 포함하여 이 블로그에 해당 솔루션이 있습니다.

이 디자인은 Zynq 시리즈의 Zynq7100 FPGA 개발 보드를 기반으로 하여 SDI 비디오 인코딩 및 디코딩 + 이미지 스케일링 + 다중 채널 비디오 접합을 구현합니다. 두 개의 입력 소스가 있으며 하나는 1920x1080@ 해상도의 3G-SDI 카메라입니다. 60Hz 및 HD-SDI도 사용할 수 있습니다. 또는 SD-SDI 카메라는 이 디자인이 3개의 SDI 비디오에 적응하기 때문에 또 다른 HDMI-3G-SDI 상자는 2개의 입력을 시뮬레이션하기 위해 노트북에 연결됩니다. SDI 비디오는 동축 케이블 BNC 소켓을 통해 FPGA 개발 보드에 연결되고 동축 비디오는 온보드 Gv8601a 칩을 통과하여 차동 및 균형 EQ로의 단일 종단 변환 기능을 실현한 다음 차동 SDI 비디오 신호가 GTX로 들어갑니다. Bo는 이를 역직렬화라고 부르며, 그런 다음 Xilinx 시리즈 FPGA의 고유한 SMPTE SD/HD/3G SDI IP 코어로 전송되어 SDI를 수행합니다. 비디오 디코딩 작업 및 출력 BT1120 비디오 이 시점에서 SDI 비디오 디코딩 작업이 완료되었으며 일상적인 이미지 처리 작업을 수행할 수 있습니다.

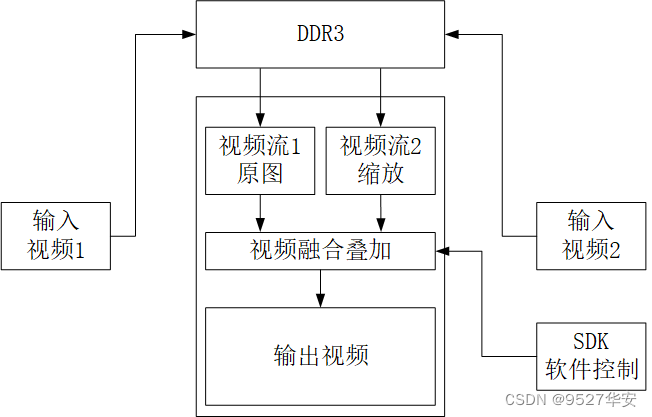

이 디자인의 목적은 이미지 스케일링 + 다중 채널 비디오 융합 및 중첩 후 디코딩된 SDI 비디오를 출력하는 것입니다. 현재 시장의 주류 프로젝트 요구에 부응하여 이 블로그에서는 두 가지 출력 방법, 즉 HDMI 출력을 설계했습니다. 3G -SDI 출력입니다. 두 가지 방법 모두 RGB로 변환하기 위해 BT1120 비디오를 디코딩하고 이미지 캐싱 작업을 수행해야 합니다. 이 디자인은 BT1120을 RGB로 변환하는 모듈을 사용하여 양방향 Xilinx 공식 VDMA 이미지 캐시 아키텍처를 구현합니다. 이미지 캐싱 및 캐싱 매체는 온보드 PS 측 DDR3입니다. 첫 번째 SDI 비디오는 VDMA를 통해 DDR에 기록된 다음 판독되어 비디오 융합 오버레이 모듈로 전송됩니다. 두 번째 SDI 비디오는 DDR을 통해 기록된 후 판독되지 않습니다. VDMA이지만 비디오 융합을 통해 오버레이됩니다. 이 시점에서 2채널 비디오는 융합 및 오버레이 처리를 위해 비디오 융합 및 오버레이 모듈로 들어간 다음 HDMI 디스플레이를 출력합니다. , 이는 HDMI 출력 방식이거나 RGB에서 BT1120 모듈로의 변환을 통해 비디오 형식이 실현된 다음 비디오가 SMPTE SD/HD/3G SDI IP 코어에 들어가고 SDI 비디오 인코딩 작업을 수행하고 SDI 비디오를 출력한 다음 통과합니다. FPGA 내부의 GTX 고속 리소스를 통해 병렬 데이터를 이 블로그에서 직렬이라고 부르는 고속 직렬로 변환하고, 차동 고속 신호가 온보드 Gv8500 칩에 들어가 단일 데이터로 차동 변환 기능을 실현합니다. -종료 및 드라이버 향상 SDI 비디오는 FPGA 개발 보드의 BNC 소켓을 통해 출력되며 동축 케이블을 통해 HDMI 디스플레이에 연결됩니다. 다음과 같은 프로젝트 소스 코드 세트:

독자의 이해를 돕기 위해 위의 두 가지 프로젝트 소스 코드 세트를 다음과 같이 설명합니다.

프로젝트 소스 코드 1

개발 보드의 FPGA 모델은 Xilinx–>Xilinx-Zynq7100–xc7z100ffg900-2입니다. 두 개의 입력 소스가 있습니다. 하나는 1920x1080@60Hz 해상도의 3G-SDI 카메라이고 다른 하나는 HDMI-3G-SDI입니다. 상자는 1920x1080@60Hz 해상도의 아날로그 SDI 카메라에 연결되어 있으며 2개의 온보드 Gv8601a 칩을 통해 FPGA로 전송되어 차동 및 균형 EQ로 변환됩니다. 두 개의 GTX 채널을 통해 SDI 비디오가 병렬 데이터로 역직렬화됩니다. 그런 다음 SMPTE SDI IP 코어의 2개 채널을 통해 SDI가 BT1120 데이터의 2개 채널로 디코딩된 다음 BT1120의 2개 채널을 통해 RGB 모듈로 변환됩니다. RGB888 비디오로 전환한 다음 Xilinx 공식 비디오 입력 AXI4-Stream IP 코어의 2개 채널을 통해 RGB888 데이터를 AXI4-Stream 데이터 스트림으로 변환한 다음 2채널 Xilinx 공식 VDMA를 통해 PS 측 DDR3 캐시에 비디오를 기록합니다. 이미지 캐시 솔루션은 HLS를 기반으로 자체 개발한 다중 채널 비디오 융합 및 오버레이 IP 코어가 2채널 비디오 융합 및 오버레이 작업을 구현한 다음 Xilinx 공식 AXI4-Stream To Video Out IP 코어를 입력하여 AXI4-를 변환합니다. 비디오 스트림을 기본 비디오 스트림으로 스트리밍한 다음 퓨전 오버레이 비디오를 RGB-HDMI 모듈로 보내 RGB888 비디오를 HDMI 비디오로 변환하고 출력 해상도는 1920x1080@60Hz입니다. 자세한 디스플레이 효과는 다음에서 출력 데모 비디오를 참조하십시오. 기사가 끝나면 이미지가 HDMI 디스플레이를 통해 표시됩니다. 이 프로젝트에서는 SDI 비디오를 HDMI 시나리오에 연결하는 데 적합한 Zynq 소프트 코어를 실행해야 합니다.

프로젝트 소스 코드 2

개발 보드의 FPGA 모델은 Xilinx–>Xilinx-Zynq7100–xc7z100ffg900-2입니다. 두 개의 입력 소스가 있습니다. 하나는 1920x1080@60Hz 해상도의 3G-SDI 카메라이고 다른 하나는 HDMI-3G-SDI입니다. 상자는 1920x1080@60Hz 해상도의 아날로그 SDI 카메라에 연결되어 있으며 2개의 온보드 Gv8601a 칩을 통해 FPGA로 전송되어 차동 및 균형 EQ로 변환됩니다. 두 개의 GTX 채널을 통해 SDI 비디오가 병렬 데이터로 역직렬화됩니다. 그런 다음 SMPTE SDI IP 코어의 2개 채널을 통해 SDI가 BT1120 데이터의 2개 채널로 디코딩된 다음 BT1120의 2개 채널을 통해 RGB 모듈로 변환됩니다. RGB888 비디오로 전환한 다음 Xilinx 공식 비디오 입력 AXI4-Stream IP 코어의 2개 채널을 통해 RGB888 데이터를 AXI4-Stream 데이터 스트림으로 변환한 다음 2채널 Xilinx 공식 VDMA를 통해 PS 측 DDR3 캐시에 비디오를 기록합니다. 이미지 캐시 솔루션은 HLS를 기반으로 자체 개발한 다중 채널 비디오 융합 및 오버레이 IP 코어가 2채널 비디오 융합 및 오버레이 작업을 구현한 다음 Xilinx 공식 AXI4-Stream To Video Out IP 코어를 입력하여 AXI4-를 변환합니다. 비디오 스트림을 기본 비디오 스트림으로 스트리밍한 다음 퓨전 오버레이 비디오를 RGB-BT1120 모듈로 전송하여 RGB888 비디오를 BT1120 비디오로 변환한 다음 SMPTE SD/HD/3G SDI IP 코어를 BT1120 비디오로 인코딩합니다. 그런 다음 FPGA 내부의 GTX 고속 리소스를 통해 SDI 병렬 데이터를 고속 직렬 신호로 변환한 다음 온보드 Gv8500 칩을 사용하여 단일 종단 및 드라이버로의 차동 변환을 구현합니다. 향상 후 출력 해상도는 1920x1080@60Hz입니다. 마지막으로 SDI-HDMI 박스는 디스플레이용 HDMI 디스플레이에 연결하는 데 사용됩니다. 이 프로젝트에서는 SDI-SDI 시나리오에 적합한 Zynq 소프트 코어를 실행해야 합니다.

이 프로젝트와 소스 코드에는 제가 작성한 부분과 인터넷의 공개 채널(CSDN, Xilinx 공식 웹사이트, Altera 공식 웹사이트 등)에서 얻은 부분이 모두 포함되어 있습니다. 불쾌하다고 생각되면 개인 메시지를 보내주십시오. 이를 바탕으로 본 프로젝트와 해당 소스 코드는 독자나 팬의 개인적인 연구 및 연구에만 사용되며, 독자나 팬 본인의 상업적 이용으로 인해 법적 문제가 발생할 경우, 상업적인 목적으로 사용하는 것을 금지합니다. , 본 블로그와 해당 블로거는 아무런 관련이 없으므로 주의해서 이용해주시기 바랍니다. . .

내 블로그 홈페이지에는 FPGA 코덱 SDI 엔지니어링 소스 코드와 블로그 소개가 가득한 SDI 비디오 칼럼이 있습니다. GS2971/GS2972 기반의 SDI 코덱과 HD-SDI, 3G- 기반의 SDI 코덱이 있습니다. SDI, 6G-SDI, 12G-SDI 등의 열 주소 링크는 다음과 같습니다.

클릭하시면 바로가기됩니다

이 블로그는 다중 채널 비디오 융합 오버레이 애플리케이션을 자체 개발했습니다. 이전에 블로그 주소 링크를 직접 작성한 적이 있습니다.

클릭하시면 바로가기됩니다

설계 원리 블록 다이어그램은 다음과 같습니다.

알아채다! ! ! !

알아채다! ! ! !

보라색 화살표: 3G-SDI 출력 경로

빨간색 화살표: HDMI 출력 경로

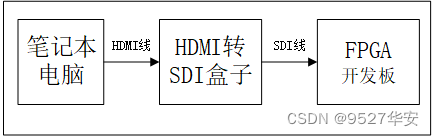

FPGA 개발 보드의 양방향 SDI 비디오 입력 인터페이스에 연결되는 2개의 SDI 입력 장치가 있으며, 그 중 하나는 1920x1080@60Hz 해상도의 3G-SDI 카메라입니다. 이 디자인 때문에 사용할 수 있습니다. 세 가지 유형의 SDI 비디오에 적합합니다. 또 다른 HDMI-3G-SDI 상자는 SDI 카메라를 시뮬레이션하기 위해 노트북에 연결되며 예산이 제한된 친구는 사용할 수 있습니다. SDI 카메라를 시뮬레이션하기 위해 HDMI-SDI 상자를 사용하는 것을 고려하십시오. HDMI-SDI 상자를 사용할 때 Hezibao의 비용은 노트북이 될 수 있습니다. 즉, 노트북을 사용하여 HDMI 입력 인터페이스에 연결할 수 있습니다. HDMI 케이블을 통해 HDMI-SDI 상자를 사용하고 SDI 케이블을 사용하여 HDMI를 SDI 상자에 연결합니다. FPGA 개발 보드에 대한 SDI 출력 인터페이스는 다음과 같습니다.

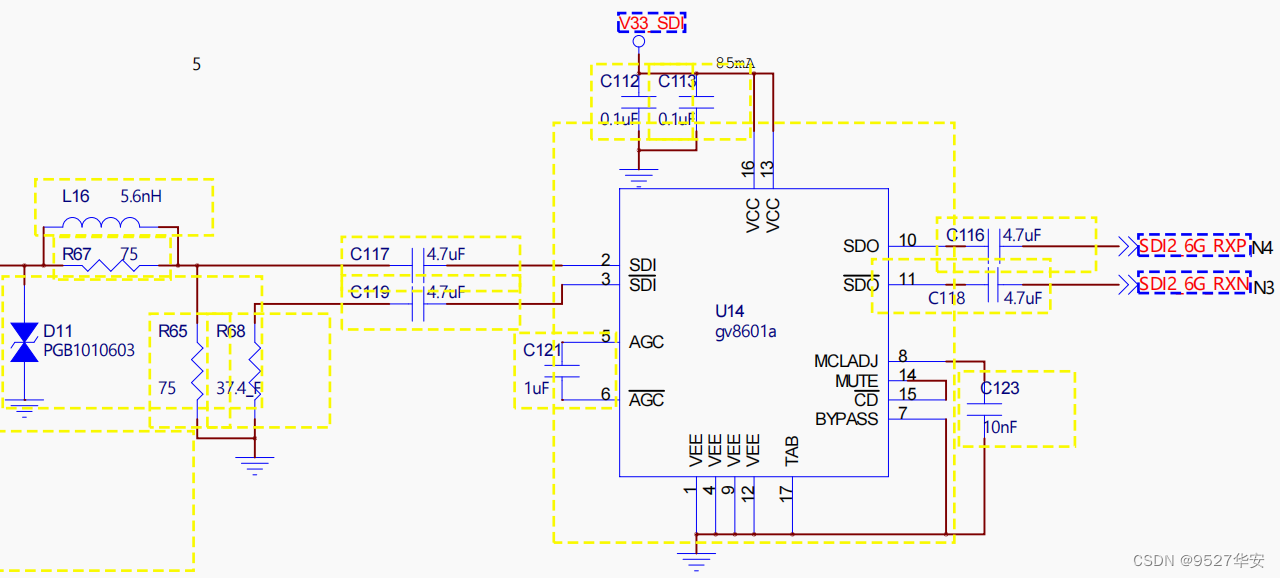

Gv8601a 칩은 차동 및 균형 EQ로의 단일 종단 변환 기능을 실현합니다. 물론 Gv8601a는 공식 Xilinx 솔루션을 사용하기 때문에 선택되었습니다. Gv8601a 이퀄라이저의 개략도는 다음과 같습니다.

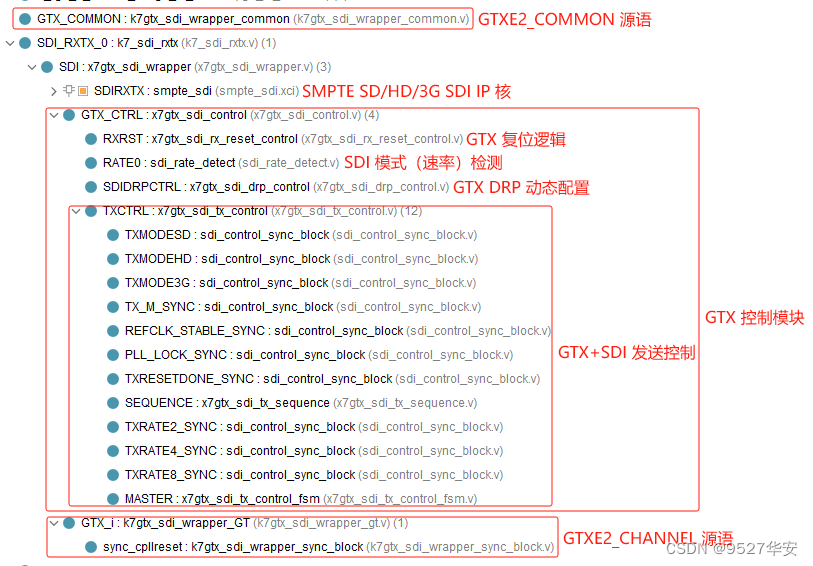

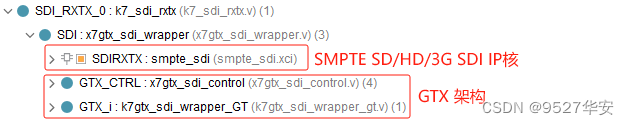

이 설계는 Xilinx의 고유한 GTX 고속 신호 처리 리소스를 사용하여 SDI 차동 비디오 신호의 역직렬화 및 직렬화를 달성합니다. SDI 비디오 수신의 경우 GTX는 역직렬화 역할, 즉 입력 고속 직렬 차동 신호를 병렬 디지털로 디코딩합니다. SDI 비디오 전송의 경우 GTX는 직렬화 역할을 합니다. 즉, 입력 병렬 디지털 신호를 고속 직렬 차동 신호로 직렬화하려면 일반적으로 vivado를 통해 GTX IP 코어를 인스턴스화해야 합니다. 하지만 이 설계에는 SD-SDI, HD-SDI, 3G-SDI 비디오의 자동 인식과 적응형 처리가 필요하므로 GTX에는 라인 레이트를 동적으로 변경하는 기능이 필요합니다. 이 기능은 DRP 인터페이스를 통해 구성할 수 있습니다. GTX의 속도 인터페이스를 통해서도 구성할 수 있으므로 구성을 위해 vivado의 UI 인터페이스를 사용할 수 없습니다. 대신 GTX의 GTXE2_CHANNEL 및 GTXE2_COMMON 소스 언어를 직접 인스턴스화하고 GTX 리소스를 직접 사용할 수 있습니다. GTX 라인 속도를 동적으로 구성하려면 GTX 제어 모듈도 필요합니다. 이 모듈은 Xilinx의 공식 설계 계획을 참조하며 SDI 모드의 동적 모니터링, DRP의 동적 구성 등의 기능을 갖추고 있습니다. plan은 Xilinx의 공식 설계를 나타내며 GTX 역직렬화 및 직렬화 모듈의 코드 구조는 다음과 같습니다.

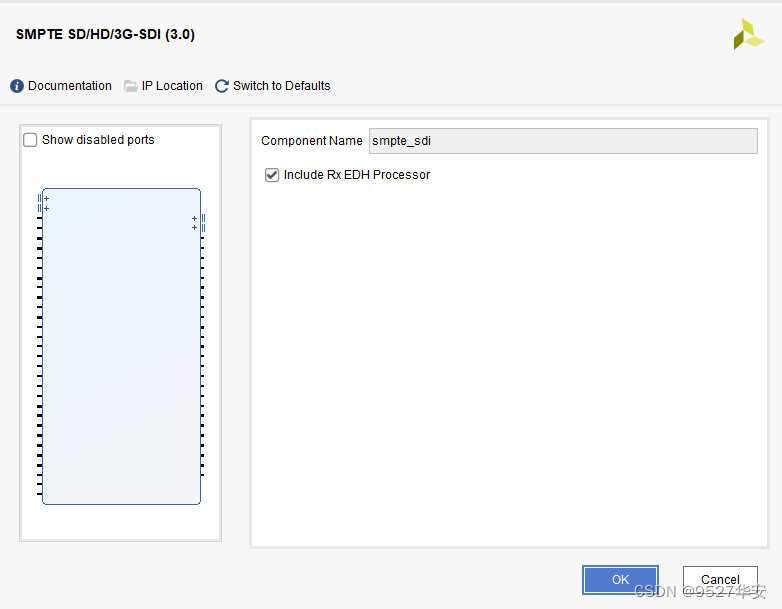

SMPTE SD/HD/3G SDI IP 코어는 Xilinx 시리즈 FPGA의 SDI 비디오 인코딩 및 디코딩을 위한 고유한 IP입니다. IP 구성은 사용이 매우 간단합니다.

SMPTE SD/HD/3G SDI IP 코어는 GTX와 함께 사용해야 합니다. SDI 비디오 수신의 경우 IP는 GTX에서 데이터를 수신한 다음 SDI 비디오를 BT1120 비디오 출력으로 디코딩합니다. SDI 비디오 전송의 경우 IP는 BT1120을 수신합니다. 사용자 측의 비디오 데이터를 인코딩한 다음 BT1120 비디오를 SDI 비디오 출력으로 인코딩합니다. 이 솔루션은 공식 Xilinx 설계를 참조하며 다음과 같습니다.

BT1120-RGB 모듈의 기능은 SMPTE SD/HD/3G SDI IP 코어 디코딩으로 출력된 BT1120 비디오를 RGB888 비디오로 변환하는 것입니다. BT1120-CEA861 모듈, YUV422-YUV444 모듈, YUV444-RGB888의 세 가지 모듈로 구성됩니다. 이 솔루션은 공식 Xilinx 디자인이 채택된 BT1120-RGB 모듈의 코드 구조를 나타냅니다.

이 디자인의 비디오 캐시 솔루션은 2채널 Xilinx 공식 VDMA 이미지 캐시 아키텍처를 채택합니다. 캐시 매체는 PS 측 DDR3입니다. 첫 번째 SDI 비디오는 VDMA를 통해 DDR에 기록된 후 비디오 퓨전 오버레이 모듈로 전송됩니다. 두 번째 SDI 비디오는 VDMA를 통해 DDR에 쓴 후 판독되지 않고 비디오 융합 오버레이 모듈을 통해 DDR3에서 판독됩니다. 프로젝트 소스 코드 1을 예로 들면 VDMA는 Xilinx의 블록 디자인을 사용하여 설계되었습니다. 아래와 같이 vivado:

지연 시간을 줄이기 위해 VDMA는 다음과 같이 1프레임을 캐시하도록 설정됩니다.

다중 채널 비디오 융합 오버레이 디자인 블록 다이어그램은 다음과 같습니다.

다중 채널 비디오 융합 및 오버레이는 기본 비디오와 오버레이 비디오의 융합 및 중첩에 의해 형성됩니다. 기본 비디오는 첫 번째 채널의 입력 비디오이고 오버레이 비디오는 두 번째 채널의 스케일링된 비디오입니다. SDK 소프트웨어는 2채널 비디오 융합의 투명도, 오버레이 비디오의 확대/축소 크기, 오버레이 비디오의 표시 위치 및 기타 정보를 동적으로 구성합니다. HLS 솔루션 C++ 코드는 RTL로 합성되어 IP로 캡슐화되어 vivado Call the IP에서 사용할 수 있습니다. 이 솔루션에 대한 자세한 내용은 다음 블로그 링크를 참조하세요.

클릭하시면 바로가기됩니다

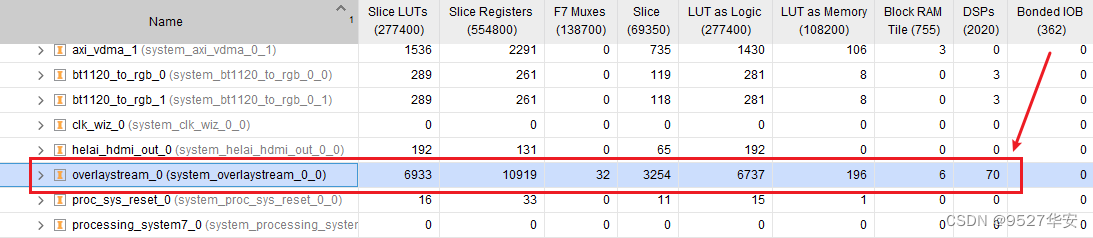

vivado에서 이 IP의 포괄적인 리소스 사용량은 다음과 같습니다.

HLS 다중 채널 비디오 융합 오버레이가 제대로 작동하려면 SDK에서 드라이버와 사용자 프로그램을 실행해야 합니다. 프로젝트에 C 언어 프로그램을 제공했습니다. 자세한 내용은 HLS 다중 채널의 스크린샷을 참조하세요. 채널 비디오 퓨전 오버레이 호출은 다음과 같습니다.

HDMI 비디오 출력 아키텍처는 다음과 같습니다.

Xilinx 공식 설계를 참조하면 VTC+AXI4-Stream To Video Out 아키텍처를 사용하여 출력 비디오를 AXI4-Stream에서 기본 형식으로 변환한 다음 순수 Verilog 코드로 구현된 RGB888-HDMI 모듈을 사용하여 RGB888을 HDMI로 변환하고 최종적으로 표시합니다. 모니터를 통해 RGB888-HDMI 모듈 코드 구조는 다음과 같습니다.

RGB888-HDMI 모듈에 대해서는 이전 블로그인 블로그 주소를 참조하십시오.클릭하시면 바로가기됩니다

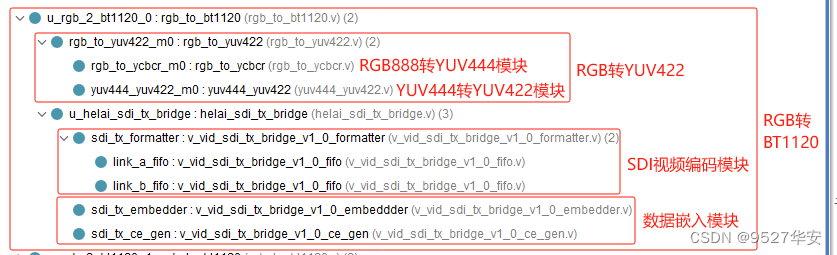

SDI 비디오 출력 아키텍처는 먼저 VDMA에서 읽은 AXI4-Stream을 RGB888 비디오를 얻은 후 RGB를 BT1120 비디오로 변환해야 합니다. 아키텍처는 다음과 같습니다.

SDI 출력 모드에서 VGA 타이밍 모듈의 픽셀 클록은 SMPTE SD/HD/3G SDI IP 코어의 송신 사용자 클록에 의해 제공됩니다. 예를 들어 3G-SDI 모드에서는 픽셀 클록이 다릅니다. , 픽셀 클럭은 148.5M입니다. HD-SDI 720P@60Hz 모드에서 픽셀 클럭은 74.25M입니다.

SDI 출력 모드에서는 RGB to BT1120 모듈을 사용해야 합니다. RGB to BT1200 모듈의 기능은 사용자 측의 RGB 비디오를 BT1200 비디오로 변환하여 SMPTE SD/HD/3G SDI IP로 출력하는 것입니다. 코어, RGB - BT1120 모듈은 RGB888 - YUV444 모듈, YUV444 - YUV422 모듈, SDI 비디오 인코딩 모듈 및 데이터 임베딩 모듈로 구성됩니다. 이 솔루션은 BT1120 - RGB 모듈의 코드 구조를 나타냅니다. 다음과 같이:

이 두 부분은 수신 프로세스와 해당 모듈을 공유합니다. 이는 기능적으로 수신 프로세스의 역 프로세스이므로 다시 설명하지 않습니다.

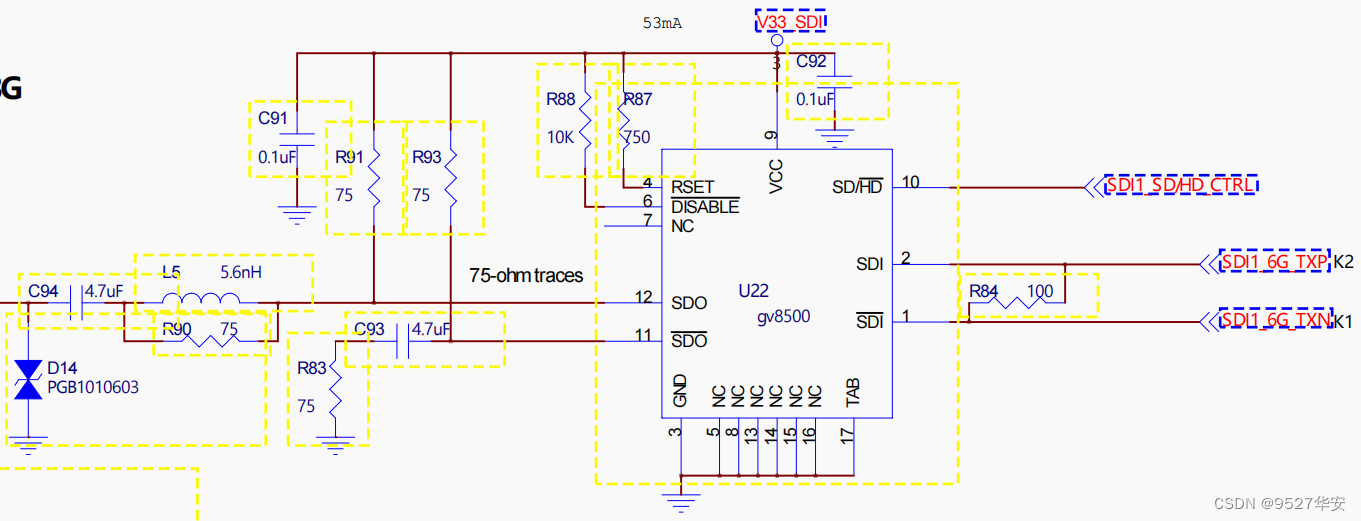

Gv8500 칩은 단일 종단 및 향상된 드라이버로의 차동 변환 기능을 실현합니다. 물론, 다른 유형의 장치도 사용할 수 있기 때문에 Gv8500이 선택되었습니다. Gv8500 드라이버의 개략도는 다음과 같습니다.

SDI 출력 모드에서는 SDI-HDMI 박스를 사용해야 합니다. 왜냐하면 제 손에 있는 모니터에는 SDI 인터페이스가 없고 HDMI 인터페이스만 있기 때문입니다. SDI 비디오를 표시하려면 이는 물론 가능합니다. 귀하의 모니터에는 SDI 인터페이스가 있으므로 직접 연결할 수 있습니다. 연결에 따르면 내 SDI-HDMI 상자가 특정 매장에서 100위안 미만에 구입한 것으로 표시됩니다.

이 블로그에서는 프로젝트 소스 코드 1을 예로 들면, vivado 블록 디자인 디자인은 다음과 같습니다. 블록 디자인 디자인은 이미지 캐시 아키텍처의 일부입니다.

프로젝트 소스 코드 1을 예로 들면, 프로젝트 소스 코드 구조는 다음과 같습니다.

프로젝트 소스 코드의 PL 사이드 클럭은 Zynq 소프트 코어에서 제공되므로 Zynq를 시작하려면 SDK를 실행해야 합니다. 또한 비디오 퓨전 오버레이 및 VDMA와 같은 IP 코어가 제대로 작동하려면 소프트웨어 드라이버를 실행해야 합니다. SDK 소프트웨어 코드 구조는 다음과 같습니다:

SDK 코드의 구성은 다음과 같습니다. 사용자는 자신의 필요에 따라 임의로 수정할 수 있습니다.

첫 번째 비디오는 1920x1080 해상도의 하위 레이어 비디오입니다.

두 번째 채널 비디오는 1920x1080 해상도의 오버레이 비디오입니다. 오버레이 비디오 좌표(400, 200)에서 1000x800 영역을 오버레이 융합 비디오로 가져옵니다.

이전 단계에서 얻은 600x600 오버레이 퓨전 비디오를 960x540으로 확장합니다.

이전 단계에서 기본 비디오의 (0,0) 좌표부터 시작하여 960x540 중첩 퓨전 비디오를 오버레이하고 기본 및 오버레이 레이어의 투명도를 80으로 설정합니다.

개발 보드 FPGA 모델: Xilinx-Zynq7100–xc7z100ffg900-2;

개발 환경: Vivado2019.1;

입력: 3G-SDI 카메라 또는 HDMI - SDI 박스, 해상도 1920x1080@60Hz;

출력: HDMI, 해상도 1920x1080@60Hz;

캐싱 솔루션: Xilinx 공식 VDMA 솔루션;

캐시 미디어: PS 측 DDR3;

비디오 융합 및 오버레이 솔루션: HLS를 기반으로 자체 개발한 다중 채널 비디오 융합 및 오버레이;

프로젝트 역할: 이 프로젝트의 목적은 독자가 Zynq 시리즈 FPGA의 설계 기능을 숙지하여 SDI를 HDMI로 구현하여 자신의 프로젝트를 이식하고 설계할 수 있도록 하는 것입니다.

프로젝트 블록 디자인 및 프로젝트 코드 아키텍처에 대해서는 3장의 "프로젝트 소스 코드 아키텍처" 섹션을 참조하십시오.

프로젝트의 자원 소비 및 전력 소비는 다음과 같습니다.

개발 보드 FPGA 모델: Xilinx-Zynq7100–xc7z100ffg900-2;

개발 환경: Vivado2019.1;

입력: 3G-SDI 카메라 또는 HDMI - SDI 박스, 해상도 1920x1080@60Hz;

출력: 3G-SDI, 해상도 1920x1080@60Hz;

캐싱 솔루션: Xilinx 공식 VDMA 솔루션;

캐시 미디어: PS 측 DDR3;

비디오 융합 및 오버레이 솔루션: HLS를 기반으로 자체 개발한 다중 채널 비디오 융합 및 오버레이;

프로젝트 역할: 이 프로젝트의 목적은 독자가 Zynq 시리즈 FPGA의 설계 기능을 숙지하여 SDI를 HDMI로 구현하여 자신의 프로젝트를 이식하고 설계할 수 있도록 하는 것입니다.

프로젝트 블록 디자인 및 프로젝트 코드 아키텍처에 대해서는 3장의 "프로젝트 소스 코드 아키텍처" 섹션을 참조하십시오.

프로젝트의 자원 소비 및 전력 소비는 다음과 같습니다.

1: 귀하의 vivado 버전이 이 프로젝트의 vivado 버전과 일치하는 경우 프로젝트를 직접 엽니다.

2: vivado 버전이 이 프로젝트의 vivado 버전보다 낮은 경우 프로젝트를 열고 파일 –> 다른 이름으로 저장을 클릭해야 합니다. 그러나 이 방법은 vivado 버전을 vivado로 업그레이드하는 것입니다. 이 프로젝트 버전 이상

3: 귀하의 vivado 버전이 이 프로젝트의 vivado 버전보다 높은 경우 해결 방법은 다음과 같습니다.

프로젝트를 열면 다음과 같이 IP가 잠겨 있는 것을 확인할 수 있습니다.

이때 IP를 업그레이드해야 합니다. 단계는 다음과 같습니다.

귀하의 FPGA 모델이 내 것과 일치하지 않는 경우 다음과 같이 FPGA 모델을 변경해야 합니다.

FPGA 모델을 변경한 후에는 IP를 업그레이드해야 합니다. IP를 업그레이드하는 방법은 앞에서 설명했습니다.

1: 각 보드의 DDR이 반드시 동일할 필요는 없으므로 MIG IP는 자신의 회로도에 따라 구성해야 합니다. 원래 프로젝트의 MIG를 직접 삭제하고 IP를 다시 추가하고 재구성할 수도 있습니다.

2: 자신의 회로도에 따라 핀 제약 조건을 수정하고 xdc 파일에서 수정합니다.

3: 순수 FPGA를 Zynq에 이식하려면 프로젝트에 zynq 소프트 코어를 추가해야 합니다.

준비해야 할 장비는 다음과 같습니다.

FPGA 개발 보드;

SDI 카메라 또는 HDMI-SDI 상자;

SDI-HDMI 박스;

HDMI 디스플레이;

내 개발 보드는 다음과 같이 연결됩니다.

프로젝트 소스 코드 1을 예로 들면 출력은 다음과 같습니다.

Zynq-SDI-비디오 퓨전 오버레이

보너스: 엔지니어링 코드 획득

코드가 너무 커서 이메일로 보낼 수 없습니다. 특정 네트워크 디스크 링크를 통해 전송됩니다.

정보 획득 방법 : 비공개 또는 기사 마지막에 V 명함.

네트워크 디스크 정보는 다음과 같습니다.

또한 많은 친구들이 이 블로거에게 많은 의견과 제안을 제공하여 서비스 콘텐츠와 옵션을 풍부하게 하기를 희망합니다. 친구들마다 요구 사항이 다르기 때문에 이 블로거는 다음 서비스도 제공합니다.