私の連絡先情報

郵便メール:

2024-07-12

한어Русский языкEnglishFrançaisIndonesianSanskrit日本語DeutschPortuguêsΕλληνικάespañolItalianoSuomalainenLatina

現在、FPGA で SDI ビデオのエンコードとデコードを実装するには 2 つのソリューションがあります。1 つは、一般的なレシーバー GS2971 などの専用のエンコードおよびデコード チップを使用する方法で、利点はたとえば GS2971 レシーバーを直接使用することです。 SDI をパラレル YCrCb422 にデコードし、GS2972 はパラレル YCrCb422 を SDI ビデオに直接エンコードします。欠点は、コストが比較的高いことです。別の解決策は、Baidu で GS2971 と GS2972 の価格を検索することです。 FPGA ロジック リソース部門では、SDI エンコーディングとデコーディングを実装し、ザイリンクス シリーズ FPGA の GTP/GTX リソースを使用して、デシリアライゼーションを実現するには、ザイリンクス シリーズ FPGA の SMPTE SDI リソースを使用して SDI エンコーディングとデコーディングを実装します。リソースが合理的に利用され、GTP/GTX リソースが無駄に使用されなくなります。欠点は、操作がより難しくなり、FPGA 開発者の高い技術レベルが必要になることです。興味深いことに、これら 2 つのソリューションには、ハードウェア FPGA 開発ボード、エンジニアリング ソース コードなどを含む、このブログの対応するソリューションがあります。

このデザインは、Zynq シリーズの Zynq7100 FPGA 開発ボードに基づいており、SDI ビデオ エンコードおよびデコード、イメージ スケーリング、マルチ チャネル ビデオ スプライシングを実装しています。入力ソースは 2 つあり、1 つは解像度 1920x1080@ の 3G-SDI カメラです。 60Hz、HD-SDI または SD-SDI カメラも使用可能。この設計は 3 つの SDI ビデオに対応しており、別の HDMI to 3G-SDI ボックスをラップトップに接続して 2 つの SDI カメラをシミュレートします。 SDI ビデオは、同軸ケーブル BNC ソケットを介して FPGA 開発ボードに接続され、同軸ビデオはオンボード Gv8601a チップを通過して、差動およびバランス EQ へのシングルエンド変換機能を実現し、差動 SDI ビデオ信号が GTX に入力されます。 Bo 氏は、FPGA 内の高速リソースを使用してデータの高速シリアル/パラレル変換を実現し、デシリアル化されたパラレル ビデオをザイリンクス シリーズ FPGA の独自の SMPTE SD/HD/3G SDI IP コアに送信して SDI を実行します。ビデオのデコード操作と BT1120 ビデオの出力 この時点で、SDI ビデオのデコード操作が完了し、通常の画像処理操作を実行できるようになります。

この設計の目的は、画像のスケーリング + マルチチャンネル ビデオの融合と重ね合わせ後にデコードされた SDI ビデオを出力することです。市場での現在の主流のプロジェクトのニーズに応えて、このブログでは 2 つの出力方法 (1 つは HDMI 出力) を設計しました。は 3G -SDI 出力であり、どちらの方法でも BT1120 ビデオを RGB に変換し、イメージ キャッシュ操作を行う必要があります。このデザインでは、BT1120 から RGB モジュールを使用してビデオ フォーマット変換を実現します。画像のキャッシュとキャッシュ メディアはオンボード PS 側 DDR3 です。最初の SDI ビデオは VDMA 経由で DDR に書き込まれ、その後読み出され、ビデオ フュージョン オーバーレイ モジュールに送信されます。2 番目の SDI ビデオは、DDR 経由で書き込まれた後は読み出されません。この時点で、2 チャネル ビデオはビデオ フュージョンおよびオーバーレイ モジュールに入り、HDMI ディスプレイに出力されます。 HDMI 出力方式、または RGB から BT1120 モジュールへの変換を通じてビデオ形式が実現され、ビデオは SMPTE SD/HD/3G SDI IP コアに入り、SDI ビデオ エンコード処理を実行して SDI ビデオを出力します。 FPGA 内の GTX 高速リソースを介して、パラレル データから高速シリアル (このブログではシリアルと呼ぶ) への変換を実現します。その後、差動高速信号はオンボード Gv8500 チップに入り、シングルへの差動変換機能を実現します。 SDI ビデオは、FPGA 開発ボードの BNC ソケットを介して出力され、同軸ケーブルを介して HDMI ディスプレイに接続されます。これは、このブログが提供する SDI 出力方法です。次のようなプロジェクト ソース コードのセット。

読者の理解を容易にするために、上記の 2 つのプロジェクト ソース コード セットを次のように説明します。

プロジェクトのソースコード 1

開発ボードの FPGA モデルは Xilinx->Xilinx-Zynq7100-xc7z100ffg900-2 で、入力ソースが 2 つあり、1 つは解像度 1920x1080@60Hz の 3G-SDI カメラ、もう 1 つは HDMI - 3G-SDI です。ボックスは、解像度 1920x1080@60Hz のアナログ SDI カメラに接続され、2 つのオンボード Gv8601a チップを介して FPGA に送信され、差動およびバランス EQ に変換されます。 2 つの GTX チャネルを通じて、SDI ビデオがパラレル データにデシリアル化され、次に 2 つの SMPTE SDI IP コアを通じて、SDI が 2 つの BT1120 データにデコードされ、次に 2 つの BT1120 チャネルを通じて RGB モジュールに変換されます。 RGB888 ビデオに変換し、2 チャネルのザイリンクス公式 Video In To AXI4-Stream IP コアを介して RGB888 データを AXI4-Stream データ ストリームに変換し、2 チャネルのザイリンクス公式 VDMA を介してビデオを PS 側の DDR3 キャッシュに書き込みます。イメージ キャッシュ ソリューション、HLS に基づく自社開発のマルチ チャネル ビデオ フュージョンおよびオーバーレイ IP コアが 2 チャネル ビデオ フュージョンおよびオーバーレイ動作を実装し、ザイリンクス公式 AXI4-Stream To Video Out IP コアを入力して AXI4-ビデオ ストリームをネイティブ ビデオ ストリームにストリーミングし、フュージョン オーバーレイ ビデオを RGB to HDMI モジュールに送信して、RGB888 ビデオを HDMI ビデオに変換し、出力解像度は 1920x1080@60Hz です。詳細な表示効果については、出力デモ ビデオを参照してください。記事の最後; 画像は最終的に HDMI ディスプレイを介して表示されます。このプロジェクトでは、SDI ビデオを HDMI に接続するシナリオに適した Zynq ソフト コアを実行する必要があります。

プロジェクトのソースコード 2

開発ボードの FPGA モデルは Xilinx->Xilinx-Zynq7100-xc7z100ffg900-2 で、入力ソースが 2 つあり、1 つは解像度 1920x1080@60Hz の 3G-SDI カメラ、もう 1 つは HDMI - 3G-SDI です。ボックスは、解像度 1920x1080@60Hz のアナログ SDI カメラに接続され、2 つのオンボード Gv8601a チップを介して FPGA に送信され、差動およびバランス EQ に変換されます。 2 つの GTX チャネルを通じて、SDI ビデオがパラレル データにデシリアル化され、次に 2 つの SMPTE SDI IP コアを通じて、SDI が 2 つの BT1120 データにデコードされ、次に 2 つの BT1120 チャネルを通じて RGB モジュールに変換されます。 RGB888 ビデオに変換し、2 チャネルのザイリンクス公式 Video In To AXI4-Stream IP コアを介して RGB888 データを AXI4-Stream データ ストリームに変換し、2 チャネルのザイリンクス公式 VDMA を介してビデオを PS 側の DDR3 キャッシュに書き込みます。イメージ キャッシュ ソリューション、HLS に基づく自社開発のマルチ チャネル ビデオ フュージョンおよびオーバーレイ IP コアが 2 チャネル ビデオ フュージョンおよびオーバーレイ動作を実装し、ザイリンクス公式 AXI4-Stream To Video Out IP コアを入力して AXI4-ビデオ ストリームをネイティブ ビデオ ストリームにストリーミングし、次にフュージョン オーバーレイ ビデオを RGB to BT1120 モジュールに送信して、RGB888 ビデオを BT1120 ビデオに変換し、SMPTE SD /HD/3G SDI IP コアを渡して BT1120 ビデオを SDI ビデオにエンコードします。次に、FPGA 内の GTX 高速リソースを介して SDI パラレル データを高速シリアル信号に変換し、オンボード Gv8500 チップを使用してシングルエンドおよびドライバーへの差動変換を実装します。強化後の出力解像度は 1920x1080@60Hz です。最後に、SDI to HDMI ボックスを使用して HDMI ディスプレイに接続し、このプロジェクトでは SDI to SDI シナリオに適した Zynq ソフト コアを実行する必要があります。

このプロジェクトとそのソース コードには、私が書いた部分と、インターネット上のパブリック チャネル (CSDN、ザイリンクス公式 Web サイト、アルテラ公式 Web サイトなどを含む) から入手した部分の両方が含まれています。不快だと思われる場合は、以下にプライベート メッセージを送信してください。本プロジェクトおよびそのソースコードは、読者またはファンによる個人的な研究および研究のみを目的としており、読者またはファン自身による商業利用によって法的問題が生じる場合には、商業目的で使用することは禁止されています。 、当ブログとブロガー様とは一切関係がございませんので、ご利用の際はご注意ください。 。 。

私のブログのホームページには SDI ビデオのコラムがあり、FPGA コーデックの SDI エンジニアリング ソース コードとブログの紹介が満載です。GS2971/GS2972 ベースの SDI コーデックと、HD-SDI、3G リソースの両方に基づいた SDI コーデックがあります。 SDI、6G-SDI、12G-SDI などの列アドレスのリンクは次のとおりです。

クリックして直接移動します

このブログは、以前にブログを書いたことがあるマルチチャンネル ビデオ フュージョン オーバーレイ アプリケーションを独自に開発しました。ブログのアドレスのリンクは次のとおりです。

クリックして直接移動します

設計原理のブロック図は次のとおりです。

知らせ! ! ! !

知らせ! ! ! !

紫の矢印: 3G-SDI 出力パス

赤い矢印: HDMI 出力パス

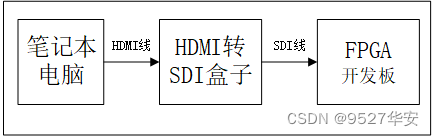

FPGA 開発ボードの 2 ウェイ SDI ビデオ入力インターフェイスに接続されている 2 つの SDI 入力デバイスがあり、1 つは解像度 1920x1080@60Hz の 3G-SDI カメラまたは SD-SDI カメラです。この設計により、3 種類の SDI ビデオに対応できます。もう 1 つの HDMI to 3G-SDI ボックスは、SDI カメラをシミュレートするためにラップトップに接続されます。 HDMI to SDI ボックスを使用して SDI カメラをシミュレートすることを検討してください。Hezibao の価格は約 100 元です。HDMI to SDI ボックスを使用する場合、入力ソースはラップトップにすることができます。つまり、ラップトップを使用して HDMI カメラの HDMI 入力インターフェイスに接続できます。 HDMI ケーブルを介して HDMI から SDI ボックスに接続し、SDI ケーブルを使用して HDMI から SDI ボックスに接続します。FPGA 開発ボードへの SDI 出力インターフェイスは次のとおりです。

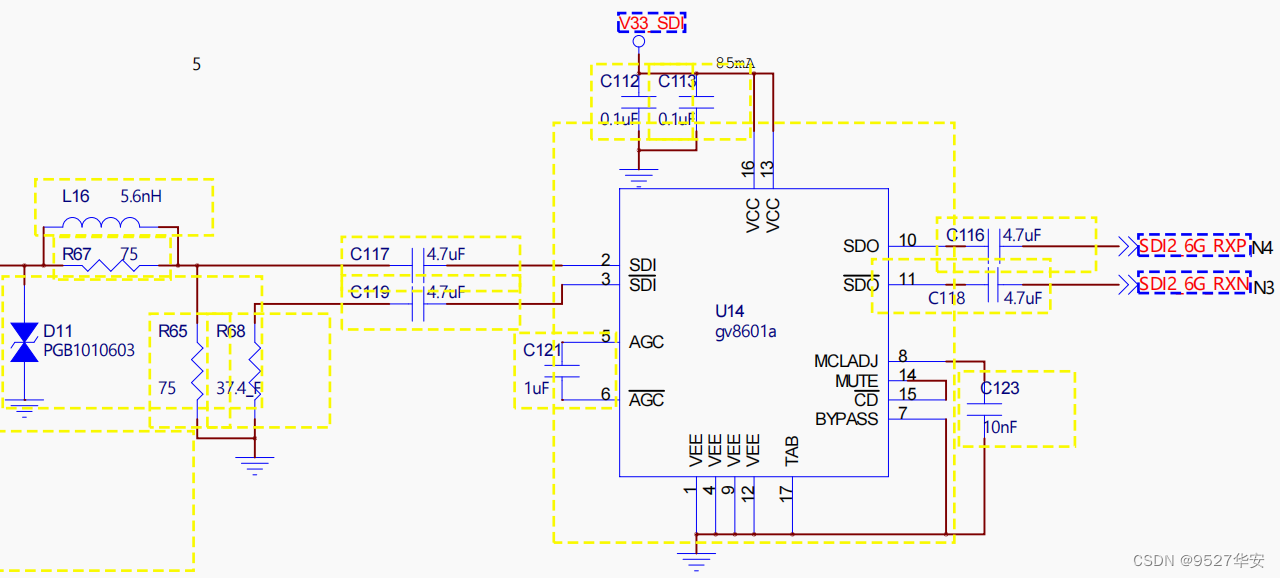

Gv8601a チップは、差動およびバランス EQ へのシングルエンド変換の機能を実現します。これは、公式のザイリンクス ソリューションを利用しているためです。もちろん、他のタイプのデバイスも使用できます。 Gv8601a イコライザーの回路図は次のとおりです。

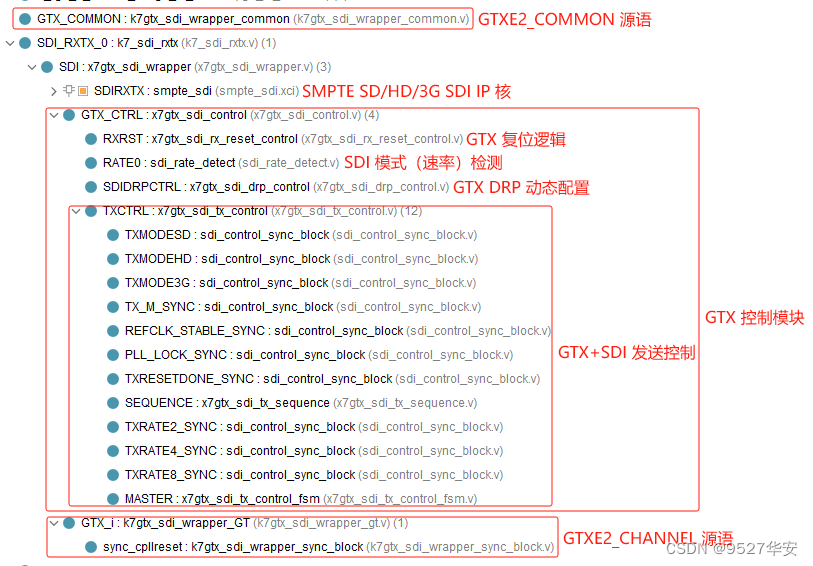

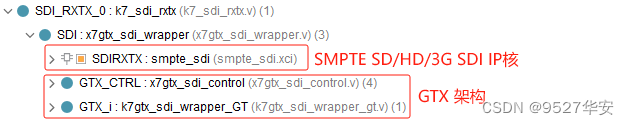

このデザインは、ザイリンクス独自の GTX 高速信号処理リソースを使用して、SDI 差動ビデオ信号のデシリアライズとシリアル化を実現します。SDI ビデオ受信の場合、GTX はデシリアライズの役割を果たします。つまり、入力された高速シリアル差動信号をパラレル デジタルにデコードします。 SDI ビデオ伝送の場合、GTX はシリアル化の役割を果たします。つまり、GTX を使用するには、通常、vivado による GTX IP コアのインスタンス化が必要です。ただし、この設計では SD-SDI、HD-SDI、および 3G-SDI ビデオの自動認識と適応処理が必要となるため、GTX にはライン レートを動的に変更する機能が必要です。この機能は DRP インターフェイスを通じて設定できます。 GTX のレート インターフェイスを通じて設定することもできるため、vivado の UI インターフェイスを使用して設定することはできません。代わりに、GTX の GTXE2_CHANNEL および GTXE2_COMMON ソース言語を直接インスタンス化し、GTX リソースを直接使用できます。 GTX ライン レートを動的に設定するには、GTX コントロール モジュールも必要です。このモジュールはザイリンクスの公式設計プランを参照しており、SDI モードの動的モニタリング、DRP の動的設定などの機能を備えています。この計画はザイリンクスの公式設計を参照しており、GTX デシリアル化およびシリアル化モジュールのコード構造は次のとおりです。

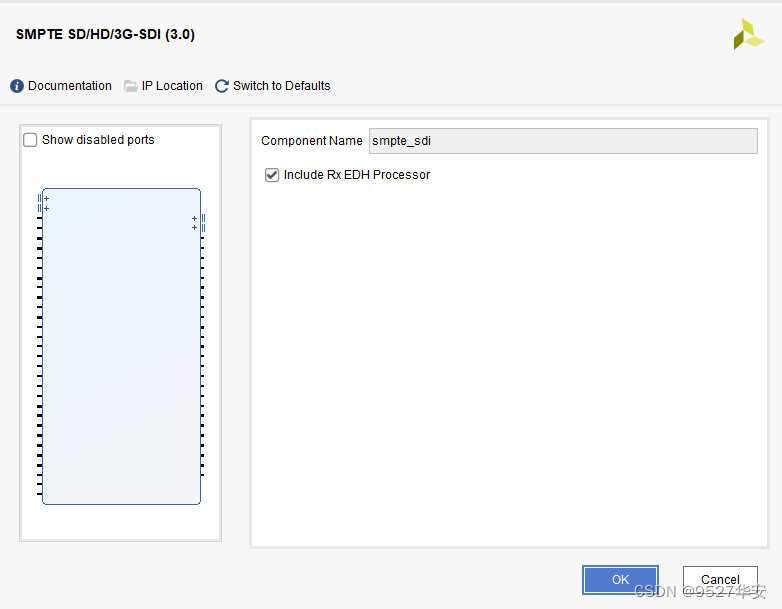

SMPTE SD/HD/3G SDI IP コアは、ザイリンクス シリーズ FPGA の SDI ビデオ エンコードおよびデコード用の独自の IP です。vivado の UI インターフェイスは非常に簡単です。

SMPTE SD/HD/3G SDI IP コアは GTX とともに使用する必要があります。SDI ビデオ受信の場合、IP は GTX からデータを受信し、SDI ビデオを BT1120 ビデオ出力にデコードします。SDI ビデオ送信の場合、IP は BT1120 を受信します。ユーザー側からビデオ データを取得し、BT1120 ビデオを SDI ビデオ出力にエンコードします。このソリューションは、SMPTE SD/HD/3G SDI IP コアのコード構造を次のように参照しています。

BT1120 to RGB モジュールの機能は、SMPTE SD/HD/3G SDI IP コア デコードによって BT1120 ビデオ出力を RGB888 ビデオに変換することです。BT1120 to CEA861 モジュール、YUV422 to YUV444 モジュール、YUV444 to RGB888 の 3 つのモジュールで構成されます。このソリューションは、ザイリンクスの公式設計が採用されており、BT1120 to RGB モジュールのコード構造は次のとおりです。

この設計のビデオ キャッシュ ソリューションは、2 チャネル ザイリンクス公式 VDMA イメージ キャッシュ アーキテクチャを採用しており、キャッシュ メディアは PS 側の DDR3 であり、最初の SDI ビデオは VDMA 経由で DDR に書き込まれ、その後読み出されてビデオ フュージョン オーバーレイ モジュールに送信されます。 2 番目の SDI ビデオは、VDMA を介して DDR に書き込まれた後、読み出されませんが、ビデオ フュージョン オーバーレイ モジュールを介して DDR3 から読み出されます。プロジェクトのソース コード 1 を例に挙げると、VDMA はザイリンクスのブロック デザインを使用して設計されています。以下に示すように、vivado:

レイテンシを短縮するために、VDMA は次のように 1 フレームをキャッシュするように設定されています。

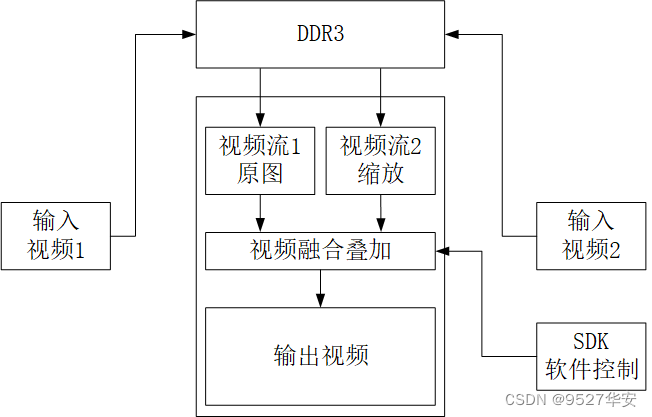

マルチチャンネル ビデオ フュージョン オーバーレイ設計のブロック図は次のとおりです。

マルチチャンネルビデオの融合とオーバーレイは、基礎となるビデオとオーバーレイビデオの融合と重ね合わせによって形成されます。基礎となるビデオは最初のチャンネルの入力ビデオであり、オーバーレイビデオは 2 番目のチャンネルのスケーリングされたビデオです。 SDK ソフトウェアは、2 チャンネル ビデオ フュージョンの透明度、オーバーレイ ビデオのズーム サイズ、オーバーレイ ビデオの表示位置、その他の情報を動的に設定します。 HLS ソリューション C++ コードは、RTL に合成され、IP にカプセル化され、vivado Call the IP で使用できます。このソリューションの詳細については、私の以前のブログのリンクを参照してください。

クリックして直接移動します

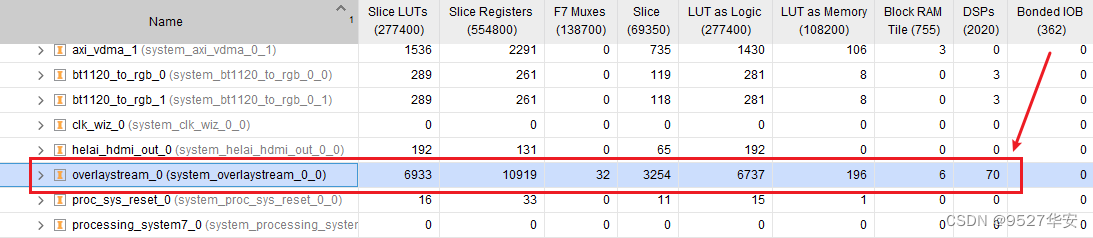

vivado でのこの IP の包括的なリソース使用量は次のとおりです。

HLS マルチチャンネル ビデオ フュージョン オーバーレイが正しく動作するには、SDK でドライバーとユーザー プログラムを実行する必要があります。プロジェクトに C 言語プログラムを提供しました。詳細については、HLS マルチチャンネル ビデオ フュージョン オーバーレイのスクリーンショットを参照してください。チャネル ビデオ フュージョン オーバーレイ コールは次のとおりです。

HDMI ビデオ出力アーキテクチャは次のとおりです。

ザイリンクスの公式設計を参照すると、VTC+AXI4-Stream To Video Out アーキテクチャを使用して出力ビデオを AXI4-Stream からネイティブ フォーマットに変換し、次に純粋な Verilog コードで実装された RGB888 to HDMI モジュールを使用して RGB888 を HDMI に変換し、最後に表示します。モニター経由での RGB888 to HDMI モジュールのコード構造は次のとおりです。

RGB888 to HDMI モジュールについては、私の以前のブログ、ブログ アドレスを参照してください。クリックして直接移動します

SDI ビデオ出力アーキテクチャは、まず VDMA によって読み取られた AXI4-Stream をネイティブ フォーマットに変換する必要があります。その後、RGB を BT1120 ビデオに変換できます。

SDI 出力モードでは、VGA タイミング モジュールのピクセル クロックは、SMPTE SD/HD/3G SDI IP コアの送信ユーザー クロックによって提供されます。たとえば、3G-SDI モードではピクセル クロックが異なります。 、HD-SDI 720P@60Hz モードでは、ピクセル クロックは 148.5M です。

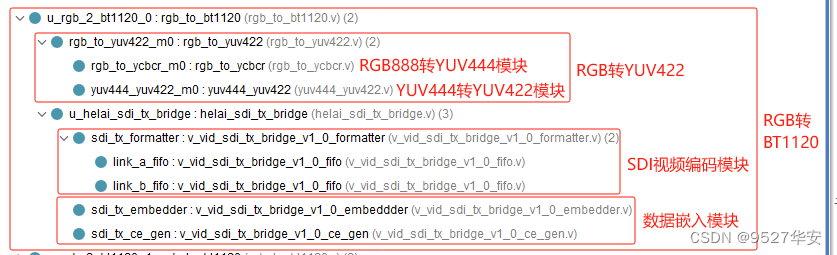

SDI 出力モードでは、RGB to BT1120 モジュールを使用する必要があります。RGB to BT1200 モジュールの機能は、ユーザー側の RGB ビデオを BT1200 ビデオに変換し、SMPTE SD/HD/3G SDI IP に出力することです。コア; RGB to BT1120 モジュールは、RGB888 to YUV444 モジュール、YUV444 to YUV422 モジュール、SDI ビデオ エンコーディング モジュール、およびデータ埋め込みモジュールで構成されます。このソリューションは、BT1120 to RGB モジュールのコード構造を参照しています。次のように:

これら 2 つの部分は、対応するモジュールを受信プロセスと共有します。これらのモジュールは、機能的には受信プロセスの逆プロセスであるため、再度説明しません。

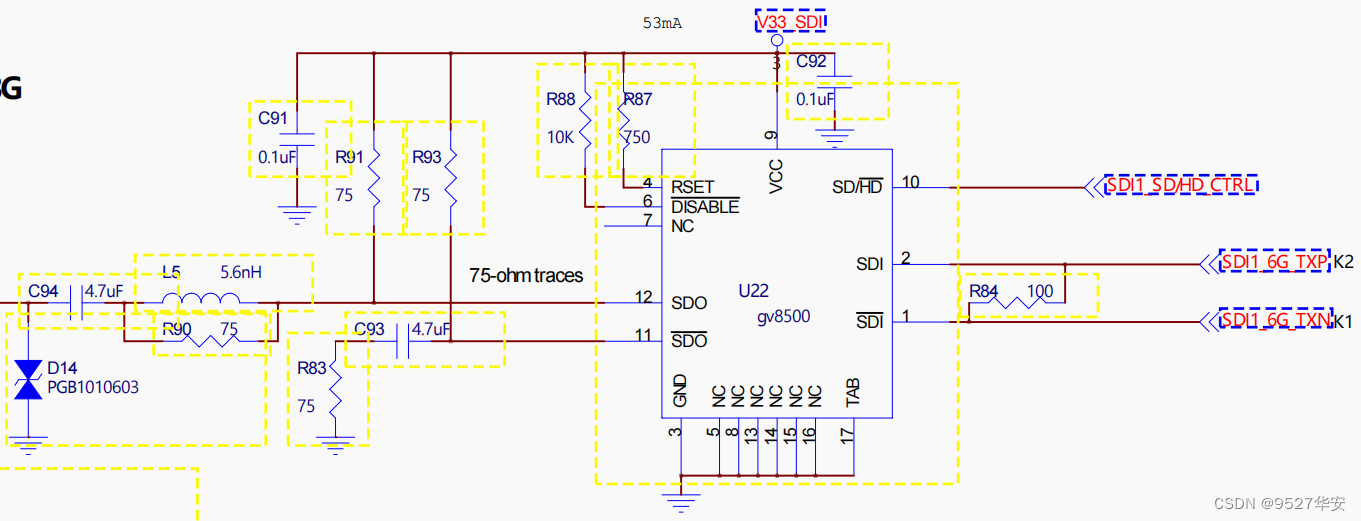

Gv8500 チップは、シングルエンドおよび強化されたドライバーへの差動変換機能を実現します。これは、公式のザイリンクス ソリューションを利用しているためです。もちろん、他のタイプのデバイスも使用できます。 Gv8500 ドライバーの概略図は次のとおりです。

SDI 出力モードでは、SDI to HDMI ボックスを使用する必要があります。私の手持ちのモニターには SDI インターフェイスがなく、SDI ビデオを表示するには HDMI インターフェイスのみが必要です。あなたのモニターには SDI インターフェイスが付いているので、直接接続できます。接続を見ると、私の SDI to HDMI ボックスは特定の店で 100 元未満で購入したことがわかります。

このブログでは 2 セットのプロジェクト ソース コードを提供します。プロジェクト ソース コード 1 を例として挙げると、他のプロジェクトも同様です。

プロジェクトのソース コード 1 を例に挙げると、プロジェクトのソース コード構造は次のとおりです。他のプロジェクトも同様です。

プロジェクト ソース コードの PL 側クロックは Zynq ソフト コアによって提供されるため、Zynq を起動するには SDK を実行する必要があります。また、ビデオ フュージョン オーバーレイや VDMA などの IP コアが適切に動作するには、ソフトウェア ドライバーを実行する必要があります。 SDK ソフトウェアのコード構造は次のとおりです。

SDK コードの構成は次のとおりです。ユーザーは自分のニーズに応じて任意に変更できます。

最初のビデオは、解像度 1920x1080 の最下層ビデオです。

2 番目のチャネル ビデオは、解像度 1920x1080 のオーバーレイ ビデオです。オーバーレイ ビデオの座標 (400、200) から 1000x800 の領域をオーバーレイ フュージョン ビデオとして取得します。

前の手順で取得した 600x600 のオーバーレイ フュージョン ビデオを 960x540 にスケールします。

前のステップで 960x540 のスーパーインポーズされたフュージョン ビデオを、下にあるビデオの (0,0) 座標から開始してオーバーレイし、下にあるレイヤーとオーバーレイ レイヤーの透明度を 80 に設定します。

開発ボード FPGA モデル: Xilinx-Zynq7100–xc7z100ffg900-2;

開発環境: Vivado2019.1;

入力: 3G-SDI カメラまたは HDMI to SDI ボックス、解像度 1920x1080@60Hz。

出力: HDMI、解像度 1920x1080@60Hz;

キャッシュ ソリューション: ザイリンクス公式 VDMA ソリューション。

キャッシュメディア: PS 側 DDR3;

ビデオ フュージョンおよびオーバーレイ ソリューション: HLS に基づいた自社開発のマルチチャンネル ビデオ フュージョンおよびオーバーレイ。

プロジェクトの役割: このプロジェクトの目的は、読者が SDI を HDMI に実装するための Zynq シリーズ FPGA の設計機能を習得し、独自のプロジェクトを移植して設計できるようにすることです。

プロジェクトのブロック デザインとプロジェクト コード アーキテクチャについては、第 3 章の「プロジェクト ソース コード アーキテクチャ」セクションを参照してください。

プロジェクトのリソース消費量と電力消費量は次のとおりです。

開発ボード FPGA モデル: Xilinx-Zynq7100–xc7z100ffg900-2;

開発環境: Vivado2019.1;

入力: 3G-SDI カメラまたは HDMI to SDI ボックス、解像度 1920x1080@60Hz。

出力: 3G-SDI、解像度 1920x1080@60Hz;

キャッシュ ソリューション: ザイリンクス公式 VDMA ソリューション。

キャッシュメディア: PS 側 DDR3;

ビデオ フュージョンおよびオーバーレイ ソリューション: HLS に基づいた自社開発のマルチチャンネル ビデオ フュージョンおよびオーバーレイ。

プロジェクトの役割: このプロジェクトの目的は、読者が SDI を HDMI に実装するための Zynq シリーズ FPGA の設計機能を習得し、独自のプロジェクトを移植して設計できるようにすることです。

プロジェクトのブロック デザインとプロジェクト コード アーキテクチャについては、第 3 章の「プロジェクト ソース コード アーキテクチャ」セクションを参照してください。

プロジェクトのリソース消費量と電力消費量は次のとおりです。

1: vivado バージョンがこのプロジェクトの vivado バージョンと一致している場合は、プロジェクトを直接開きます。

2: vivado のバージョンがこのプロジェクトの vivado バージョンよりも低い場合は、プロジェクトを開いて [ファイル] –> [名前を付けて保存] をクリックする必要があります。ただし、この方法は vivado のバージョンを vivado にアップグレードするのが安全ではありません。このプロジェクトのバージョン以降。

3: vivado バージョンがこのプロジェクトの vivado バージョンより高い場合、解決策は次のとおりです。

プロジェクトを開くと、次のように IP がロックされていることがわかります。

現時点では、IP をアップグレードする必要があります。手順は次のとおりです。

あなたの FPGA モデルが私のものと一致しない場合は、次のように FPGA モデルを変更する必要があります。

FPGA モデルを変更した後は、IP をアップグレードする必要があります。IP をアップグレードする方法は前述しました。

1: 各ボードの DDR は必ずしも完全に同じであるとは限らないため、独自の回路図に従って MIG IP を構成する必要があります。元のプロジェクトの MIG を直接削除し、IP を再度追加して再構成することもできます。

2: 独自の回路図に従ってピン制約を変更し、それを xdc ファイル内で変更します。

3: 純粋な FPGA を Zynq に移植するには、プロジェクトに zynq ソフト コアを追加する必要があります。

準備が必要な機材は以下の通りです。

FPGA開発ボード。

SDI カメラまたは HDMI to SDI ボックス。

SDIからHDMIへのボックス。

HDMIディスプレイ。

私の開発ボードは次のように接続されています。

プロジェクトのソース コード 1 を例にすると、出力は次のようになります。

Zynq-SDI-ビデオ フュージョン オーバーレイ

おまけ:エンジニアリングコードの取得

コードが大きすぎるため、電子メールで送信できません。特定のネットワーク ディスク リンクを介して送信されます。

情報の入手方法: 非公開、または記事の最後にある V 名刺。

ネットワークディスク情報は以下のとおりです。

さらに、多くの友人がサービスの内容やオプションを充実させることを期待して、このブロガーに多くの意見や提案を与えてくれました。友人によってニーズが異なるため、このブロガーは次のサービスも提供しています。