2024-07-12

한어Русский языкEnglishFrançaisIndonesianSanskrit日本語DeutschPortuguêsΕλληνικάespañolItalianoSuomalainenLatina

Actuellement, il existe deux solutions pour que le FPGA implémente l'encodage et le décodage vidéo SDI : l'une consiste à utiliser des puces d'encodage et de décodage dédiées, telles que le récepteur typique GS2971, et l'émetteur GS2972. L'avantage est par exemple la simplicité du récepteur GS2971. décode le SDI en YCrCb422 parallèle et le GS2972 transmet. L'appareil code directement le YCrCb422 parallèle en vidéo SDI. L'inconvénient est que le coût est relativement élevé. Vous pouvez rechercher les prix du GS2971 et du GS2972 sur Baidu. Département de ressources logiques FPGA pour implémenter l'encodage et le décodage SDI et utiliser les ressources GTP/GTX du FPGA de la série Xilinx Pour réaliser la désérialisation, utilisez les ressources SMPTE SDI du FPGA de la série Xilinx pour implémenter l'encodage et le décodage SDI. les ressources sont raisonnablement utilisées et les ressources GTP/GTX ne sont pas utilisées en vain. L'inconvénient est que l'opération est plus difficile et nécessite un niveau technique plus élevé de développeurs FPGA. Il est intéressant de noter que ces deux solutions ont des solutions correspondantes ici sur ce blog, notamment des cartes de développement matérielles FPGA, du code source d'ingénierie, etc.

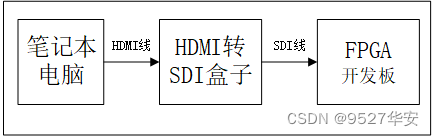

Cette conception est basée sur la carte de développement FPGA Zynq7100 de la série Zynq pour implémenter l'encodage et le décodage vidéo SDI + la mise à l'échelle de l'image + l'épissage vidéo multicanal. Il existe deux sources d'entrée, l'une est une caméra 3G-SDI avec une résolution de 1920 x 1080 @. 60 Hz et HD-SDI peuvent également être utilisés. Ou une caméra SD-SDI, car cette conception est adaptative à trois vidéos SDI ; un autre boîtier HDMI vers 3G-SDI, le boîtier est connecté à un ordinateur portable pour simuler une caméra SDI ; Les vidéos SDI sont connectées à la carte de développement FPGA via une prise BNC de câbles coaxiaux, puis la vidéo coaxiale passe par la puce Gv8601a intégrée pour réaliser les fonctions de conversion asymétrique en égaliseur différentiel et équilibré, puis le signal vidéo SDI différentiel entre dans la GTX ; ressource à grande vitesse à l'intérieur du FPGA pour réaliser une conversion série à parallèle à grande vitesse des données. Bo appelle cela la désérialisation ; la vidéo parallèle désérialisée est ensuite envoyée au noyau IP SMPTE SD/HD/3G SDI unique du FPGA de la série Xilinx pour effectuer une SDI. opération de décodage vidéo et sortie vidéo BT1120 À ce stade, l'opération de décodage vidéo SDI est terminée et vous pouvez effectuer des opérations de traitement d'image de routine ;

Le but de cette conception est de produire une vidéo SDI décodée après mise à l'échelle de l'image + fusion et superposition vidéo multicanaux. En réponse aux besoins actuels des projets courants sur le marché, ce blog a conçu deux méthodes de sortie, l'une est la sortie HDMI et l'autre. l'autre est la sortie 3G-SDI, les deux méthodes nécessitent que le décodage de la vidéo BT1120 soit converti en RVB et les opérations de mise en cache d'image ; cette conception utilise le module BT1120 en RVB pour réaliser la conversion de format vidéo bidirectionnelle de Xilinx. mettre en œuvre la mise en cache et la mise en cache des images. Le support est intégré à la DDR3 côté PS ; la première vidéo SDI est écrite sur DDR via VDMA, puis lue et envoyée au module de superposition de fusion vidéo. La deuxième vidéo SDI n'est pas lue après avoir été écrite en DDR. via VDMA, mais est superposé via la fusion vidéo. Le module lit à partir de DDR3. À ce stade, la vidéo à 2 canaux est entrée dans le module de fusion et de superposition vidéo, puis elle entre dans le module d'envoi HDMI pour sortir le HDMI ; affichage, qui est la méthode de sortie HDMI ; ou le format vidéo est réalisé via la conversion du module RVB vers BT1120, puis la vidéo entre dans le noyau IP SMPTE SD/HD/3G SDI, effectue les opérations d'encodage vidéo SDI et produit la vidéo SDI, puis passe par les ressources GTX haute vitesse à l'intérieur du FPGA pour réaliser la conversion des données parallèles en série haute vitesse, que ce blog appelle série, le signal différentiel haute vitesse entre ensuite dans la puce Gv8500 embarquée pour réaliser les fonctions de conversion différentielle en asymétrique et amélioration du pilote. La vidéo SDI est sortie via la prise BNC de la carte de développement FPGA et est connectée au boîtier SDI vers HDMI via un câble coaxial à l'écran HDMI. Il s'agit de la méthode de sortie SDI proposée par ce blog ; 2 ensembles de codes sources du projet, comme suit :

Les deux ensembles de codes sources du projet ci-dessus sont expliqués comme suit pour faciliter la compréhension des lecteurs :

Code source du projet 1

Le modèle FPGA de la carte de développement est Xilinx–>Xilinx-Zynq7100–xc7z100ffg900-2 ; il existe deux sources d'entrée, l'une est une caméra 3G-SDI avec une résolution de 1920 x 1080 à 60 Hz et l'autre est une HDMI vers 3G-SDI. Le boîtier est connecté à un ordinateur portable. Caméra SDI analogique avec une résolution de 1920 x 1080 à 60 Hz ; les deux vidéos d'entrée sont envoyées au FPGA via les deux puces Gv8601a intégrées pour obtenir une conversion asymétrique en égaliseur différentiel et équilibré ; via les deux canaux GTX, la vidéo SDI est désérialisée en données parallèles ; puis via 2 canaux du noyau IP SMPTE SDI, le SDI est décodé en 2 canaux de données BT1120 puis via 2 canaux du module BT1120 vers RVB, le BT1120 est converti ; dans la vidéo RGB888 ; puis via 2 canaux de la vidéo officielle Xilinx vers le noyau IP AXI4-Stream pour réaliser la conversion des données RGB888 en flux de données AXI4-Stream ; puis écrire la vidéo dans le cache DDR3 côté PS via le VDMA officiel Xilinx à 2 canaux ; solution de cache d'images ; puis le noyau IP de fusion et de superposition vidéo multicanal auto-développé basé sur HLS implémente l'opération de fusion et de superposition vidéo à 2 canaux ; Entrez ensuite le noyau IP officiel AXI4-Stream To Video Out pour convertir l'AXI4- Diffusez le flux vidéo vers le flux vidéo natif ; puis envoyez la vidéo de superposition de fusion au module RVB vers HDMI pour convertir la vidéo RGB888 en vidéo HDMI et la résolution de sortie est de 1920 x 1080 à 60 Hz. Pour des effets d'affichage détaillés, veuillez consulter la vidéo de démonstration de sortie sur. la fin de l'article ; l'image est enfin affichée via un écran HDMI ; ce projet nécessite l'exécution du soft core Zynq adapté aux scénarios d'épissage vidéo SDI ;

Code source du projet 2

Le modèle FPGA de la carte de développement est Xilinx–>Xilinx-Zynq7100–xc7z100ffg900-2 ; il existe deux sources d'entrée, l'une est une caméra 3G-SDI avec une résolution de 1920 x 1080 à 60 Hz et l'autre est une HDMI vers 3G-SDI. Le boîtier est connecté à un ordinateur portable. Caméra SDI analogique avec une résolution de 1920 x 1080 à 60 Hz ; les deux vidéos d'entrée sont envoyées au FPGA via les deux puces Gv8601a intégrées pour obtenir une conversion asymétrique en égaliseur différentiel et équilibré ; via les deux canaux GTX, la vidéo SDI est désérialisée en données parallèles ; passez ensuite par 2 canaux du noyau IP SMPTE SDI pour décoder le SDI en 2 canaux de données BT1120, puis passez par 2 canaux du module BT1120 vers RVB pour convertir BT1120 en RVB888 ; vidéo ; puis passez par 2 canaux de la vidéo officielle de Xilinx vers le noyau IP AXI4-Stream pour réaliser la conversion des données RGB888 en flux de données AXI4-Stream ; puis la vidéo est écrite dans le cache DDR3 côté PS via l'image VDMA officielle de Xilinx à 2 canaux ; solution de cache ; puis le noyau IP de fusion vidéo et de superposition multicanal auto-développé basé sur HLS implémente l'opération de fusion et de superposition vidéo à 2 canaux ; Entrez ensuite le noyau IP officiel AXI4-Stream To Video Out pour convertir le flux AXI4 ; flux vidéo vers le flux vidéo natif ; puis envoyez la vidéo de superposition de fusion au module RVB vers BT1120 pour convertir la vidéo RGB888 en vidéo BT1120, puis passez le noyau IP SMPTE SD/HD/3G encode la vidéo BT1120 en vidéo SDI ; convertit les données parallèles SDI en signaux série à grande vitesse via les ressources GTX à grande vitesse à l'intérieur du FPGA; puis utilise la puce Gv8500 intégrée pour mettre en œuvre la conversion différentielle en asymétrique et en pilote. Après amélioration, la résolution de sortie est enfin de 1920x1080 @ 60Hz; , un boîtier SDI vers HDMI est utilisé pour se connecter à un écran HDMI pour l'affichage ; ce projet nécessite l'exécution du noyau logiciel Zynq adapté aux scénarios SDI vers SDI ;

Ce projet et son code source incluent à la fois des parties écrites par moi-même et des parties obtenues auprès de chaînes publiques sur Internet (y compris CSDN, le site officiel de Xilinx, le site officiel d'Altera, etc.). Si vous pensez que c'est offensant, veuillez envoyer un message privé à). critiquer et éduquer ; sur cette base, ce projet Le projet et son code source sont uniquement destinés à l'étude et à la recherche personnelles des lecteurs ou des fans, et il est interdit de les utiliser à des fins commerciales si des problèmes juridiques découlent d'une utilisation commerciale par les lecteurs ou les fans eux-mêmes. , ce blog et le blogueur n'ont rien à voir avec cela, alors utilisez-le avec prudence. . .

La page d'accueil de mon blog contient une colonne vidéo SDI, qui regorge de code source d'ingénierie SDI du codec FPGA et d'introduction au blog ; il existe des codecs SDI basés sur GS2971/GS2972 et des codecs SDI basés sur les ressources GTP/GTX ; SDI, 6G-SDI, 12G-SDI, etc. ; le lien d'adresse de colonne est le suivant :

Cliquez pour y aller directement

Ce blog a auto-développé une application de superposition de fusion vidéo multicanal. J'ai déjà écrit un blog spécifiquement. Le lien vers l'adresse du blog est le suivant :

Cliquez pour y aller directement

Le schéma fonctionnel du principe de conception est le suivant :

Avis! ! ! !

Avis! ! ! !

Flèche violette : chemin de sortie 3G-SDI

Flèche rouge : chemin de sortie HDMI

Il existe deux périphériques d'entrée SDI, qui sont connectés à l'interface d'entrée vidéo SDI bidirectionnelle de la carte de développement FPGA ; l'un est une caméra 3G-SDI avec une résolution de 1920 x 1080 à 60 Hz. Les caméras HD-SDI ou SD-SDI peuvent également être connectées. être utilisé en raison de cette conception Il est adaptatif à trois types de vidéos SDI : un autre boîtier HDMI vers 3G-SDI, le boîtier est connecté à un ordinateur portable pour simuler une caméra SDI, est relativement cher, et les amis avec un budget limité peuvent le faire ; pensez à utiliser un boîtier HDMI vers SDI pour simuler une caméra SDI. Hezibao coûte environ 100 yuans ; lorsque vous utilisez un boîtier HDMI vers SDI, la source d'entrée peut être un ordinateur portable, c'est-à-dire utiliser un ordinateur portable pour vous connecter à l'interface d'entrée HDMI du Boîtier HDMI vers SDI via un câble HDMI, puis utilisez un câble SDI pour connecter le boîtier HDMI au SDI. L'interface de sortie SDI à la carte de développement FPGA est la suivante :

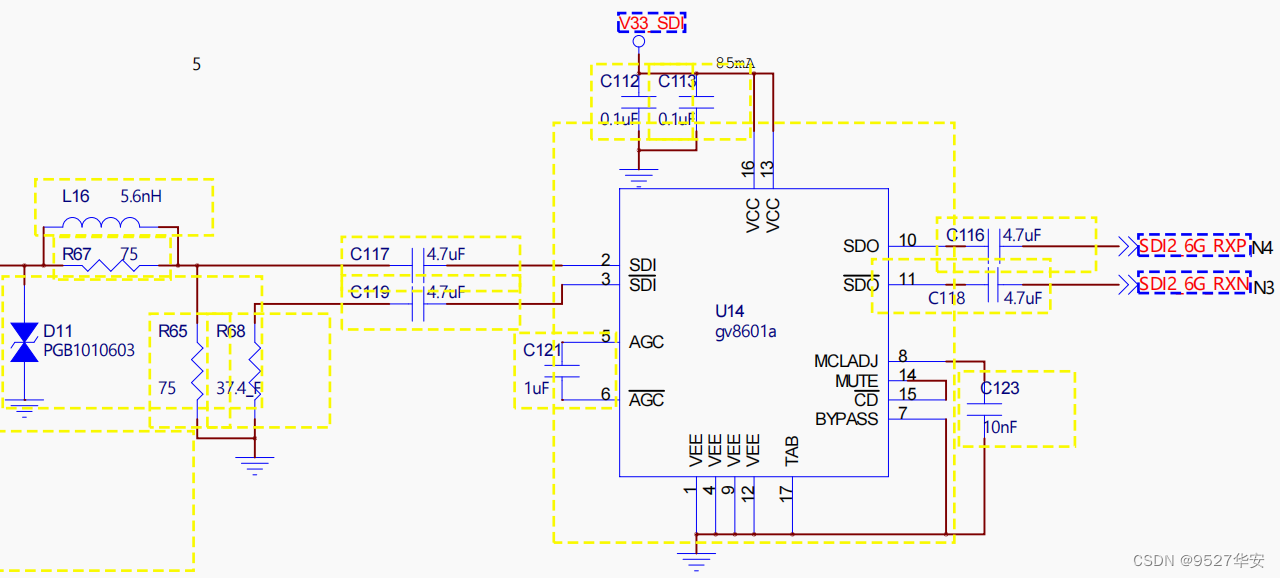

La puce Gv8601a réalise les fonctions de conversion asymétrique en égaliseur différentiel et symétrique. Le Gv8601a est choisi ici car il s'appuie sur la solution officielle Xilinx. Bien entendu, d'autres types d'appareils peuvent également être utilisés. Le schéma de principe de l'égaliseur Gv8601a est le suivant :

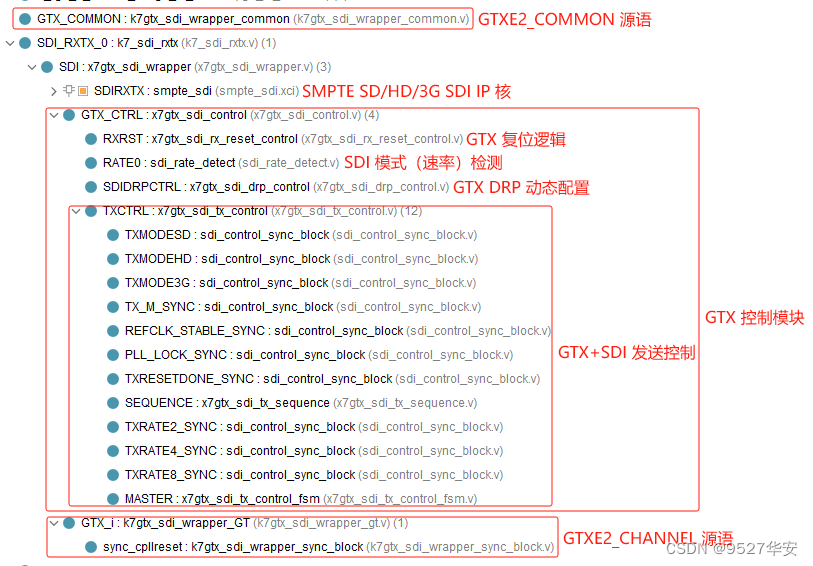

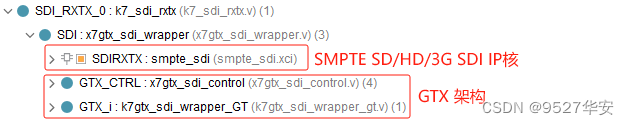

Cette conception utilise les ressources uniques de traitement du signal GTX à grande vitesse de Xilinx pour réaliser la désérialisation et la sérialisation des signaux vidéo différentiels SDI. Pour la réception vidéo SDI, GTX joue le rôle de désérialisation, c'est-à-dire décoder les signaux différentiels série haute vitesse d'entrée en numérique parallèle. signal ; pour la transmission vidéo SDI, GTX joue le rôle de sérialisation, c'est-à-dire de sérialisation du signal numérique parallèle d'entrée en un signal différentiel série à grande vitesse ; l'utilisation de GTX nécessite généralement l'instanciation du noyau IP GTX, via vivado Configurez l'interface utilisateur. Interface, mais cette conception nécessite une identification automatique et un traitement adaptatif des vidéos SD-SDI, HD-SDI et 3G-SDI, donc GTX doit avoir la fonction de changer dynamiquement le débit de ligne. Cette fonction peut être configurée via l'interface DRP. Il peut également être configuré via l'interface de taux de GTX, vous ne pouvez donc pas utiliser l'interface utilisateur de vivado pour la configuration, mais vous pouvez directement instancier les langages sources GTXE2_CHANNEL et GTXE2_COMMON de GTX et utiliser directement les ressources GTX. afin de configurer dynamiquement le débit de la ligne GTX, vous avez également besoin d'un module de contrôle GTX, ce module fait référence au plan de conception officiel de Xilinx, et a les fonctions de surveillance dynamique du mode SDI, de configuration dynamique du DRP, etc. plan fait référence à la conception officielle de Xilinx ; la structure du code du module de désérialisation et de sérialisation GTX est la suivante :

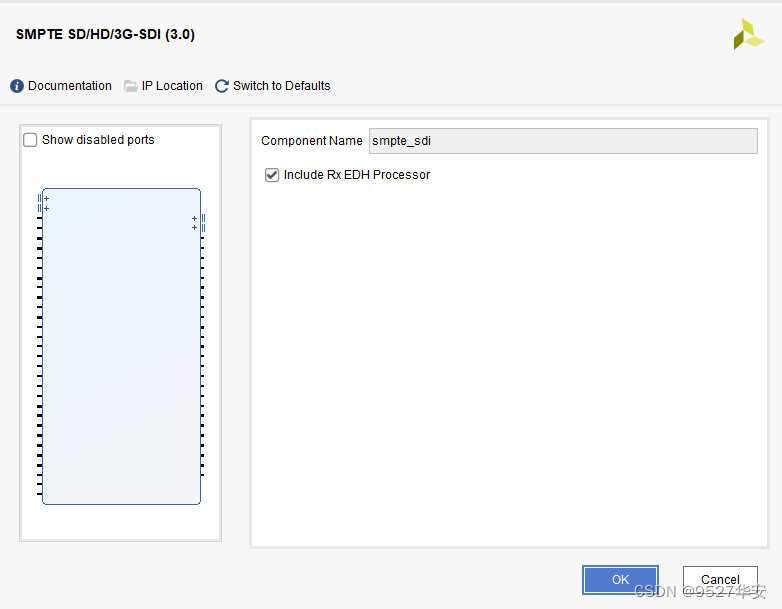

Le noyau IP SMPTE SD/HD/3G SDI est une IP unique pour l'encodage et le décodage vidéo SDI des FPGA de la série Xilinx. La configuration IP est très simple à utiliser. L'interface utilisateur de vivado est la suivante :

Le noyau IP SMPTE SD/HD/3G SDI doit être utilisé avec GTX Pour la réception vidéo SDI, l'IP reçoit les données de GTX, puis décode la vidéo SDI en sortie vidéo BT1120. Pour la transmission vidéo SDI, l'IP reçoit le BT1120. données vidéo du côté utilisateur, puis code la vidéo BT1120 en sortie vidéo SDI ; cette solution fait référence à la conception officielle de Xilinx :

La fonction du module BT1120 vers RGB est de convertir la sortie vidéo BT1120 par décodage SMPTE SD/HD/3G SDI IP core en vidéo RGB888. Il se compose de trois modules : module BT1120 vers CEA861, module YUV422 vers YUV444 et YUV444 vers RGB888. Cette solution fait référence à la conception officielle de Xilinx. La structure du code du module BT1120 vers RVB est la suivante :

La solution de cache vidéo de cette conception adopte l'architecture de cache d'image VDMA officielle de Xilinx à 2 canaux ; le support de cache est de la DDR3 côté PS ; la première vidéo SDI est écrite en DDR via VDMA, puis lue et envoyée au module de superposition de fusion vidéo ; .La deuxième vidéo SDI Après avoir écrit sur DDR via VDMA, elle n'est pas lue, mais est lue à partir de DDR3 via le module de superposition de fusion vidéo. En prenant le code source du projet 1 comme exemple, VDMA est conçu en utilisant la conception de blocs de Xilinx. vivado, comme indiqué ci-dessous :

Afin de réduire la latence, VDMA est configuré pour mettre en cache 1 trame, comme suit :

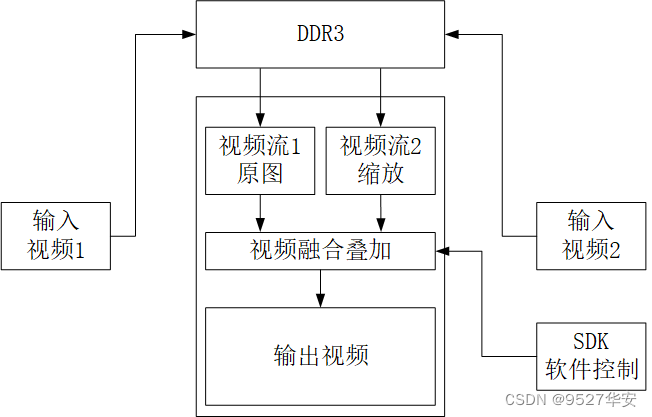

Le schéma fonctionnel de conception de superposition de fusion vidéo multicanal est le suivant :

La fusion et la superposition vidéo multicanaux sont formées par la fusion et la superposition de la vidéo sous-jacente et de la vidéo superposée. La vidéo sous-jacente est la vidéo d'entrée du premier canal et la vidéo superposée est la vidéo mise à l'échelle du deuxième canal. les vidéos sont fusionnées et sorties, ce qui peut être le logiciel SDK configure dynamiquement la transparence de la fusion vidéo à 2 canaux, la taille du zoom de la vidéo superposée, la position d'affichage de la vidéo superposée et d'autres informations que la conception est mise en œuvre à l'aide du ; Le code C++ de la solution HLS est synthétisé en RTL et encapsulé dans IP, qui peut être utilisé dans vivado Call the IP. Pour plus de détails sur cette solution, veuillez vous référer à mon blog précédent. Le lien du blog est le suivant :

Cliquez pour y aller directement

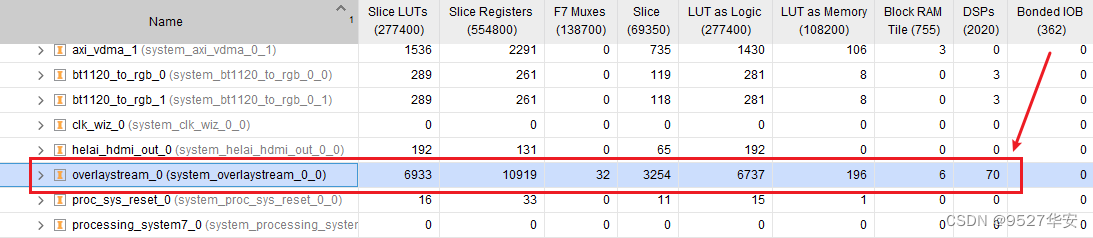

L'utilisation complète des ressources de cette adresse IP dans vivado est la suivante :

La superposition de fusion vidéo multicanal HLS doit exécuter le pilote et le programme utilisateur dans le SDK pour fonctionner correctement. J'ai fourni un programme en langage C dans le projet, veuillez vous référer au code source du projet pour plus de détails ; L'appel de superposition de fusion vidéo de canal est le suivant :

L'architecture de la sortie vidéo HDMI est la suivante :

En vous référant à la conception officielle de Xilinx, utilisez l'architecture VTC+AXI4-Stream To Video Out pour convertir la vidéo de sortie d'AXI4-Stream au format natif ; puis utilisez le module RGB888 vers HDMI implémenté dans du code Verilog pur pour convertir RGB888 en HDMI, et enfin afficher. via le moniteur, la structure du code du module RGB888 vers HDMI est la suivante :

Concernant le module RGB888 vers HDMI, merci de vous référer à mon précédent blog, adresse du blog :Cliquez pour y aller directement

L'architecture de sortie vidéo SDI doit d'abord convertir le flux AXI4 lu par VDMA au format natif. Après avoir obtenu la vidéo RGB888, elle peut ensuite convertir la vidéo RVB en BT1120 en BT1120.

En mode de sortie SDI, l'horloge pixel du module de synchronisation VGA est fournie par l'horloge utilisateur d'envoi du noyau IP SMPTE SD/HD/3G SDI. L'horloge pixel est différente selon les modes SDI, par exemple en mode 3G-SDI. , l'horloge des pixels est de 148,5 M. En mode HD-SDI 720P @ 60 Hz, l'horloge des pixels est de 74,25 M.

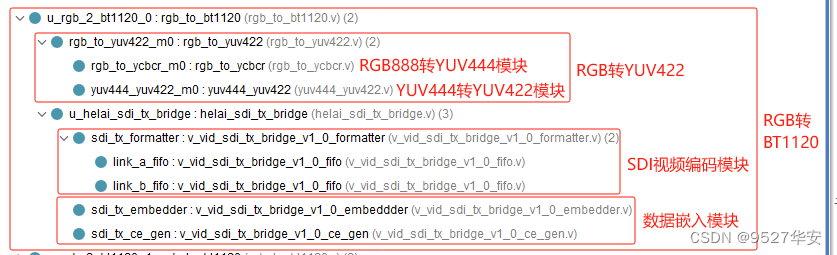

En mode de sortie SDI, le module RVB vers BT1120 doit être utilisé ; la fonction du module RVB vers BT1200 est de convertir la vidéo RVB du côté utilisateur en vidéo BT1200 et de la transmettre au SMPTE SD/HD/3G SDI IP. noyau ; le module RVB vers BT1120 se compose d'un module RGB888 vers YUV444, d'un module YUV444 vers YUV422, d'un module d'encodage vidéo SDI et d'un module d'intégration de données. Cette solution fait référence à la structure de code du module BT1120 vers RVB ; comme suit:

Ces deux parties partagent les modules correspondants avec le processus récepteur, qui sont fonctionnellement le processus inverse du processus récepteur et ne seront pas décrits à nouveau ;

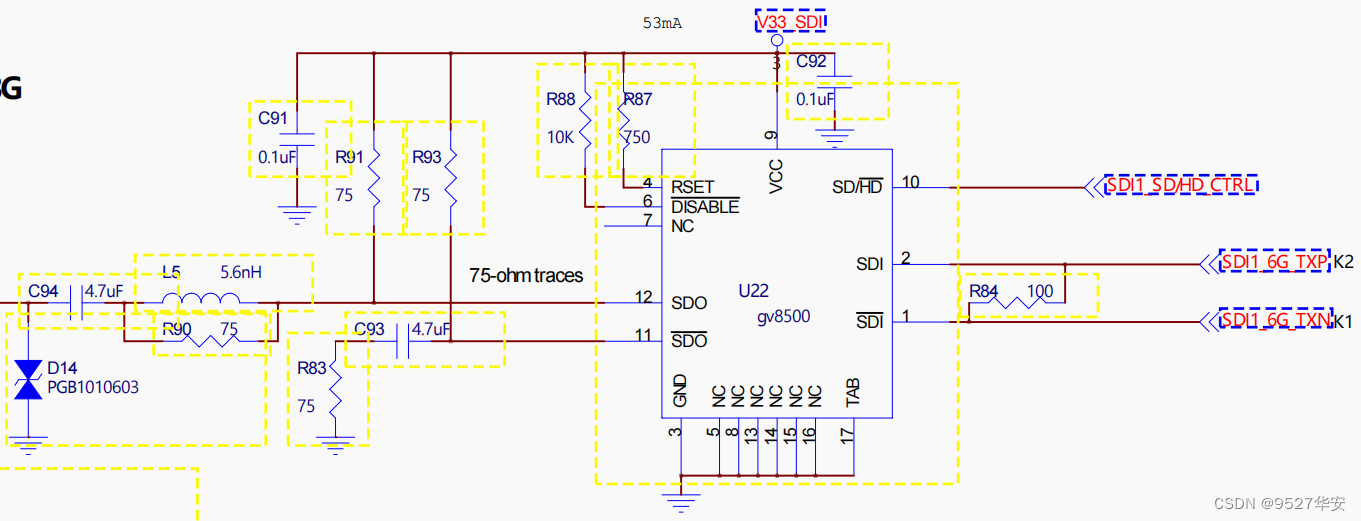

La puce Gv8500 réalise les fonctions de conversion différentielle en pilote asymétrique et amélioré. Le Gv8500 est choisi ici car il s'appuie sur la solution officielle Xilinx. Bien entendu, d'autres types de dispositifs peuvent également être utilisés. Le diagramme schématique du pilote Gv8500 est le suivant :

En mode de sortie SDI, vous devez utiliser un boîtier SDI vers HDMI, car le moniteur dans ma main n'a pas d'interface SDI, seulement une interface HDMI. Afin d'afficher la vidéo SDI, cela ne peut être fait que si. votre moniteur dispose d'une interface SDI, vous pouvez directement La connexion montre que mon boîtier SDI vers HDMI a été acheté dans un certain magasin pour moins de 100 yuans ;

Ce blog fournit 2 ensembles de codes sources de projet. En prenant le code source du projet 1 comme exemple, la conception de vivado Block Design est la suivante. La conception de Block Design fait partie de l'architecture de cache d'images :

En prenant le code source du projet 1 comme exemple, la structure du code source du projet est la suivante. Les autres projets sont similaires :

L'horloge côté PL du code source du projet est fournie par le noyau logiciel Zynq, le SDK doit donc être exécuté pour démarrer Zynq. De plus, les cœurs IP tels que la superposition de fusion vidéo et VDMA doivent exécuter des pilotes logiciels pour fonctionner correctement. La structure du code du logiciel SDK est la suivante :

La configuration dans le code du SDK est la suivante, les utilisateurs peuvent la modifier arbitrairement en fonction de leurs propres besoins ;

La première vidéo est la vidéo de la couche inférieure avec une résolution de 1920 x 1080 ;

La vidéo du deuxième canal est la vidéo de superposition avec une résolution de 1 920 x 1 080. Prenez une zone de 1 000 x 800 à partir des coordonnées de la vidéo de superposition (400, 200) comme origine de la vidéo de fusion de superposition ;

Mettez à l'échelle la vidéo de fusion superposée 600 x 600 obtenue à l'étape précédente à 960 x 540 ;

Superposez la vidéo de fusion superposée 960 x 540 à l'étape précédente en commençant par la coordonnée (0,0) de la vidéo sous-jacente et définissez la transparence des calques sous-jacents et superposés sur 80 ;

Modèle de carte de développement FPGA : Xilinx-Zynq7100–xc7z100ffg900-2 ;

Environnement de développement : Vivado2019.1 ;

Entrée : caméra 3G-SDI ou boîtier HDMI vers SDI, résolution 1920x1080@60Hz ;

Sortie : HDMI, résolution 1920 x 1080 à 60 Hz ;

Solution de mise en cache : solution VDMA officielle de Xilinx ;

Support de cache : DDR3 côté PS ;

Solution de fusion et de superposition vidéo : fusion et superposition vidéo multicanaux auto-développées basées sur HLS ;

Rôle du projet : le but de ce projet est de permettre aux lecteurs de maîtriser les capacités de conception des FPGA de la série Zynq pour implémenter le SDI vers HDMI, afin qu'ils puissent transplanter et concevoir leurs propres projets ;

Pour la conception des blocs du projet et l'architecture du code du projet, veuillez vous référer à la section « Architecture du code source du projet » au chapitre 3 ;

La consommation de ressources et la consommation électrique du projet sont les suivantes :

Modèle de carte de développement FPGA : Xilinx-Zynq7100–xc7z100ffg900-2 ;

Environnement de développement : Vivado2019.1 ;

Entrée : caméra 3G-SDI ou boîtier HDMI vers SDI, résolution 1920x1080@60Hz ;

Sortie : 3G-SDI, résolution 1920 x 1080 à 60 Hz ;

Solution de mise en cache : solution VDMA officielle de Xilinx ;

Support de cache : DDR3 côté PS ;

Solution de fusion et de superposition vidéo : fusion et superposition vidéo multicanaux auto-développées basées sur HLS ;

Rôle du projet : le but de ce projet est de permettre aux lecteurs de maîtriser les capacités de conception des FPGA de la série Zynq pour implémenter le SDI vers HDMI, afin qu'ils puissent transplanter et concevoir leurs propres projets ;

Pour la conception des blocs du projet et l'architecture du code du projet, veuillez vous référer à la section « Architecture du code source du projet » au chapitre 3 ;

La consommation de ressources et la consommation électrique du projet sont les suivantes :

1 : Si votre version vivado est cohérente avec la version vivado de ce projet, ouvrez directement le projet ;

2 : Si votre version vivado est inférieure à la version vivado de ce projet, vous devez ouvrir le projet et cliquer sur Fichier -> Enregistrer sous. Cependant, cette méthode n'est pas sûre. Le moyen le plus sûr consiste à mettre à niveau votre version vivado vers la version vivado. de ce projet version ou supérieure ;

3 : Si votre version vivado est supérieure à la version vivado de ce projet, la solution est la suivante :

Après avoir ouvert le projet, vous constaterez que les IP sont verrouillées, comme suit :

À ce stade, vous devez mettre à niveau l’IP. Les étapes sont les suivantes :

Si votre modèle FPGA n'est pas cohérent avec le mien, vous devez modifier le modèle FPGA comme suit :

Après avoir modifié le modèle FPGA, vous devez mettre à niveau l'IP. La méthode de mise à niveau de l'IP a été décrite précédemment ;

1 : Comme le DDR de chaque carte n'est pas nécessairement exactement le même, l'IP MIG doit être configuré selon votre propre schéma. Vous pouvez même supprimer directement le MIG de mon projet d'origine, rajouter l'IP et le reconfigurer ;

2 : Modifiez les contraintes des broches selon votre propre diagramme schématique et modifiez-le dans le fichier xdc ;

3 : La transplantation d'un FPGA pur vers Zynq nécessite l'ajout d'un noyau logiciel zynq au projet ;

Le matériel à préparer est le suivant :

Conseil de développement FPGA ;

Caméra SDI ou boîtier HDMI vers SDI ;

Boîtier SDI vers HDMI ;

Affichage HDMI ;

Ma carte de développement est connectée comme suit :

En prenant le code source du projet 1 comme exemple, le résultat est le suivant :

Superposition de fusion Zynq-SDI-Vidéo

Bonus : Acquisition du code d'ingénierie

Le code est trop volumineux et ne peut pas être envoyé par e-mail. Il sera envoyé via un certain lien de disque réseau.

Comment obtenir des informations : en privé, ou la carte de visite V en fin d'article.

Les informations sur le disque réseau sont les suivantes :

En outre, de nombreux amis ont donné à ce blogueur de nombreuses opinions et suggestions, dans l'espoir d'enrichir le contenu et les options du service. Parce que différents amis ont des besoins différents, ce blogueur fournit également les services suivants :