моя контактная информация

Почтамезофия@protonmail.com

2024-07-12

한어Русский языкEnglishFrançaisIndonesianSanskrit日本語DeutschPortuguêsΕλληνικάespañolItalianoSuomalainenLatina

В настоящее время существует два решения для FPGA для реализации кодирования и декодирования видео SDI: одно — использовать специальные чипы кодирования и декодирования, такие как типичный приемник GS2971 и передатчик GS2972. Преимущество заключается в простоте. Например, непосредственно приемник GS2971. декодирует SDI в параллельный YCrCb422, а GS2972 передает. Устройство напрямую кодирует параллельный YCrCb422 в SDI-видео. Недостаток заключается в том, что стоимость относительно высока. Цены на GS2971 и GS2972 можно найти на Baidu. Отдел логических ресурсов FPGA для реализации кодирования и декодирования SDI и использования ресурсов GTP/GTX FPGA серии Xilinx. Чтобы добиться десериализации, используйте ресурсы SMPTE SDI FPGA серии Xilinx для реализации кодирования и декодирования SDI. ресурсы используются разумно, а ресурсы GTP/GTX не используются зря. Недостатком является то, что операция более сложна и требует более высокого технического уровня разработчиков FPGA. Интересно, что у этих двух решений есть соответствующие решения здесь, в этом блоге, включая платы разработки аппаратного обеспечения FPGA, исходный код для разработки и т. д.

Эта конструкция основана на плате разработки Zynq7100 FPGA серии Zynq для реализации кодирования и декодирования видео SDI + масштабирования изображения + склейки многоканального видео. Имеется два источника входного сигнала, один из которых — камера 3G-SDI с разрешением 1920x1080@. 60 Гц и HD-SDI. Или камера SD-SDI, поскольку эта конструкция адаптируется к трем видео SDI; еще один блок HDMI-3G-SDI, блок подключается к ноутбуку для имитации двух входов SDI; Видео SDI подключаются к плате разработки FPGA через коаксиальный кабель с разъемом BNC, а затем коаксиальное видео проходит через встроенный чип Gv8601a для реализации функций несимметричного преобразования в дифференциальный и балансный эквалайзер, после чего дифференциальный видеосигнал SDI поступает в GTX; высокоскоростной ресурс внутри FPGA для реализации высокоскоростного последовательного преобразования данных в параллельное. Бо называет это десериализацией; десериализованное параллельное видео затем отправляется в уникальное IP-ядро SMPTE SD/HD/3G SDI FPGA серии Xilinx для выполнения. операция декодирования видео SDI и вывод видео BT1120. На этом этапе операция декодирования видео SDI завершена, и вы можете выполнять обычные операции по обработке изображения;

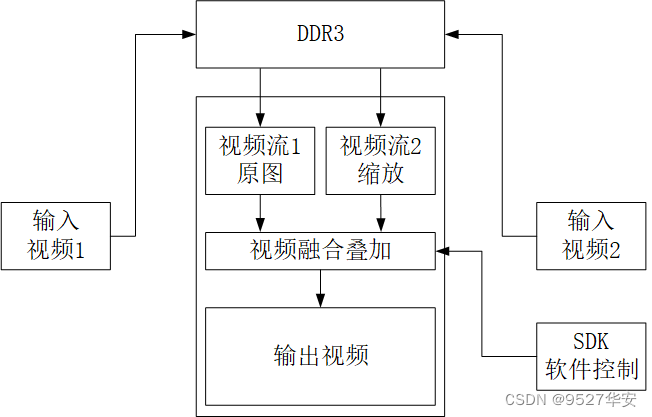

Целью этой разработки является вывод декодированного видео SDI после масштабирования изображения + объединения и наложения многоканального видео. В ответ на текущие потребности основного проекта на рынке в этом блоге разработаны два метода вывода: один — выход HDMI, а другой — выход HDMI. другой — выход 3G-SDI, оба метода требуют декодирования видео BT1120 для преобразования в RGB, а в этой конструкции используется модуль BT1120 в RGB для преобразования формата видео в официальную архитектуру кэша изображений VDMA Xilinx; реализовать кэширование и кэширование изображений. Носитель находится на стороне PS DDR3. Первое видео SDI записывается в DDR через VDMA, а затем считывается и отправляется в модуль наложения видео. Второе видео SDI не считывается после записи в DDR. через VDMA, но накладывается посредством слияния видео. Модуль считывает из DDR3. На этом этапе 2-канальное видео поступает в модуль наложения видео, а затем выполняется процесс наложения слияния, а затем оно поступает в модуль отправки HDMI; вывод HDMI-дисплея, который является методом вывода HDMI; или формат видео реализуется с помощью модуля преобразования RGB в BT1120, затем видео поступает в IP-ядро SMPTE SD/HD/3G SDI, выполняет операции кодирования видео SDI и выводит видео SDI. , а затем проходит через высокоскоростные ресурсы GTX внутри FPGA для реализации преобразования параллельных данных в высокоскоростной последовательный порт, который в этом блоге называется последовательным, дифференциальный высокоскоростной сигнал затем поступает во встроенный чип Gv8500 для реализации функций дифференциальное преобразование в несимметричный и улучшение драйвера. Видео SDI выводится через разъем BNC платы разработки FPGA и подключается к блоку SDI-HDMI через коаксиальный кабель к дисплею HDMI. Это метод вывода SDI; в этом блоге представлены 2 набора исходных кодов проектов, а именно:

Вышеупомянутые два набора исходных кодов проекта объясняются следующим образом, чтобы облегчить понимание читателям:

Исходный код проекта 1

Модель FPGA платы разработки: Xilinx–>Xilinx-Zynq7100–xc7z100ffg900-2, имеется два источника входного сигнала: один — камера 3G-SDI с разрешением 1920x1080 при 60 Гц, а другой — HDMI-3G-SDI; Коробка подключена к ноутбуку. Аналоговая SDI-камера с разрешением 1920x1080 при 60 Гц; два входных видео передаются на FPGA через два встроенных чипа Gv8601a для достижения несимметричного преобразования в дифференциальный и балансный эквалайзер; через два канала GTX видео SDI десериализуется в параллельные данные, затем проходит через 2 канала IP-ядра SMPTE SDI для декодирования SDI в 2 канала данных BT1120, затем проходит через 2 канала BT1120 в модуль RGB для преобразования BT1120 в RGB888; затем видео проходит через 2 канала официального видео входа Xilinx в IP-ядро AXI4-Stream для реализации преобразования данных RGB888 в поток данных AXI4, затем видео записывается в кэш DDR3 на стороне PS через 2-канальный официальный образ VDMA Xilinx; затем самостоятельно разработанное IP-ядро многоканального слияния и наложения видео на основе HLS реализует операцию слияния и наложения 2-канального видео. Затем введите официальное IP-ядро Xilinx AXI4-Stream To Video Out для преобразования AXI4-Stream; видеопоток в собственный видеопоток; затем отправьте видео с наложением на модуль RGB-HDMI для преобразования видео RGB888 в видео HDMI и выходного разрешения. Подробные эффекты отображения см. в демонстрационном видео вывода на странице. конец статьи; изображение наконец отображается через HDMI-дисплей; для этого проекта требуется программное ядро Zynq, подходящее для сращивания видео SDI с HDMI;

Исходный код проекта 2

Модель FPGA платы разработки: Xilinx–>Xilinx-Zynq7100–xc7z100ffg900-2, имеется два источника входного сигнала: один — камера 3G-SDI с разрешением 1920x1080 при 60 Гц, а другой — HDMI-3G-SDI; Коробка подключена к ноутбуку. Аналоговая SDI-камера с разрешением 1920x1080 при 60 Гц; два входных видео передаются на FPGA через два встроенных чипа Gv8601a для достижения несимметричного преобразования в дифференциальный и балансный эквалайзер; через два канала GTX видео SDI десериализуется в параллельные данные, затем проходит через 2 канала IP-ядра SMPTE SDI для декодирования SDI в 2 канала данных BT1120, затем проходит через 2 канала BT1120 в модуль RGB для преобразования BT1120 в RGB888; затем видео проходит через 2 канала официального видео входа Xilinx в IP-ядро AXI4-Stream для реализации преобразования данных RGB888 в поток данных AXI4, затем видео записывается в кэш DDR3 на стороне PS через 2-канальный официальный образ VDMA Xilinx; затем самостоятельно разработанное IP-ядро многоканального слияния и наложения видео на основе HLS реализует операцию слияния и наложения 2-канального видео. Затем введите официальное IP-ядро Xilinx AXI4-Stream To Video Out для преобразования AXI4-Stream; видеопоток в собственный видеопоток; затем отправить видео наложения Fusion в модуль RGB-BT1120 для преобразования видео RGB888 в видео BT1120, а затем передать IP-ядро SMPTE SD/HD/3G SDI и кодировать видео BT1120 в видео SDI; затем преобразует параллельные данные SDI в высокоскоростные последовательные сигналы через высокоскоростные ресурсы GTX внутри FPGA, а затем использует встроенный чип Gv8500 для реализации дифференциального преобразования в несимметричный и драйвер. После улучшения выходное разрешение составляет 1920x1080 при 60 Гц; наконец, блок SDI-HDMI используется для подключения к дисплею HDMI для отображения; для этого проекта требуется программное ядро Zynq, подходящее для сценариев SDI-SDI;

Этот проект и его исходный код включают в себя как части, написанные мной, так и части, полученные из общедоступных каналов в Интернете (включая CSDN, официальный сайт Xilinx, официальный сайт Altera и т. д.). Если вы считаете, что это оскорбительно, отправьте личное сообщение по адресу. критиковать и обучать, исходя из этого, этот проект. Проект и его исходный код предназначены только для личного изучения и исследования читателями или фанатами и запрещены к использованию в коммерческих целях, если в результате коммерческого использования читателями или фанатами возникают юридические вопросы. , этот блог и блоггер не имеют к нему никакого отношения, поэтому используйте его с осторожностью. . .

На домашней странице моего блога есть раздел видео SDI, в котором полно исходного кода кодеков SDI FPGA и введение в блог; есть кодеки SDI на основе GS2971/GS2972 и кодеки SDI на основе ресурсов GTP/GTX; SDI, 6G-SDI, 12G-SDI и т. д., ссылка на адрес столбца следующая:

Нажмите, чтобы перейти напрямую

В этом блоге самостоятельно разработано приложение для наложения многоканального видео. Я специально написал блог. Ссылка на адрес блога выглядит следующим образом:

Нажмите, чтобы перейти напрямую

Принципиальная блок-схема конструкции выглядит следующим образом:

Уведомление! ! ! !

Уведомление! ! ! !

Фиолетовая стрелка: выходной путь 3G-SDI.

Красная стрелка: выходной путь HDMI

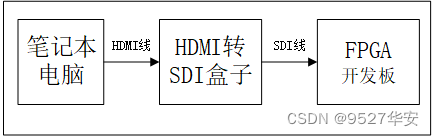

Имеется два устройства ввода SDI, которые подключаются к двустороннему интерфейсу видеовхода SDI платы разработки FPGA; одно из них представляет собой камеру 3G-SDI с разрешением 1920x1080 при 60 Гц, а также камеры SD-SDI. можно использовать из-за этой конструкции. Он адаптируется к трем типам видео SDI; еще один блок HDMI-3G-SDI, блок подключается к ноутбуку для имитации камеры SDI. Камеры SDI относительно дороги, и друзья с ограниченным бюджетом могут рассмотреть это; использование коробки HDMI-SDI для имитации камеры SDI Hezibao стоит около 100 юаней, при использовании коробки HDMI-SDI источником входного сигнала может быть ноутбук, то есть использовать ноутбук для подключения к входному интерфейсу HDMI HDMI; к блоку SDI через кабель HDMI, а затем используйте кабель SDI для подключения блока HDMI к блоку SDI. Выходной интерфейс SDI к плате разработки FPGA выглядит следующим образом:

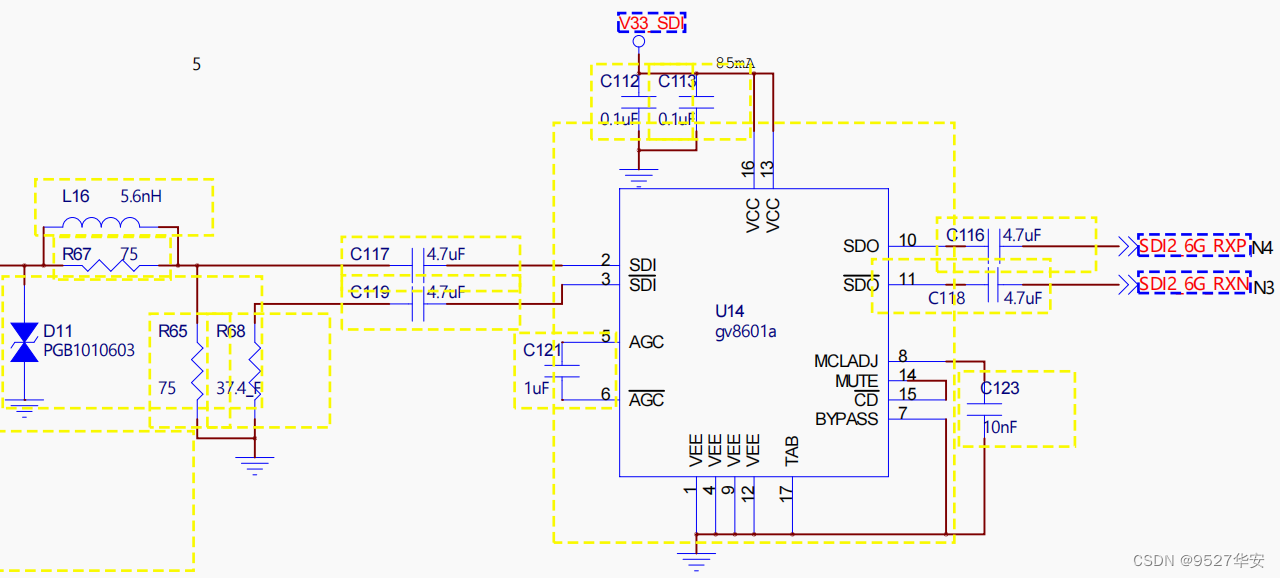

Чип Gv8601a реализует функции несимметричного преобразования в дифференциальный и балансный эквалайзер. Здесь выбран Gv8601a, поскольку он основан на официальном решении Xilinx. Конечно, можно использовать и другие типы устройств. Принципиальная схема эквалайзера Gv8601a выглядит следующим образом:

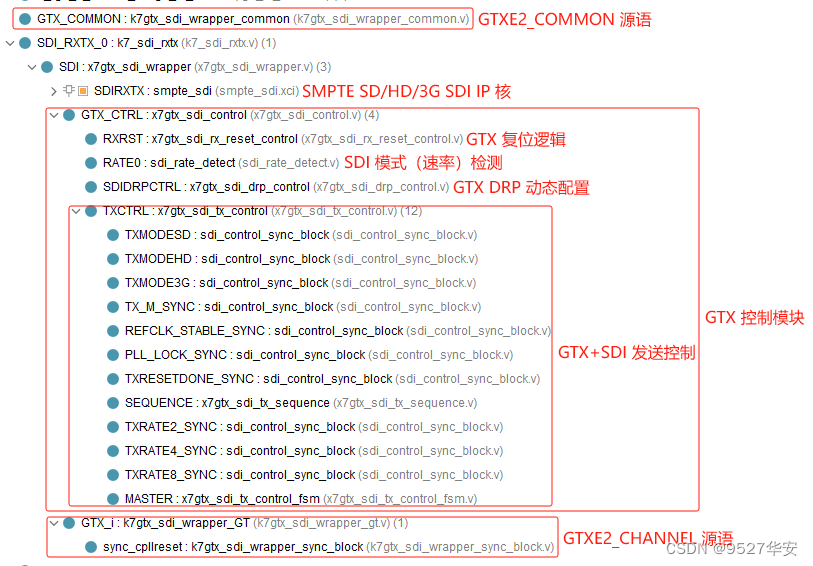

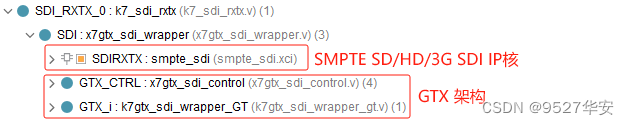

В этой конструкции используются уникальные ресурсы высокоскоростной обработки сигналов Xilinx GTX для достижения десериализации и сериализации дифференциальных видеосигналов SDI. Для приема видео SDI GTX выполняет роль десериализации, то есть декодирования входных высокоскоростных последовательных дифференциальных сигналов в параллельные цифровые. для передачи видео SDI GTX играет роль сериализации, то есть сериализации входного параллельного цифрового сигнала в высокоскоростной последовательный дифференциальный сигнал, как правило, требует создания экземпляра IP-ядра GTX посредством настройки пользовательского интерфейса vivado; интерфейс, но такая конструкция требует автоматической идентификации и адаптивной обработки видео SD-SDI, HD-SDI и 3G-SDI, поэтому GTX должна иметь функцию динамического изменения скорости линии. Эту функцию можно настроить через интерфейс DRP. Его также можно настроить через интерфейс скорости GTX, поэтому вы не можете использовать интерфейс пользовательского интерфейса vivado для настройки. Вместо этого вы можете напрямую создать экземпляры исходных языков GTXE2_CHANNEL и GTXE2_COMMON и напрямую использовать ресурсы GTX. для динамической настройки скорости линии GTX также необходим модуль управления GTX, этот модуль соответствует официальному проектному плану Xilinx и имеет функции динамического мониторинга режима SDI, динамической настройки DRP и т. д.; план относится к официальному дизайну Xilinx, структура кода модуля десериализации и сериализации GTX следующая:

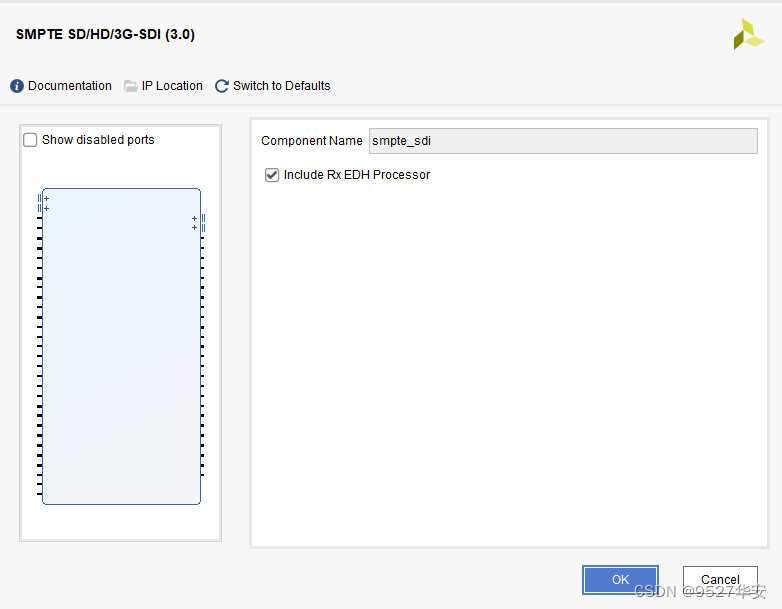

IP-ядро SMPTE SD/HD/3G SDI — это уникальный IP-адрес для кодирования и декодирования видео SDI FPGA серии Xilinx. Конфигурация IP очень проста в использовании. Интерфейс пользовательского интерфейса vivado выглядит следующим образом.

IP-ядро SMPTE SD/HD/3G SDI должно использоваться с GTX. Для приема видео SDI IP получает данные от GTX, а затем декодирует видео SDI в видеовыход BT1120. Для передачи видео SDI IP получает BT1120. видеоданные со стороны пользователя, а затем кодирует видео BT1120 в видеовыход SDI; это решение относится к официальному дизайну Xilinx, структура основного IP-кода SMPTE SD/HD/3G SDI выглядит следующим образом:

Функция модуля BT1120 в RGB заключается в преобразовании видеовыхода BT1120 с помощью IP-декодирования SMPTE SD/HD/3G SDI в видео RGB888. Он состоит из трех модулей: модуля BT1120 в CEA861, модуля YUV422 в YUV444 и модуля YUV444 в RGB888. Это решение относится к официальному дизайну Xilinx, структура кода модуля BT1120 to RGB следующая:

Решение для видеокэширования в этой конструкции использует официальную 2-канальную архитектуру кэша изображений VDMA Xilinx; носителем кэша является DDR3 на стороне PS; первое видео SDI записывается в DDR через VDMA, а затем считывается и отправляется в модуль наложения видео. Второе SDI-видео После записи в DDR через VDMA оно не считывается, а считывается из DDR3 через модуль Video Fusion Overlay. На примере исходного кода проекта 1 VDMA спроектирован с использованием Block Design компании Xilinx. вивадо, как показано ниже:

Чтобы уменьшить задержку, VDMA кэширует 1 кадр следующим образом:

Блок-схема наложения многоканального видео слияния выглядит следующим образом:

Объединение и наложение многоканального видео формируется путем объединения и наложения основного видео и наложенного видео. Базовое видео представляет собой входное видео первого канала, а наложенное видео представляет собой масштабированное видео второго канала. видео объединяются и выводятся, что может быть выполнено. Программное обеспечение SDK динамически настраивает прозрачность слияния двухканального видео, размер масштабирования наложенного видео, положение отображения наложенного видео и другую информацию. Проектирование реализуется с использованием; Код решения HLS на C++ синтезируется в RTL, а затем инкапсулируется как IP, который можно использовать в vivado. Вызов IP. Подробную информацию об этом решении можно найти в моем предыдущем блоге. Ссылка на блог выглядит следующим образом:

Нажмите, чтобы перейти напрямую

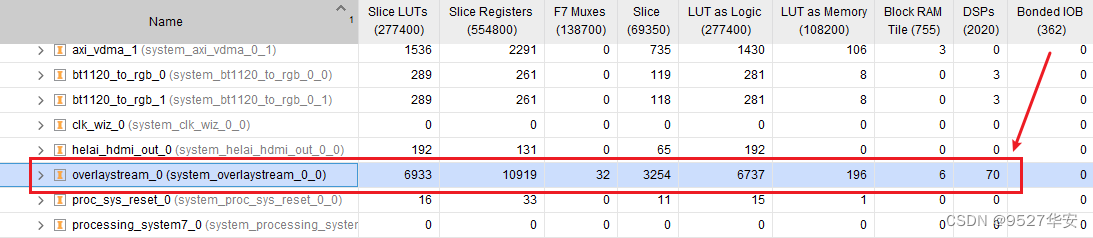

Комплексное использование ресурсов этого IP в vivado выглядит следующим образом:

Для правильной работы многоканального наложения видео HLS необходимо запустить драйвер и пользовательскую программу в SDK. Я предоставил в проекте программу на языке C, подробности см. в исходном коде проекта; Вызов наложения канала Video Fusion выглядит следующим образом:

Архитектура видеовыхода HDMI следующая:

Ссылаясь на официальный дизайн Xilinx, используйте архитектуру VTC+AXI4-Stream To Video Out для преобразования выходного видео из AXI4-Stream в собственный формат, затем используйте модуль RGB888 to HDMI, реализованный в чистом коде Verilog, для преобразования RGB888 в HDMI, и наконец, отобразите его через монитор, структура кода модуля RGB888 to HDMI выглядит следующим образом:

Что касается модуля RGB888-HDMI, обратитесь к моему предыдущему блогу по адресу:Нажмите, чтобы перейти напрямую

Архитектура вывода видео SDI должна сначала преобразовать поток AXI4, считанный VDMA, в собственный формат. После получения видео RGB888 он может затем преобразовать видео RGB в BT1120 в BT1120. Архитектура следующая:

В режиме вывода SDI тактовая частота пикселя модуля синхронизации VGA обеспечивается отправляющей пользовательской тактовой частотой IP-ядра SMPTE SD/HD/3G SDI. Тактовая частота пикселя различна в разных режимах SDI. Например, в режиме 3G-SDI. , частота пикселей составляет 148,5M. В режиме HD-SDI 720P при 60 Гц частота пикселей составляет 74,25M;

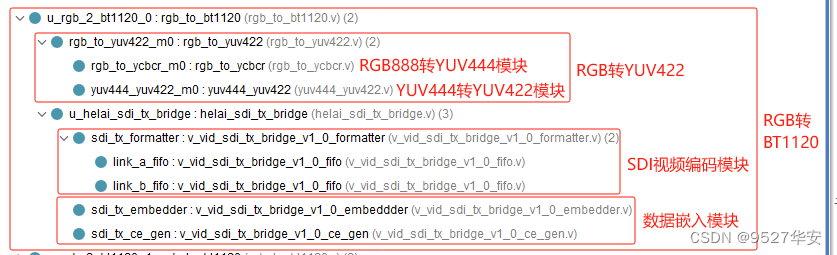

В режиме вывода SDI необходимо использовать модуль RGB to BT1120, функция которого заключается в преобразовании видео RGB на стороне пользователя в видео BT1200 и его выводе на SMPTE SD/HD/3G SDI IP; ядро модуля RGB-BT1120 состоит из модуля RGB888-YUV444, модуля YUV444-YUV422, модуля кодирования видео SDI и модуля встраивания данных. Это решение относится к официальному дизайну модуля Xilinx; следующее:

Эти две части совместно используют соответствующие модули с процессом приема, которые функционально являются процессом, обратным процессу приема, и не будут описываться снова;

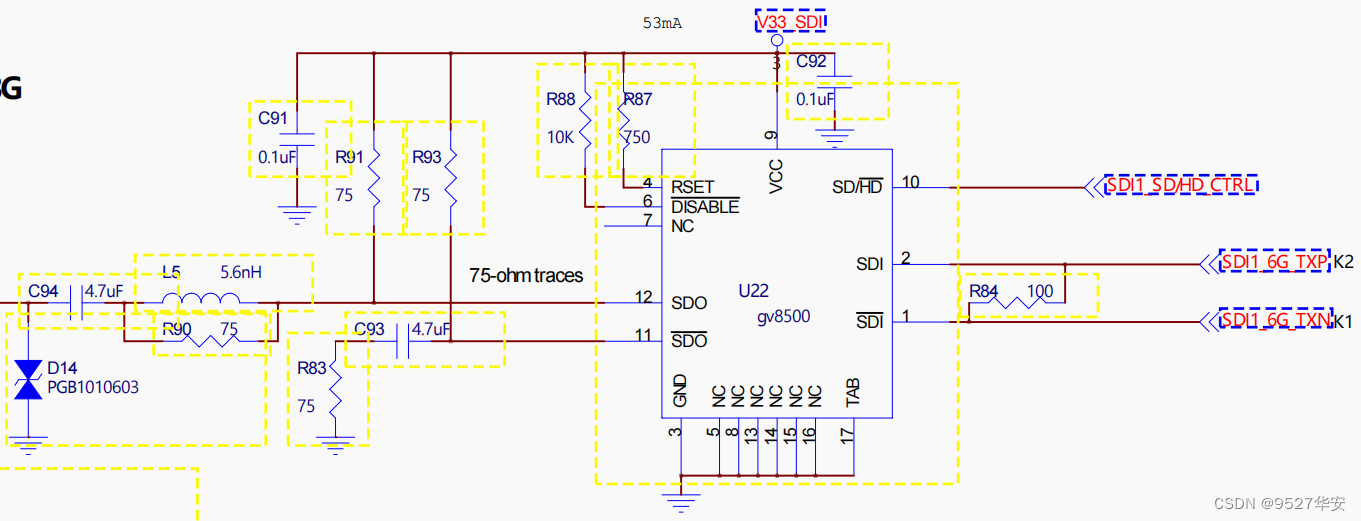

Чип Gv8500 реализует функции дифференциального преобразования в несимметричный и расширенный драйвер. Здесь выбран Gv8500, поскольку он основан на официальном решении Xilinx. Конечно, можно использовать и другие типы устройств. Принципиальная схема драйвера Gv8500 выглядит следующим образом:

В режиме вывода SDI вам необходимо использовать коробку SDI to HDMI, потому что монитор в моей руке не имеет интерфейса SDI, а только интерфейс HDMI. Для отображения видео SDI я могу сделать только это. если ваш монитор имеет интерфейс SDI, вы можете напрямую. Соединение показывает, что мой блок SDI-HDMI был куплен в определенном магазине менее чем за 100 юаней;

В этом блоге представлены 2 набора исходных кодов проекта. На примере исходного кода проекта 1 конструкция блока vivado выглядит следующим образом. Другие проекты аналогичны конструкции блочного дизайна:

Если взять в качестве примера исходный код проекта 1, структура исходного кода проекта выглядит следующим образом. Другие проекты аналогичны:

Сторонняя синхронизация PL исходного кода проекта обеспечивается программным ядром Zynq, поэтому для запуска Zynq необходимо запустить SDK. Кроме того, для правильной работы IP-ядер, таких как оверлей видео и VDMA, необходимо запустить программные драйверы. Структура программного кода SDK следующая:

Конфигурация кода SDK следующая: пользователи могут изменять ее произвольно в соответствии со своими потребностями;

Первое видео — это видео нижнего слоя с разрешением 1920x1080;

Второе видео — это наложенное видео с разрешением 1920x1080. Возьмите область 1000x800 из координат наложенного видео (400, 200) в качестве источника для наложенного видео;

Масштабируйте наложенное видео размером 600x600, полученное на предыдущем шаге, до 960x540;

Наложите наложенное совмещенное видео размером 960x540 на предыдущем шаге, начиная с координаты (0,0) базового видео, и установите прозрачность нижележащего и наложенного слоев на 80;

Модель макетной платы FPGA: Xilinx-Zynq7100–xc7z100ffg900-2;

Среда разработки: Vivado2019.1;

Вход: камера 3G-SDI или блок HDMI-SDI, разрешение 1920x1080 при 60 Гц;

Выход: HDMI, разрешение 1920x1080, 60 Гц;

Решение для кэширования: официальное решение VDMA Xilinx;

Носитель кэша: сторона PS DDR3;

Решение для слияния и наложения видео: собственная разработка многоканального слияния и наложения видео на основе HLS;

Роль проекта: Цель этого проекта — предоставить читателям возможность освоить возможности проектирования FPGA серии Zynq для реализации SDI в HDMI, чтобы они могли переносить и разрабатывать свои собственные проекты;

Информацию о блочном проектировании проекта и архитектуре кода проекта см. в разделе «Архитектура исходного кода проекта» в главе 3;

Потребление ресурсов и энергопотребление проекта следующие:

Модель макетной платы FPGA: Xilinx-Zynq7100–xc7z100ffg900-2;

Среда разработки: Vivado2019.1;

Вход: камера 3G-SDI или блок HDMI-SDI, разрешение 1920x1080 при 60 Гц;

Выход: 3G-SDI, разрешение 1920x1080, 60 Гц;

Решение для кэширования: официальное решение VDMA Xilinx;

Носитель кэша: сторона PS DDR3;

Решение для слияния и наложения видео: собственная разработка многоканального слияния и наложения видео на основе HLS;

Роль проекта: Цель этого проекта — предоставить читателям возможность освоить возможности проектирования FPGA серии Zynq для реализации SDI в HDMI, чтобы они могли переносить и разрабатывать свои собственные проекты;

Информацию о блочном проектировании проекта и архитектуре кода проекта см. в разделе «Архитектура исходного кода проекта» в главе 3;

Потребление ресурсов и энергопотребление проекта следующие:

1: Если ваша версия vivado соответствует версии vivado этого проекта, откройте проект напрямую;

2: Если ваша версия vivado ниже версии vivado этого проекта, вам нужно открыть проект и нажать «Файл» -> «Сохранить как», однако этот метод небезопасен. Самый безопасный способ — обновить версию vivado до vivado. этого проекта или выше;

3: Если ваша версия vivado выше версии vivado этого проекта, решение следующее:

Открыв проект, вы обнаружите, что IP-адреса заблокированы следующим образом:

На данный момент вам необходимо обновить IP. Шаги следующие:

Если ваша модель FPGA не соответствует моей, вам необходимо изменить модель FPGA следующим образом:

После изменения модели ПЛИС необходимо обновить ИП. Способ обновления ИП был описан ранее;

1: Поскольку DDR каждой платы не обязательно одинаков, IP-адрес MIG необходимо настроить в соответствии с вашей собственной принципиальной схемой. Вы даже можете напрямую удалить MIG моего исходного проекта здесь, повторно добавить IP и перенастроить его. ;

2. Измените ограничения выводов в соответствии с вашей собственной принципиальной схемой и измените их в файле xdc;

3. Пересадка чистой FPGA в Zynq требует добавления программного ядра Zynq в проект;

Оборудование, которое необходимо подготовить, следующее:

плата разработки ПЛИС;

SDI-камера или коробка HDMI-SDI;

коробка SDI-HDMI;

HDMI-дисплей;

Моя плата разработки подключена следующим образом:

Если взять в качестве примера исходный код проекта 1, то результат будет следующим:

Наложение Zynq-SDI-Video Fusion

Бонус: Получение инженерного кода

Код слишком велик и не может быть отправлен по электронной почте. Он будет отправлен по ссылке на определенный сетевой диск.

Как получить информацию: лично или по визитке V в конце статьи.

Информация о сетевом диске следующая:

Кроме того, многие друзья высказали этому блоггеру множество мнений и предложений, надеясь расширить содержание и возможности услуг. Поскольку у разных друзей разные потребности, этот блоггер также предоставляет следующие услуги: