τα στοιχεία επικοινωνίας μου

Ταχυδρομείο[email protected]

2024-07-12

한어Русский языкEnglishFrançaisIndonesianSanskrit日本語DeutschPortuguêsΕλληνικάespañolItalianoSuomalainenLatina

Επί του παρόντος, υπάρχουν δύο λύσεις για την εφαρμογή κωδικοποίησης και αποκωδικοποίησης βίντεο SDI: η μία είναι η χρήση αποκλειστικών τσιπ κωδικοποίησης και αποκωδικοποίησης, όπως ο τυπικός δέκτης GS2972, και ο πομπός GS2972. Το πλεονέκτημα είναι, για παράδειγμα, ο δέκτης GS2971 Αποκωδικοποιεί το SDI σε παράλληλο YCrCb422 και το GS2972 κωδικοποιεί απευθείας το YCrCb422 σε βίντεο SDI Το μειονέκτημα είναι ότι το κόστος είναι σχετικά υψηλό Το λογικό τμήμα πόρων FPGA για την υλοποίηση κωδικοποίησης και αποκωδικοποίησης SDI και χρήση των πόρων GTP/GTX της σειράς FPGA για να επιτύχετε την αποσεισμοποίηση, χρησιμοποιήστε τους πόρους SMPTE SDI της σειράς FPGA για την εφαρμογή κωδικοποίησης και αποκωδικοποίησης SDI Οι πόροι χρησιμοποιούνται λογικά και οι πόροι GTP/GTX δεν χρησιμοποιούνται μάταια. Το μειονέκτημα είναι ότι η λειτουργία είναι πιο δύσκολη και απαιτεί υψηλότερο τεχνικό επίπεδο προγραμματιστών. Είναι ενδιαφέρον ότι αυτές οι δύο λύσεις έχουν αντίστοιχες λύσεις εδώ σε αυτό το ιστολόγιο, συμπεριλαμβανομένων των πλακών ανάπτυξης υλικού FPGA, του πηγαίου κώδικα μηχανικής κ.λπ.

Αυτός ο σχεδιασμός βασίζεται στην πλακέτα ανάπτυξης Zynq7100 FPGA της σειράς Zynq για την εφαρμογή κωδικοποίησης και αποκωδικοποίησης βίντεο SDI + κλιμάκωση εικόνας + σύνδεση βίντεο πολλαπλών καναλιών Υπάρχουν δύο πηγές εισόδου, η μία είναι μια κάμερα 3G-SDI με ανάλυση 1920x1080@. 60Hz και HD-SDI μπορούν επίσης να χρησιμοποιηθούν ή κάμερα SD-SDI, επειδή αυτή η σχεδίαση προσαρμόζεται σε ένα άλλο κουτί HDMI σε 3G-SDI Τα βίντεο SDI συνδέονται με την πλακέτα ανάπτυξης FPGA μέσω ομοαξονικών καλωδίων υποδοχής BNC και, στη συνέχεια, το ομοαξονικό βίντεο περνά μέσα από το ενσωματωμένο τσιπ Gv8601a για να πραγματοποιήσει τις λειτουργίες της μετατροπής ενός άκρου σε διαφορικό και ισορροπημένο EQ, και στη συνέχεια το διαφορικό σήμα βίντεο SDI εισέρχεται στο GTX Υψηλής ταχύτητας πόρος μέσα στο FPGA για την πραγματοποίηση της υψηλής ταχύτητας σειριακής σε παράλληλη μετατροπή των δεδομένων Bo το αποκαλεί deserialization στη συνέχεια αποστέλλεται στον μοναδικό πυρήνα SMPTE SD/HD/3G SDI της FPGA της σειράς Xilinx. Λειτουργία αποκωδικοποίησης βίντεο και έξοδος βίντεο BT1120 Σε αυτό το σημείο, η λειτουργία αποκωδικοποίησης βίντεο SDI έχει ολοκληρωθεί και μπορείτε να εκτελέσετε εργασίες ρουτίνας επεξεργασίας εικόνας.

Ο σκοπός αυτής της σχεδίασης είναι η έξοδος αποκωδικοποιημένου βίντεο SDI μετά από κλιμάκωση εικόνας + πολυκαναλική σύντηξη και υπέρθεση Σε απάντηση στις τρέχουσες ανάγκες του βασικού έργου στην αγορά, αυτό το ιστολόγιο έχει σχεδιάσει δύο μεθόδους εξόδου, η μία είναι η έξοδος HDMI και η Η άλλη είναι η έξοδος 3G -SDI, και οι δύο μέθοδοι απαιτούν την αποκωδικοποίηση βίντεο BT1120 για μετατροπή σε κρυφή μνήμη και αυτό το σχέδιο χρησιμοποιεί τη μονάδα BT1120 σε RGB για να επιτύχει τη μετατροπή μορφής βίντεο της επίσημης αρχιτεκτονικής κρυφής μνήμης Xilinx Εφαρμογή αποθήκευσης και αποθήκευσης στην κρυφή μνήμη εικόνας Το μέσο είναι ενσωματωμένο στο DDR3 από την πλευρά του PS μέσω VDMA, αλλά επικαλύπτεται μέσω της σύντηξης βίντεο Η μονάδα διαβάζεται από το DDR3 οθόνη, η οποία είναι η μέθοδος εξόδου HDMI ή η μορφή βίντεο πραγματοποιείται μέσω της μετατροπής μονάδας RGB σε BT1120, στη συνέχεια το βίντεο εισέρχεται στον πυρήνα IP SMPTE SD/HD/3G, εκτελεί λειτουργίες κωδικοποίησης βίντεο SDI και εξάγει βίντεο SDI και στη συνέχεια εξάγει βίντεο SDI. περνά μέσα από τους πόρους υψηλής ταχύτητας GTX μέσα στο FPGA για να πραγματοποιήσει τη μετατροπή των παράλληλων δεδομένων σε σειριακή υψηλής ταχύτητας, την οποία αυτό το ιστολόγιο αποκαλεί σειριακή, το διαφορικό σήμα υψηλής ταχύτητας εισέρχεται στη συνέχεια στο ενσωματωμένο τσιπ Gv8500 για να πραγματοποιήσει τις λειτουργίες της διαφορικής μετατροπής σε Βελτίωση ενός άκρου και προγράμματος οδήγησης Το βίντεο SDI εξάγεται μέσω της υποδοχής BNC της πλακέτας ανάπτυξης FPGA και συνδέεται με το κουτί SDI σε HDMI μέσω ενός ομοαξονικού καλωδίου στην οθόνη HDMI 2 σετ πηγαίων κωδίκων έργου, ως εξής:

Τα παραπάνω δύο σύνολα πηγαίων κωδίκων έργου εξηγούνται ως εξής για να διευκολυνθεί η κατανόηση των αναγνωστών:

Πηγαίος κώδικας έργου 1

Το μοντέλο FPGA της πλακέτας ανάπτυξης είναι Xilinx–>Xilinx-Zynq7100–xc7z100ffg900-2, υπάρχουν δύο πηγές εισόδου, η μία είναι κάμερα 3G-SDI με ανάλυση 1920x1080@60Hz και η άλλη είναι μια κάμερα HDMI έως 3G-S. Το κουτί είναι συνδεδεμένο με μια αναλογική κάμερα SDI με ανάλυση 1920x1080@60Hz, τα δύο βίντεο εισόδου αποστέλλονται στο FPGA μέσω των δύο ενσωματωμένων τσιπών για την επίτευξη μετατροπής ενός άκρου σε διαφορικό και στη συνέχεια Μέσω των δύο καναλιών GTX, το βίντεο SDI αποσυντονίζεται σε παράλληλα δεδομένα. Στη συνέχεια, περάστε από 2 κανάλια SMPTE SDI IP για να αποκωδικοποιήσετε το SDI σε 2 κανάλια δεδομένων BT1120 και μετά να μετατρέψετε το BT1120 σε RGB888. Στη συνέχεια, περάστε από 2 κανάλια του επίσημου πυρήνα βίντεο του Xilinx σε AXI4-Stream για να πραγματοποιήσετε μετατροπή δεδομένων RGB888 σε ροή δεδομένων AXI4-Stream, στη συνέχεια, το βίντεο εγγράφεται στην κρυφή μνήμη DDR3 της πλευράς PS μέσω της επίσημης εικόνας VDMA Xilinx. Στη συνέχεια, ο πυρήνας σύντηξης βίντεο πολλαπλών καναλιών που έχει αναπτυχθεί μόνος του με βάση το HLS υλοποιεί τη λειτουργία σύντηξης και επικάλυψης βίντεο 2 καναλιών . Μετάδοση βίντεο στη ροή του εγγενούς βίντεο, στη συνέχεια, στείλτε το βίντεο επικάλυψης fusion στη μονάδα RGB σε HDMI για να μετατρέψετε το βίντεο RGB888 σε βίντεο HDMI και η ανάλυση εξόδου είναι 1920x1080@60Hz Τέλος του άρθρου, η εικόνα εμφανίζεται τελικά μέσω μιας οθόνης HDMI.

Πηγαίος κώδικας έργου 2

Το μοντέλο FPGA της πλακέτας ανάπτυξης είναι Xilinx–>Xilinx-Zynq7100–xc7z100ffg900-2, υπάρχουν δύο πηγές εισόδου, η μία είναι κάμερα 3G-SDI με ανάλυση 1920x1080@60Hz και η άλλη είναι μια κάμερα HDMI έως 3G-S. Το κουτί είναι συνδεδεμένο με μια αναλογική κάμερα SDI με ανάλυση 1920x1080@60Hz, τα δύο βίντεο εισόδου αποστέλλονται στο FPGA μέσω των δύο ενσωματωμένων τσιπών για την επίτευξη μετατροπής ενός άκρου σε διαφορικό και στη συνέχεια Μέσω των δύο καναλιών GTX, το βίντεο SDI αποσυντονίζεται σε παράλληλα δεδομένα. Στη συνέχεια, περάστε από 2 κανάλια SMPTE SDI IP για να αποκωδικοποιήσετε το SDI σε 2 κανάλια δεδομένων BT1120 και μετά να μετατρέψετε το BT1120 σε RGB888. Στη συνέχεια, περάστε από 2 κανάλια του επίσημου πυρήνα βίντεο του Xilinx σε AXI4-Stream για να πραγματοποιήσετε μετατροπή δεδομένων RGB888 σε ροή δεδομένων AXI4-Stream, στη συνέχεια, το βίντεο εγγράφεται στην κρυφή μνήμη DDR3 της πλευράς PS μέσω της επίσημης εικόνας VDMA Xilinx. Στη συνέχεια, ο πυρήνας σύντηξης βίντεο πολλαπλών καναλιών που έχει αναπτυχθεί μόνος του με βάση το HLS υλοποιεί τη λειτουργία σύντηξης και επικάλυψης βίντεο 2 καναλιών . Στη συνέχεια, στείλτε το βίντεο επικάλυψης fusion στη μονάδα RGB σε BT1120 για να μετατρέψετε το βίντεο RGB888 σε βίντεο BT1120 μετατρέπει τα παράλληλα δεδομένα SDI σε σειριακά σήματα υψηλής ταχύτητας μέσω των πόρων υψηλής ταχύτητας GTX στο εσωτερικό του FPGA και στη συνέχεια χρησιμοποιεί το ενσωματωμένο τσιπ Gv8500 για να υλοποιήσει τη διαφορική μετατροπή σε ένα άκρο και πρόγραμμα οδήγησης , ένα κουτί SDI σε HDMI χρησιμοποιείται για να συνδεθεί σε μια οθόνη HDMI για προβολή, αυτό το έργο απαιτεί την εκτέλεση του μαλακού πυρήνα Zynq, κατάλληλο για σενάρια SDI σε SDI.

Αυτό το έργο και ο πηγαίος κώδικάς του περιλαμβάνουν τμήματα που έχουν γραφτεί από εμένα και μέρη που λαμβάνονται από δημόσια κανάλια στο Διαδίκτυο (συμπεριλαμβανομένου του CSDN, του επίσημου ιστότοπου Xilinx, του επίσημου ιστότοπου της Altera, κ.λπ. Εάν πιστεύετε ότι είναι προσβλητικό, στείλτε ένα ιδιωτικό μήνυμα στο κριτική και εκπαίδευση με βάση αυτό, αυτό το έργο και ο πηγαίος κώδικας του είναι μόνο για προσωπική μελέτη και έρευνα από αναγνώστες ή θαυμαστές και απαγορεύεται να χρησιμοποιούνται για εμπορικούς σκοπούς , αυτό το ιστολόγιο και ο blogger δεν έχουν καμία σχέση με αυτό, γι' αυτό χρησιμοποιήστε το με προσοχή. . .

Η αρχική σελίδα του ιστολογίου μου έχει μια στήλη βίντεο SDI, η οποία είναι γεμάτη από τον πηγαίο κώδικα μηχανικής του κωδικοποιητή FPGA και την εισαγωγή του ιστολογίου. SDI, 6G-SDI, 12G-SDI, κ.λπ., ο σύνδεσμος διεύθυνσης στήλης είναι ο εξής:

Κάντε κλικ για να μεταβείτε απευθείας

Αυτό το ιστολόγιο έχει δημιουργήσει μια εφαρμογή επικάλυψης πολλαπλών καναλιών. Έχω γράψει ειδικά ένα ιστολόγιο στο παρελθόν.

Κάντε κλικ για να μεταβείτε απευθείας

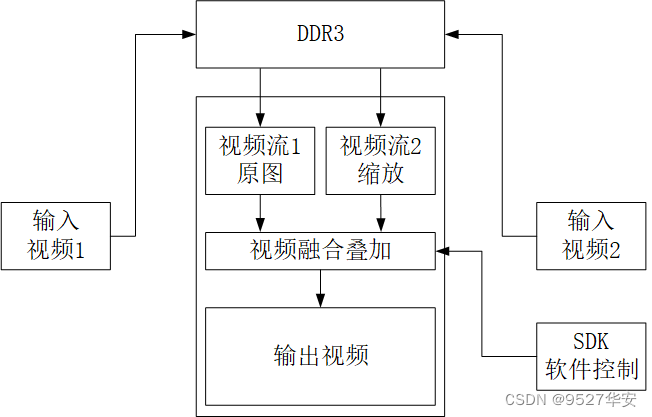

Το μπλοκ διάγραμμα της αρχής σχεδιασμού είναι το εξής:

Ειδοποίηση! ! ! !

Ειδοποίηση! ! ! !

Μωβ βέλος: Διαδρομή εξόδου 3G-SDI

Κόκκινο βέλος: Διαδρομή εξόδου HDMI

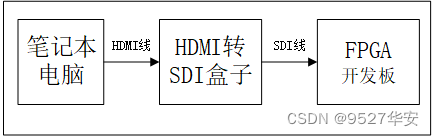

Υπάρχουν δύο συσκευές εισόδου SDI, οι οποίες συνδέονται με τη διεπαφή εισόδου βίντεο SDI της πλακέτας ανάπτυξης FPGA, η μία είναι κάμερα 3G-SDI με ανάλυση 1920x1080@60Hz να χρησιμοποιηθεί λόγω αυτού του σχεδιασμού Είναι προσαρμοσμένο σε τρεις τύπους βίντεο SDI, ένα άλλο κουτί HDMI σε 3G-SDI, το κουτί είναι συνδεδεμένο με φορητό υπολογιστή για την προσομοίωση μιας κάμερας SDI, και οι φίλοι με περιορισμένο προϋπολογισμό μπορούν Εξετάστε το ενδεχόμενο να χρησιμοποιήσετε ένα κουτί HDMI σε SDI για την προσομοίωση μιας κάμερας SDI κοστίζει περίπου 100 γιουάν όταν χρησιμοποιείτε ένα κουτί HDMI σε SDI, η πηγή εισόδου μπορεί να είναι ένας φορητός υπολογιστής, δηλαδή, να χρησιμοποιήσετε έναν φορητό υπολογιστή για να συνδεθείτε στη διεπαφή εισόδου HDMI. HDMI σε κουτί SDI μέσω καλωδίου HDMI και, στη συνέχεια, χρησιμοποιήστε ένα καλώδιο SDI για να συνδέσετε το κουτί HDMI σε SDI Η διεπαφή εξόδου SDI στην πλακέτα ανάπτυξης FPGA είναι η εξής:

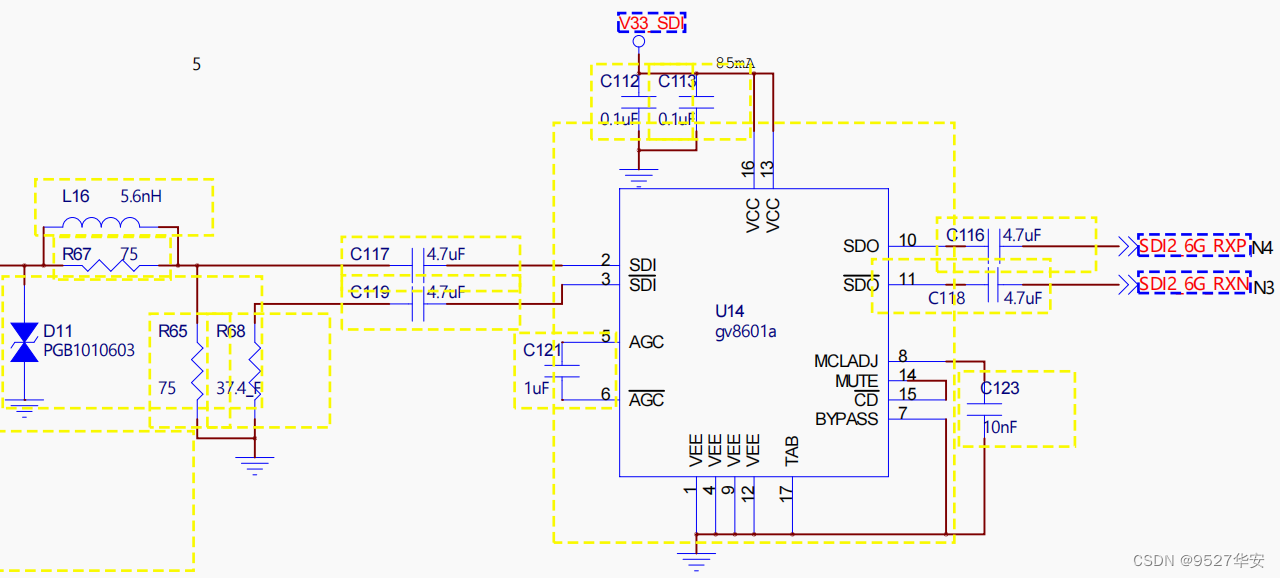

Το τσιπ Gv8601a πραγματοποιεί τις λειτουργίες της μετατροπής ενός άκρου σε διαφορικό και ισορροπημένο EQ Το Gv8601a επιλέγεται εδώ επειδή βασίζεται στην επίσημη λύση Xilinx. Το σχηματικό διάγραμμα του ισοσταθμιστή Gv8601a έχει ως εξής:

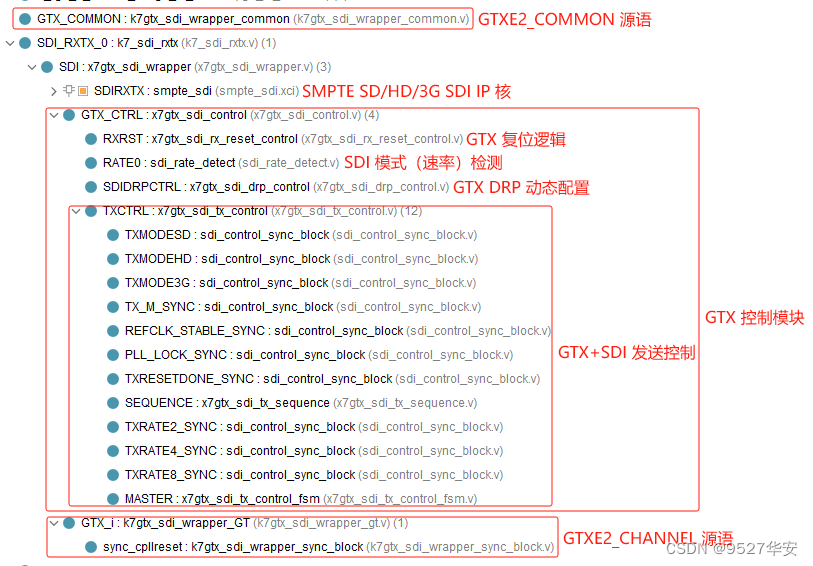

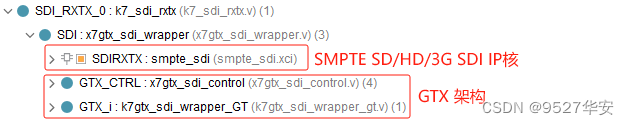

Αυτός ο σχεδιασμός χρησιμοποιεί τους μοναδικούς πόρους επεξεργασίας σήματος υψηλής ταχύτητας GTX της Xilinx για την επίτευξη αποσειριοποίησης και σειριοποίησης των διαφορικών σημάτων βίντεο SDI, το GTX παίζει το ρόλο της αποσειριοποίησης, δηλαδή την αποκωδικοποίηση των σειριακών διαφορικών σημάτων εισόδου σε παράλληλη ψηφιακή. για τη μετάδοση βίντεο SDI, το GTX παίζει το ρόλο της σειριοποίησης, δηλαδή τη σειριοποίηση του παράλληλου ψηφιακού σήματος σε ένα σειριακό διαφορικό σήμα υψηλής ταχύτητας, η χρήση του GTX γενικά απαιτεί την εγκατάσταση του πυρήνα GTX, μέσω του vivado Configure the UI. διεπαφή, αλλά αυτός ο σχεδιασμός απαιτεί αυτόματη αναγνώριση και προσαρμοστική επεξεργασία των βίντεο SD-SDI, HD-SDI και 3G-SDI, επομένως το GTX πρέπει να έχει τη λειτουργία δυναμικής αλλαγής του ρυθμού γραμμής Αυτή η λειτουργία μπορεί να διαμορφωθεί μέσω της διεπαφής DRP. Μπορεί επίσης να διαμορφωθεί μέσω της διεπαφής ρυθμού του GTX, επομένως δεν μπορείτε να χρησιμοποιήσετε τη διεπαφή διεπαφής του vivado, αντ' αυτού, μπορείτε να δημιουργήσετε απευθείας τις γλώσσες πηγής GTXE2_CHANNEL και να χρησιμοποιήσετε απευθείας τους πόρους GTX. Για να διαμορφώσετε δυναμικά τον ρυθμό γραμμής GTX, χρειάζεστε επίσης μια μονάδα ελέγχου GTX, αυτή η ενότητα αναφέρεται στο επίσημο σχέδιο σχεδίασης του Xilinx και έχει τις λειτουργίες δυναμικής παρακολούθησης της λειτουργίας SDI, δυναμικής διαμόρφωσης του DRP, κ.λπ Το σχέδιο αναφέρεται στον επίσημο σχεδιασμό του Xilinx, η δομή του κώδικα της ενότητας αποσειροποίησης και σειριοποίησης GTX είναι η εξής:

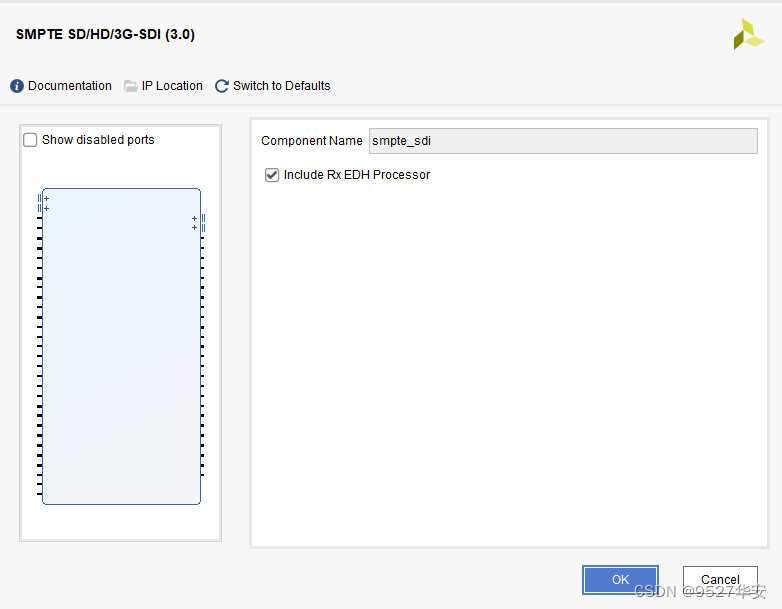

Ο πυρήνας SMPTE SD/HD/3G SDI IP είναι μια μοναδική IP για κωδικοποίηση και αποκωδικοποίηση βίντεο της σειράς Xilinx. Η διαμόρφωση IP είναι πολύ απλή στη χρήση.

Ο πυρήνας SMPTE SD/HD/3G SDI IP πρέπει να χρησιμοποιείται με GTX Για λήψη βίντεο SDI, η IP λαμβάνει δεδομένα από το GTX και στη συνέχεια αποκωδικοποιεί το βίντεο SDI σε έξοδο βίντεο BT1120 δεδομένα βίντεο από την πλευρά του χρήστη και, στη συνέχεια, κωδικοποιεί το βίντεο BT1120 στην έξοδο βίντεο SDI.

Η λειτουργία της μονάδας BT1120 σε RGB είναι να μετατρέπει την έξοδο βίντεο BT1120 με αποκωδικοποίηση πυρήνα IP SMPTE SD/HD/3G σε βίντεο RGB888. Αποτελείται από τρεις μονάδες: μονάδα BT1120 σε CEA861, μονάδα YUV422 σε YUV444 και μονάδα RUV844. Αυτή η λύση αναφέρεται στο Ο επίσημος σχεδιασμός Xilinx έχει υιοθετηθεί η δομή του κώδικα της μονάδας BT1120 σε RGB

Η λύση κρυφής μνήμης βίντεο αυτού του σχεδίου υιοθετεί την επίσημη αρχιτεκτονική κρυφής μνήμης εικόνας VDMA 2 καναλιών, το μέσο κρυφής μνήμης είναι PS-side DDR3. Το δεύτερο βίντεο SDI Αφού εγγραφεί σε DDR μέσω VDMA, δεν διαβάζεται από το DDR3 μέσω της ενότητας επικάλυψης σύντηξης βίντεο Λαμβάνοντας ως παράδειγμα τον πηγαίο κώδικα του έργου, το VDMA έχει σχεδιαστεί χρησιμοποιώντας το Block Design του Xilinx vivado, όπως φαίνεται παρακάτω:

Προκειμένου να μειωθεί η καθυστέρηση, το VDMA έχει ρυθμιστεί σε προσωρινή μνήμη 1 καρέ, ως εξής:

Το μπλοκ διάγραμμα σχεδίασης επικάλυψης σύντηξης βίντεο πολλαπλών καναλιών έχει ως εξής:

Η συγχώνευση και η επικάλυψη βίντεο πολλαπλών καναλιών σχηματίζονται από τη συγχώνευση και την υπέρθεση του υποκείμενου βίντεο και του βίντεο επικάλυψης Τα βίντεο συγχωνεύονται και εξάγονται, το οποίο μπορεί να είναι Το λογισμικό SDK διαμορφώνει δυναμικά τη διαφάνεια της σύντηξης βίντεο 2 καναλιών, το μέγεθος ζουμ του βίντεο επικάλυψης, τη θέση εμφάνισης του βίντεο επικάλυψης και άλλες πληροφορίες Ο κώδικας της λύσης HLS συντίθεται σε RTL και ενσωματώνεται σε IP, το οποίο μπορεί να χρησιμοποιηθεί στο vivado Καλέστε την IP Για λεπτομέρειες σχετικά με αυτήν τη λύση, ανατρέξτε στο προηγούμενο ιστολόγιο μου.

Κάντε κλικ για να μεταβείτε απευθείας

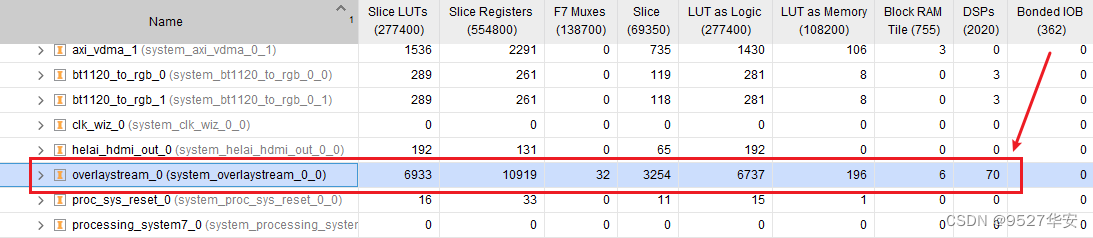

Η πλήρης χρήση πόρων αυτής της IP στο vivado είναι η εξής:

Η επικάλυψη πολυκαναλικής σύντηξης βίντεο HLS πρέπει να εκτελέσει το πρόγραμμα οδήγησης και το πρόγραμμα χρήστη στο SDK για να λειτουργήσει σωστά. Έχω παράσχει ένα πρόγραμμα στη γλώσσα C στο έργο. Η κλήση επικάλυψης σύντηξης βίντεο καναλιού έχει ως εξής:

Η αρχιτεκτονική εξόδου βίντεο HDMI είναι η εξής:

Αναφερόμενοι στην επίσημη σχεδίαση της Xilinx, χρησιμοποιήστε την αρχιτεκτονική VTC+AXI4-Stream To Video Out για να μετατρέψετε το βίντεο εξόδου από AXI4-Stream σε Native, στη συνέχεια χρησιμοποιήστε τη μονάδα RGB888 σε HDMI που έχει υλοποιηθεί σε καθαρό κώδικα verilog για να μετατρέψετε το RGB888 σε HDMI. μέσω της οθόνης , η δομή κώδικα της μονάδας RGB888 σε HDMI είναι η εξής:

Όσον αφορά τη μονάδα RGB888 σε HDMI, ανατρέξτε στο προηγούμενο ιστολόγιό μου, διεύθυνση ιστολογίου:Κάντε κλικ για να μεταβείτε απευθείας

Η αρχιτεκτονική εξόδου βίντεο SDI πρέπει πρώτα να μετατρέψει το AXI4-Stream που διαβάζεται από το VDMA σε εγγενή μορφή Μετά τη λήψη του βίντεο RGB888, μπορεί να μετατρέψει το βίντεο RGB σε BT1120.

Στη λειτουργία εξόδου SDI, το ρολόι εικονοστοιχείων της μονάδας χρονισμού VGA παρέχεται από το ρολόι του χρήστη αποστολής του πυρήνα IP SMPTE SD/HD/3G Το ρολόι εικονοστοιχείων είναι διαφορετικό σε διαφορετικές λειτουργίες SDI , το ρολόι pixel είναι 148,5M Σε λειτουργία HD-SDI 720P@60Hz, το ρολόι pixel είναι 74,25M.

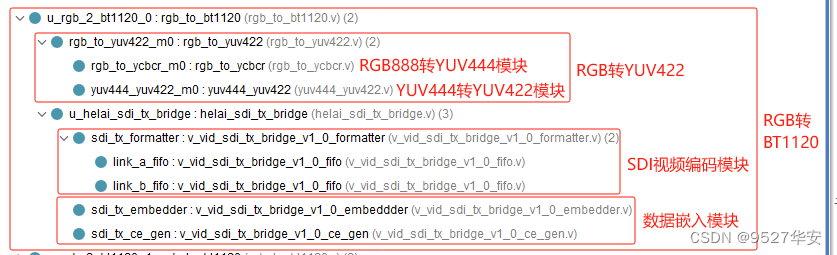

Στη λειτουργία εξόδου SDI, πρέπει να χρησιμοποιηθεί η μονάδα RGB σε BT1200, η λειτουργία της μονάδας RGB σε BT1200 είναι να μετατρέπει το βίντεο RGB από την πλευρά του χρήστη σε βίντεο BT1200 και να το εξάγει στο SMPTE SD/HD/3G SDI IP. Η μονάδα πυρήνα RGB σε BT1120 αποτελείται από μια μονάδα RGB888 έως YUV444, μονάδα κωδικοποίησης βίντεο SDI και μονάδα ενσωμάτωσης δεδομένων Αυτή η λύση αναφέρεται στον επίσημο σχεδιασμό της μονάδας BT1120 ως εξής:

Αυτά τα δύο μέρη μοιράζονται τις αντίστοιχες ενότητες με τη διαδικασία λήψης, οι οποίες λειτουργικά είναι η αντίστροφη διαδικασία της διαδικασίας λήψης και δεν θα περιγραφούν ξανά.

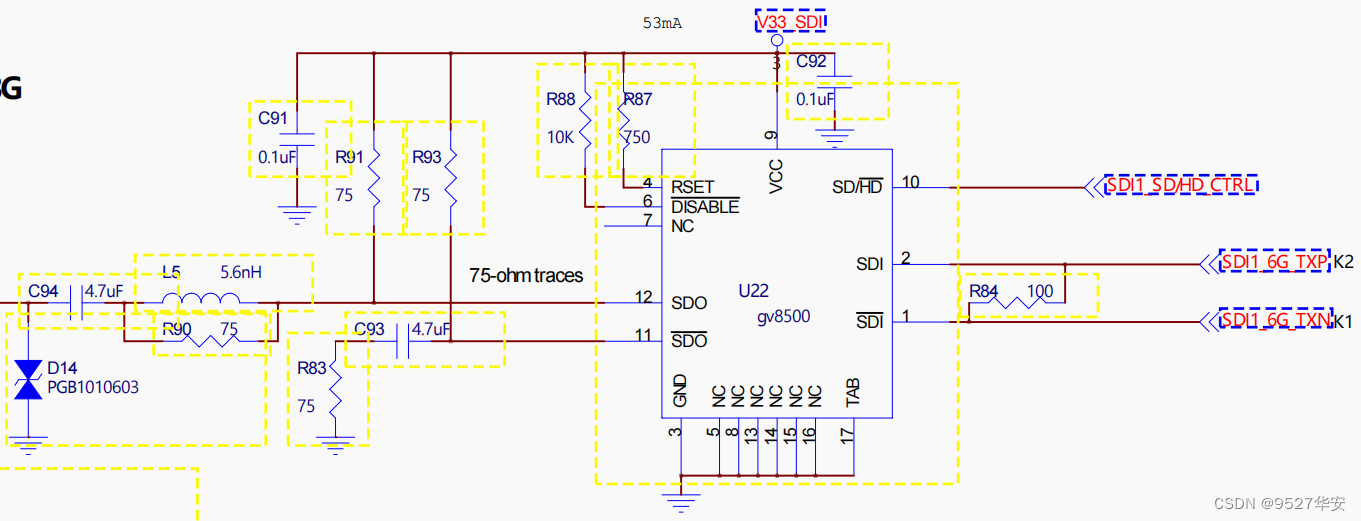

Το τσιπ Gv8500 πραγματοποιεί τις λειτουργίες της διαφορικής μετατροπής σε μονόπλευρο και βελτιωμένο πρόγραμμα οδήγησης Το Gv8500 επιλέγεται εδώ επειδή βασίζεται στην επίσημη λύση Xilinx. Το σχηματικό διάγραμμα του προγράμματος οδήγησης Gv8500 έχει ως εξής:

Στη λειτουργία εξόδου SDI, πρέπει να χρησιμοποιήσετε ένα κουτί SDI σε HDMI, επειδή η οθόνη στο χέρι μου δεν έχει διασύνδεση SDI, μόνο διασύνδεση HDMI, φυσικά, αυτό μπορεί να γίνει Η οθόνη σας έχει διεπαφή SDI, μπορείτε απευθείας Η σύνδεση δείχνει ότι το κουτί μου SDI σε HDMI αγοράστηκε σε ένα συγκεκριμένο κατάστημα για λιγότερο από 100 γιουάν.

Αυτό το ιστολόγιο παρέχει 2 σετ πηγαίων κωδίκων έργου Λαμβάνοντας ως παράδειγμα τον πηγαίο κώδικα του έργου, ο σχεδιασμός του vivado Block είναι ο εξής.

Λαμβάνοντας ως παράδειγμα τον πηγαίο κώδικα του έργου, η δομή του πηγαίου κώδικα του έργου είναι η εξής.

Το πλευρικό ρολόι του πηγαίου κώδικα του έργου παρέχεται από τον μαλακό πυρήνα του Zynq, επομένως το SDK πρέπει να εκτελεστεί για να ξεκινήσει το Zynq Η δομή του κώδικα λογισμικού SDK έχει ως εξής:

Η διαμόρφωση στον κώδικα SDK έχει ως εξής, οι χρήστες μπορούν να τον τροποποιήσουν αυθαίρετα σύμφωνα με τις δικές τους ανάγκες.

Το πρώτο βίντεο είναι το βίντεο στο κάτω επίπεδο με ανάλυση 1920x1080.

Το βίντεο του δεύτερου καναλιού είναι το βίντεο επικάλυψης με ανάλυση 1920x1080 Πάρτε μια περιοχή 1000x800 από τις συντεταγμένες βίντεο επικάλυψης (400, 200) ως αρχή ως το βίντεο σύντηξης επικάλυψης.

Κλιμακώστε το βίντεο σύντηξης επικάλυψης 600x600 που ελήφθη στο προηγούμενο βήμα σε 960x540.

Επικαλύψτε το υπερτιθέμενο βίντεο σύντηξης 960x540 στο προηγούμενο βήμα ξεκινώντας από τη συντεταγμένη (0,0) του υποκείμενου βίντεο και ορίστε τη διαφάνεια των υποκείμενων επιπέδων και των επιπέδων επικάλυψης στο 80.

Μοντέλο FPGA πλακέτας ανάπτυξης: Xilinx-Zynq7100–xc7z100ffg900-2;

Περιβάλλον ανάπτυξης: Vivado2019.1;

Είσοδος: Κάμερα 3G-SDI ή κουτί HDMI σε SDI, ανάλυση 1920x1080@60Hz.

Έξοδος: HDMI, ανάλυση 1920x1080@60Hz;

Λύση προσωρινής αποθήκευσης: Επίσημη λύση VDMA της Xilinx.

Μέσα προσωρινής μνήμης: PS πλευρά DDR3.

Λύση σύντηξης και επικάλυψης βίντεο: πολυκαναλική σύντηξη και επικάλυψη βίντεο με βάση το HLS.

Ρόλος έργου: Ο σκοπός αυτού του έργου είναι να επιτρέψει στους αναγνώστες να κατακτήσουν τις δυνατότητες σχεδιασμού της σειράς Zynq FPGA για την εφαρμογή SDI σε HDMI, ώστε να μπορούν να μεταμοσχεύουν και να σχεδιάζουν τα δικά τους έργα.

Για τη σχεδίαση μπλοκ έργου και την αρχιτεκτονική του κώδικα έργου, ανατρέξτε στην ενότητα "Αρχιτεκτονική πηγαίου κώδικα έργου" στο Κεφάλαιο 3.

Η κατανάλωση πόρων και η κατανάλωση ενέργειας του έργου έχουν ως εξής:

Μοντέλο FPGA πλακέτας ανάπτυξης: Xilinx-Zynq7100–xc7z100ffg900-2;

Περιβάλλον ανάπτυξης: Vivado2019.1;

Είσοδος: Κάμερα 3G-SDI ή κουτί HDMI σε SDI, ανάλυση 1920x1080@60Hz.

Έξοδος: 3G-SDI, ανάλυση 1920x1080@60Hz;

Λύση προσωρινής αποθήκευσης: Επίσημη λύση VDMA της Xilinx.

Μέσα προσωρινής μνήμης: PS πλευρά DDR3.

Λύση σύντηξης και επικάλυψης βίντεο: πολυκαναλική σύντηξη και επικάλυψη βίντεο με βάση το HLS.

Ρόλος έργου: Ο σκοπός αυτού του έργου είναι να επιτρέψει στους αναγνώστες να κατακτήσουν τις δυνατότητες σχεδιασμού της σειράς Zynq FPGA για την εφαρμογή SDI σε HDMI, ώστε να μπορούν να μεταμοσχεύουν και να σχεδιάζουν τα δικά τους έργα.

Για τη σχεδίαση μπλοκ έργου και την αρχιτεκτονική του κώδικα έργου, ανατρέξτε στην ενότητα "Αρχιτεκτονική πηγαίου κώδικα έργου" στο Κεφάλαιο 3.

Η κατανάλωση πόρων και η κατανάλωση ενέργειας του έργου έχουν ως εξής:

1: Εάν η έκδοση του vivado είναι συμβατή με την έκδοση vivado αυτού του έργου, ανοίξτε το έργο απευθείας.

2: Εάν η έκδοση vivado είναι χαμηλότερη από την έκδοση vivado αυτού του έργου, πρέπει να ανοίξετε το έργο και να κάνετε κλικ στο Αρχείο –> Αποθήκευση ως, ωστόσο, αυτή η μέθοδος δεν είναι ασφαλής αυτού του έργου ή νεότερη έκδοση.

3: Εάν η έκδοση vivado είναι υψηλότερη από την έκδοση vivado αυτού του έργου, η λύση είναι η εξής:

Μετά το άνοιγμα του έργου, θα διαπιστώσετε ότι οι IP είναι κλειδωμένες, ως εξής:

Αυτή τη στιγμή, πρέπει να αναβαθμίσετε την IP Τα βήματα είναι τα εξής:

Εάν το μοντέλο FPGA δεν συνάδει με το δικό μου, πρέπει να αλλάξετε το μοντέλο FPGA ως εξής:

Αφού αλλάξετε το μοντέλο FPGA, πρέπει να αναβαθμίσετε την IP Η μέθοδος αναβάθμισης της IP έχει περιγραφεί προηγουμένως.

1: Εφόσον το DDR κάθε πλακέτας δεν είναι απαραίτητα ακριβώς το ίδιο, η MIG IP πρέπει να ρυθμιστεί σύμφωνα με το δικό σας σχηματικό διάγραμμα.

2: Τροποποιήστε τους περιορισμούς pin σύμφωνα με το δικό σας σχηματικό διάγραμμα και τροποποιήστε το στο αρχείο xdc.

3: Η μεταφύτευση καθαρού FPGA σε Zynq απαιτεί την προσθήκη μαλακού πυρήνα zynq στο έργο.

Ο εξοπλισμός που πρέπει να προετοιμαστεί είναι ο εξής:

Πίνακας ανάπτυξης FPGA?

Κάμερα SDI ή κουτί HDMI σε SDI.

SDI σε κουτί HDMI.

Οθόνη HDMI;

Η πλακέτα ανάπτυξης μου συνδέεται ως εξής:

Λαμβάνοντας ως παράδειγμα τον πηγαίο κώδικα 1 του έργου, η έξοδος είναι η εξής:

Επικάλυψη Zynq-SDI-Video Fusion

Μπόνους: Απόκτηση μηχανικού κώδικα

Ο κωδικός είναι πολύ μεγάλος και δεν μπορεί να σταλεί με email Θα σταλεί μέσω συγκεκριμένου συνδέσμου δίσκου δικτύου.

Πώς να αποκτήσετε πληροφορίες: ιδιωτικά ή την επαγγελματική κάρτα V στο τέλος του άρθρου.

Οι πληροφορίες του δίσκου δικτύου είναι οι εξής:

Επιπλέον, πολλοί φίλοι έχουν δώσει σε αυτόν τον blogger πολλές απόψεις και προτάσεις, ελπίζοντας να εμπλουτίσουν το περιεχόμενο και τις επιλογές της υπηρεσίας Επειδή διαφορετικοί φίλοι έχουν διαφορετικές ανάγκες, αυτός ο blogger παρέχει επίσης τις ακόλουθες υπηρεσίες: