2024-07-12

한어Русский языкEnglishFrançaisIndonesianSanskrit日本語DeutschPortuguêsΕλληνικάespañolItalianoSuomalainenLatina

सम्प्रति, FPGA कृते SDI विडियो एन्कोडिंग् तथा डिकोडिंग् कार्यान्वितुं द्वौ समाधानौ स्तः: एकं समर्पितानां एन्कोडिंग् तथा डिकोडिंग् चिप्स् इत्यस्य उपयोगः, यथा विशिष्टः रिसीवरः GS2972, तथा च ट्रांसमीटर् GS2972 इत्यस्य लाभः उदाहरणार्थं, GS2971 रिसीवरः प्रत्यक्षतया अस्ति SDI इत्यस्य समानान्तर YCrCb422 इत्यस्य decodes, and the GS2972 transmits उपकरणं प्रत्यक्षतया समानान्तर YCrCb422 इत्यस्य SDI विडियो मध्ये एन्कोडं करोति FPGA तर्कसंसाधनविभागः SDI एन्कोडिंग् तथा डिकोडिंग् कार्यान्वितुं तथा Xilinx श्रृङ्खला FPGA इत्यस्य GTP/GTX संसाधनानाम् उपयोगं कर्तुं, Xilinx श्रृङ्खला FPGA इत्यस्य SMPTE SDI संसाधनानाम् उपयोगं कृत्वा SDI एन्कोडिंग् तथा डिकोडिंग् कार्यान्वितुं शक्नोति संसाधनानाम् उपयोगः यथोचितरूपेण भवति तथा च GTP/GTX संसाधनानाम् उपयोगः व्यर्थं न भवति । रोचकं तत् अस्ति यत् एतयोः समाधानयोः अत्र अस्मिन् ब्लोग् मध्ये तदनुरूपं समाधानं भवति, यत्र हार्डवेयर FPGA विकासफलकाः, अभियांत्रिकी स्रोतसङ्केतः इत्यादयः सन्ति ।

इदं डिजाइनं Zynq श्रृङ्खलायाः Zynq7100 FPGA विकासबोर्डस्य आधारेण अस्ति यत् SDI विडियो एन्कोडिंग् तथा डिकोडिंग् + इमेज स्केलिंग् + बहु-चैनल विडियो स्प्लिसिंग् कार्यान्वितं भवति, अत्र द्वौ इनपुट् स्रोतौ स्तः, एकः 1920x1080@ रिजोल्यूशनयुक्तः 3G-SDI कैमरा अस्ति । 60Hz SDI विडियो समाक्षीयकेबल BNC सॉकेटस्य माध्यमेन FPGA विकासबोर्डेन सह सम्बद्धाः भवन्ति, ततः समाक्षीयविडियो ऑनबोर्ड Gv8601a चिप् मार्गेण गच्छति यत् एकल-अन्तरूपान्तरणस्य कार्याणि विभेदक-संतुलित-EQ मध्ये साकारं करोति ततः विभेदक-SDI-वीडियो-संकेतः GTX-मध्ये प्रवेशं करोति FPGA इत्यस्य अन्तः उच्चगतिसंसाधनं आँकडानां समानान्तररूपान्तरणं साकारं कर्तुं Bo तत् deserialization इति कथयति ततः Xilinx श्रृङ्खला FPGA इत्यस्य अद्वितीय SMPTE SD/HD/3G SDI IP कोरं प्रति प्रेष्यते video decoding operation and output BT1120 video अस्मिन् बिन्दौ, SDI video decoding ऑपरेशनं सम्पन्नम् अस्ति तथा च भवान् नियमितं इमेज प्रोसेसिंग ऑपरेशनं कर्तुं शक्नोति;

अस्य डिजाइनस्य उद्देश्यं इमेज स्केलिंग् + बहु-चैनल-वीडियो-संलयनस्य अनन्तरं डिकोडेड् SDI-वीडियो-निर्गमः अस्ति तथा च मार्केट्-मध्ये वर्तमान-मुख्यधारा-प्रकल्पस्य आवश्यकतानां प्रतिक्रियारूपेण अस्मिन् ब्लोग्-इत्यनेन द्वौ आउटपुट्-विधौ डिजाइनं कृतौ, एकः HDMI-आउटपुट् अपरः च 3G -SDI आउटपुट् अस्ति, द्वयोः पद्धतयोः RGB मध्ये परिवर्तयितुं BT1120 विडियो डिकोडिंग् आवश्यकं भवति तथा च इमेज कैशिंग् ऑपरेशन्स् इत्येतत् डिजाइनं विडियो प्रारूपरूपान्तरणं प्राप्तुं BT1120 तः RGB मॉड्यूलस्य उपयोगं करोति इमेज कैशिंग् तथा कैशिंग् माध्यमं PS-पक्षीयं DDR3 मध्ये अस्ति प्रथमः SDI विडियो VDMA मार्गेण DDR मध्ये लिखितः भवति ततः पठितः भवति तथा च विडियो फ्यूजन ओवरले मॉड्यूल् प्रति प्रेषितः भवति द्वितीयः SDI विडियो DDR मध्ये लिखितस्य अनन्तरं न पठ्यते VDMA, परन्तु विडियो फ्यूजनस्य माध्यमेन ओवरलेड् भवति , यत् HDMI आउटपुट विधिः अस्ति; through the GTX high-speed resources inside the FPGA to realise the conversion of parallel data to high-speed serial, which this blog calls serial , विभेदक उच्च-गतिसंकेतः ततः एकलरूपेण विभेदकरूपान्तरणस्य कार्याणि साकारयितुं onboard Gv8500 चिप् प्रविशति -समाप्तः तथा चालकवर्धनम् SDI विडियो FPGA विकासबोर्डस्य BNC सॉकेटद्वारा आउटपुट् भवति, तथा च HDMI प्रदर्शने समाक्षीयकेबलद्वारा SDI to HDMI box इत्यनेन सह सम्बद्धः भवति परियोजनास्रोतसङ्केतानां समुच्चयः, यथा निम्नलिखितम् ।

पाठकानां अवगमनस्य सुविधायै परियोजनास्रोतसङ्केतानां उपर्युक्तौ द्वौ समुच्चयौ निम्नलिखितरूपेण व्याख्याताः सन्ति ।

परियोजना स्रोतसङ्केतः 1

विकासफलकस्य FPGA मॉडल् Xilinx–>Xilinx-Zynq7100–xc7z100ffg900-2 अस्ति, एकः 3G-SDI कैमरा अस्ति यस्य रिजोल्यूशनः 1920x1080@60Hz अस्ति, अपरः च HDMI तः 3G-SDI यावत् अस्ति box., पेटी 1920x1080@60Hz रिजोल्यूशनयुक्तेन एनालॉग् SDI कॅमेरा सह सम्बद्धा भवति, ततः एकल-अन्तरूपान्तरणं प्राप्तुं Gv8601a चिप्-द्वयस्य माध्यमेन FPGA प्रति प्रेष्यते द्वयोः GTX चैनलयोः माध्यमेन, SDI विडियो समानान्तरदत्तांशरूपेण विक्रमितः भवति;ततः SMPTE SDI IP कोरस्य 2 चैनलेषु, SDI BT1120 आँकडानां 2 चैनलेषु डिकोडः भवति ततः BT1120 इत्यस्य 2 चैनलेषु RGB मॉड्यूले परिवर्तितः भवति; RGB888 विडियो मध्ये;ततः Xilinx आधिकारिक Video In To AXI4-Stream IP कोरं RGB888 डेटा साकारं कर्तुं ततः 2-चैनल Xilinx आधिकारिक VDMA माध्यमेन PS पक्ष DDR3 कैश मध्ये विडियो लिखतु; ततः HLS आधारितं स्वविकसितं बहु-चैनल-वीडियो-संलयनं तथा ओवरले-IP कोरं 2-चैनल-वीडियो-संलयनं तथा ओवरले-सञ्चालनं कार्यान्वितं करोति ततः AXI4- परिवर्तयितुं Xilinx आधिकारिकं AXI4-Stream To Video Out IP कोरं प्रविशतु ; स्ट्रीम विडियो स्ट्रीम to the Native video stream;ततः RGB888 विडियो HDMI विडियो मध्ये परिवर्तयितुं फ्यूजन ओवरले विडियो प्रेषयन्तु तथा च आउटपुट् रिजोल्यूशनं विस्तृतं प्रदर्शनप्रभावार्थं कृपया आउटपुट् प्रदर्शनं विडियो पश्यन्तु लेखस्य अन्ते चित्रं HDMI प्रदर्शनस्य माध्यमेन प्रदर्शितं भवति;

परियोजना स्रोतसङ्केतः 2

विकासफलकस्य FPGA मॉडल् Xilinx–>Xilinx-Zynq7100–xc7z100ffg900-2 अस्ति, एकः 3G-SDI कैमरा अस्ति यस्य रिजोल्यूशनः 1920x1080@60Hz अस्ति, अपरः च HDMI तः 3G-SDI यावत् अस्ति box., पेटी 1920x1080@60Hz रिजोल्यूशनयुक्तेन एनालॉग् SDI कॅमेरा सह सम्बद्धा भवति, ततः एकल-अन्तरूपान्तरणं प्राप्तुं Gv8601a चिप्-द्वयस्य माध्यमेन FPGA प्रति प्रेष्यते द्वयोः GTX चैनलयोः माध्यमेन, SDI विडियो समानान्तरदत्तांशरूपेण विक्रमितः भवति;ततः SMPTE SDI IP कोरस्य 2 चैनलेषु, SDI BT1120 आँकडानां 2 चैनलेषु डिकोडः भवति ततः BT1120 इत्यस्य 2 चैनलेषु RGB मॉड्यूले परिवर्तितः भवति; RGB888 विडियो मध्ये;ततः Xilinx आधिकारिक Video In To AXI4-Stream IP कोरं RGB888 डेटा साकारं कर्तुं ततः 2-चैनल Xilinx आधिकारिक VDMA माध्यमेन PS पक्ष DDR3 कैश मध्ये विडियो लिखतु; ततः HLS आधारितं स्वविकसितं बहु-चैनल-वीडियो-संलयनं तथा ओवरले-IP कोरं 2-चैनल-वीडियो-संलयनं तथा ओवरले-सञ्चालनं कार्यान्वितं करोति ततः AXI4- परिवर्तयितुं Xilinx आधिकारिकं AXI4-Stream To Video Out IP कोरं प्रविशतु ; ततः RGB888 विडियो BT1120 विडियो मध्ये परिवर्तयितुं फ्यूजन ओवरले विडियो प्रेषयन्तु; ततः FPGA इत्यस्य अन्तः GTX उच्चगतिसंसाधनानाम् माध्यमेन SDI समानान्तरदत्तांशं उच्चगति-सीरियल-संकेतेषु परिवर्तयति तथा च एकल-समाप्तं तथा चालकं प्रति विभेदकरूपान्तरणं कार्यान्वितुं onboard Gv8500 चिप् इत्यस्य उपयोगं करोति वर्धनानन्तरं, आउटपुट् रिजोल्यूशन 1920x1080@60Hz भवति अन्ते, प्रदर्शनार्थं HDMI प्रदर्शनेन सह सम्बद्धं कर्तुं SDI तः HDMI बॉक्सस्य उपयोगः भवति;

अस्मिन् परियोजनायां तस्य स्रोतसङ्केते च मया लिखिताः भागाः अपि च अन्तर्जालस्य सार्वजनिकचैनेलात् प्राप्ताः भागाः (CSDN, Xilinx आधिकारिकजालस्थलम्, Altera आधिकारिकजालस्थलम् इत्यादयः सन्ति यदि भवान् इदं आक्षेपार्हं मन्यते तर्हि कृपया निजसन्देशं प्रेषयतु)। अस्य आधारेण एतस्याः परियोजनायाः आलोचनां शिक्षितुं च परियोजना तस्याः स्रोतसङ्केतः च केवलं पाठकैः वा प्रशंसकैः वा व्यक्तिगत-अध्ययनार्थं शोधार्थं च भवति, तथा च यदि पाठकानां वा प्रशंसकानां वा व्यावसायिक-उपयोगात् कानूनी-समस्याः उत्पद्यन्ते तर्हि तस्य उपयोगः निषिद्धः अस्ति , अस्य ब्लोग् इत्यस्य ब्लोगरस्य च तया सह किमपि सम्बन्धः नास्ति, अतः कृपया सावधानीपूर्वकं तस्य उपयोगं कुर्वन्तु। . .

मम ब्लॉगस्य मुखपृष्ठे एकः SDI विडियो स्तम्भः अस्ति, यः FPGA कोडेकः SDI अभियांत्रिकी स्रोतः कोडः अस्ति तथा च GS2971/GS2972 इत्यस्य आधारेण SDI कोडेक्स् सन्ति, तथा च GTP/GTX संसाधनानाम् आधारेण SDI कोडेक्स् सन्ति; SDI, 6G-SDI, 12G-SDI इत्यादयः स्तम्भपतेः लिङ्कः निम्नलिखितरूपेण अस्ति;

प्रत्यक्षतया गन्तुं क्लिक् कुर्वन्तु

अस्मिन् ब्लोग् इत्यनेन बहुचैनल-वीडियो-संलयन-ओवरले-अनुप्रयोगः स्वयमेव विकसितः अस्ति, मया पूर्वं विशेषतया ब्लॉग् लिखितः अस्ति ।

प्रत्यक्षतया गन्तुं क्लिक् कुर्वन्तु

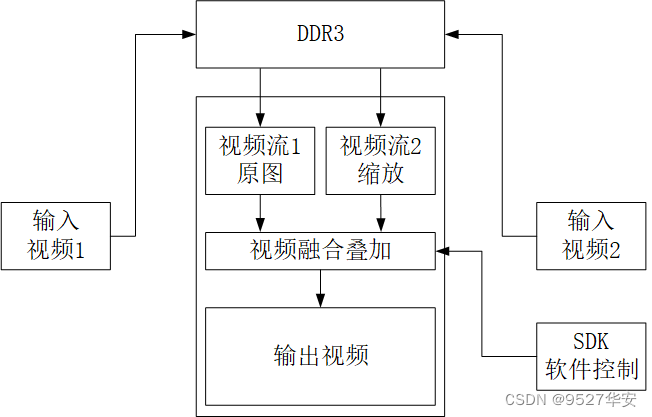

डिजाइनसिद्धान्तखण्डचित्रं निम्नलिखितम् अस्ति ।

सूचना! ! ! !

सूचना! ! ! !

बैंगनी बाण: 3G-SDI आउटपुट मार्ग

लाल बाणः HDMI निर्गममार्गः

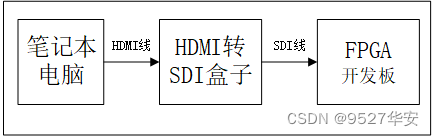

तत्र द्वौ SDI इनपुट् उपकरणौ स्तः, ये FPGA विकास बोर्डस्य 2-मार्गीय SDI विडियो इनपुट् अन्तरफलकेन सह सम्बद्धाः सन्ति;एकः 1920x1080@60Hz रिजोल्यूशनयुक्तः 3G-SDI कैमरा अपि अस्ति be used because of this design इदं त्रयः प्रकाराः SDI विडियो अनुकूलः अस्ति, अन्यः HDMI तः 3G-SDI पेटी, पेटी SDI कॅमेरा अनुकरणार्थं लैपटॉपेन सह सम्बद्धा भवति SDI कैमरा तुल्यकालिकरूपेण महत् भवति, सीमितबजटयुक्ताः मित्राणि च शक्नुवन्ति SDI कॅमेरा अनुकरणार्थं HDMI to SDI box इत्यस्य उपयोगं विचारयन्तु Hezibao इत्यस्य मूल्यं HDMI to SDI box इत्यस्य उपयोगः भवति तदा इनपुट् स्रोतः लैपटॉपः भवितुम् अर्हति, अर्थात्, इत्यस्य HDMI इनपुट् इन्टरफेस् इत्यनेन सह सम्बद्धं कर्तुं लैपटॉपस्य उपयोगः भवति HDMI to SDI box HDMI केबलद्वारा, ततः HDMI to SDI box सम्बद्धं कर्तुं SDI केबलस्य उपयोगं कुर्वन्तु FPGA विकासबोर्डेन सह SDI आउटपुट् अन्तरफलकं निम्नलिखितम् अस्ति:

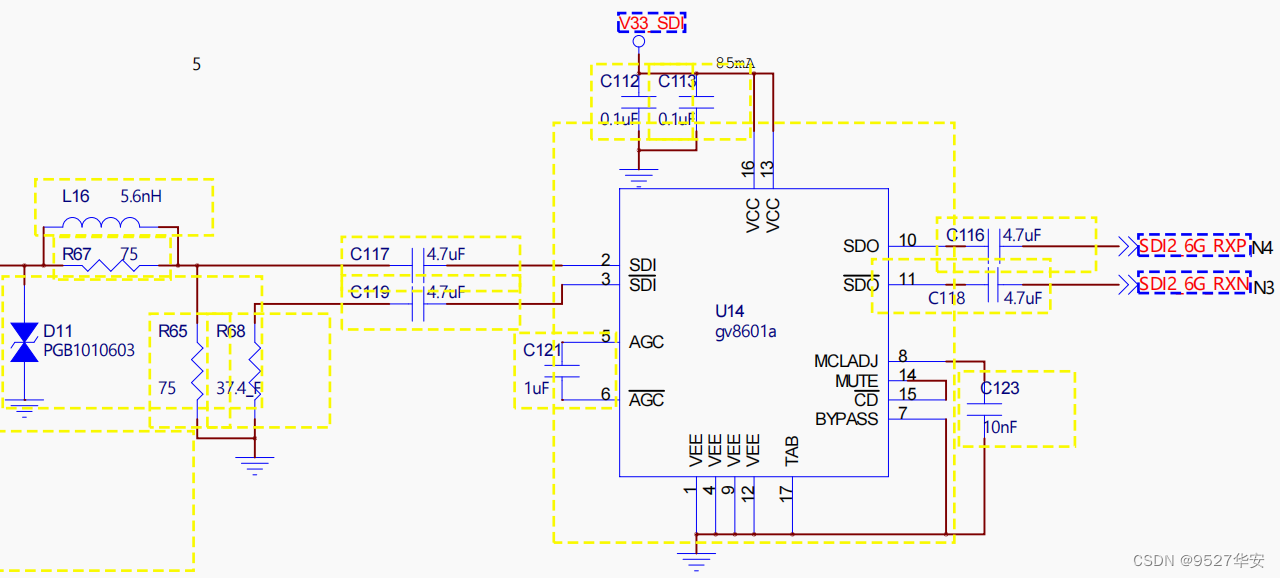

Gv8601a चिप् एकल-अन्त-रूपान्तरणस्य कार्याणि विभेदक-संतुलित-EQ प्रति साक्षात्करोति Gv8601a अत्र चयनितम् अस्ति यतोहि एतत् आधिकारिकं Xilinx समाधानं आकर्षयति अवश्यं, अन्यप्रकारस्य उपकरणानां उपयोगः अपि कर्तुं शक्यते Gv8601a समीकरणस्य योजनाबद्धचित्रं निम्नलिखितम् अस्ति ।

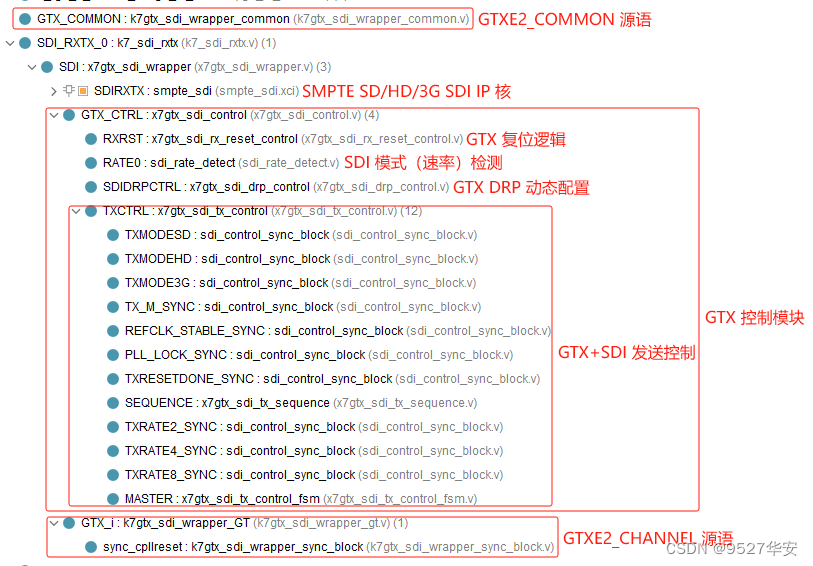

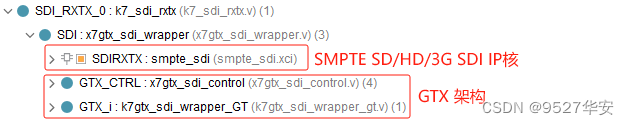

इदं डिजाइनं Xilinx इत्यस्य अद्वितीयं GTX उच्च-गति-संकेत-संसाधन-संसाधनानाम् उपयोगं करोति यत् SDI-विभेदक-वीडियो-संकेतानां वि-क्रमाङ्कनं तथा क्रमाङ्कनं प्राप्तुं शक्नोति, GTX-विक्रमीकरणस्य भूमिकां निर्वहति, अर्थात् निवेश-उच्च-गति-विभेदक-संकेतानां समानान्तर-डिजिटल-रूपेण विकोडयति signal; अन्तरफलकं, परन्तु अस्मिन् डिजाइने SD-SDI, HD-SDI, तथा 3G-SDI विडियोषु स्वचालितपरिचयस्य अनुकूलप्रक्रियाकरणस्य च आवश्यकता वर्तते, अतः GTX इत्यस्य रेखादरं गतिशीलरूपेण परिवर्तयितुं कार्यं भवितुं आवश्यकम् अस्ति एतत् कार्यं DRP अन्तरफलकस्य माध्यमेन विन्यस्तुं शक्यते इदं GTX इत्यस्य दर-अन्तरफलकस्य माध्यमेन अपि विन्यस्तं कर्तुं शक्यते, अतः भवान् विन्यासार्थं vivado इत्यस्य UI अन्तरफलकस्य उपयोगं कर्तुं न शक्नोति तस्य स्थाने, भवान् प्रत्यक्षतया GTX इत्यस्य GTXE2_CHANNEL तथा GTXE2_COMMON स्रोतभाषाणां उदाहरणं कर्तुं शक्नोति तथा च GTX संसाधनानाम् उपयोगं प्रत्यक्षतया कर्तुं शक्नोति GTX रेखादरं गतिशीलरूपेण विन्यस्तं कर्तुं, भवन्तः GTX नियन्त्रणमॉड्यूलस्य अपि आवश्यकतां अनुभवन्ति , एतत् मॉड्यूल् Xilinx इत्यस्य आधिकारिकं डिजाइनयोजनां निर्दिशति, तथा च SDI मोडस्य गतिशीलनिरीक्षणस्य कार्याणि सन्ति, DRP इत्यस्य गतिशीलविन्यासः इत्यादीनां कार्याणि सन्ति योजना Xilinx इत्यस्य आधिकारिकं डिजाइनं निर्दिशति GTX deserialization and serialization module इत्यस्य कोडसंरचना निम्नलिखितरूपेण अस्ति;

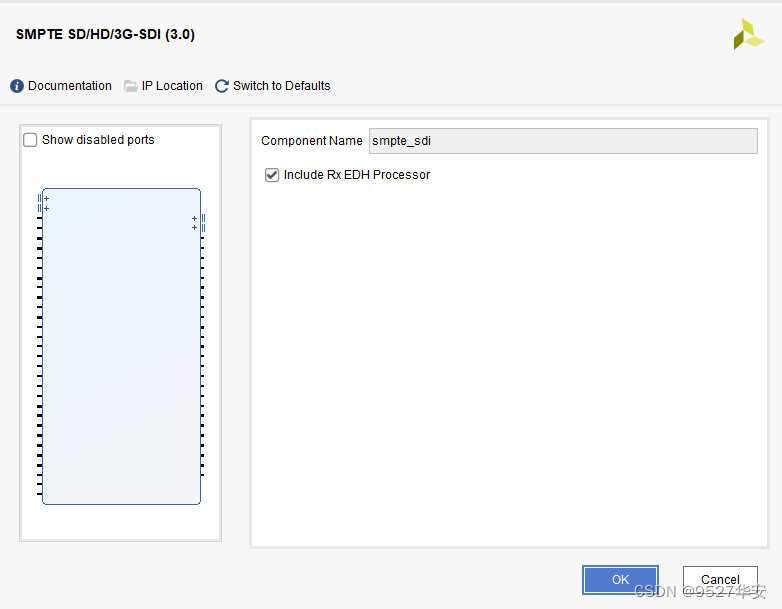

SMPTE SD/HD/3G SDI IP कोरः Xilinx श्रृङ्खला FPGAs इत्यस्य SDI विडियो एन्कोडिंग् तथा डिकोडिंग् इत्यस्य कृते एकः अद्वितीयः IP अस्ति IP विन्यासस्य उपयोगः अतीव सरलः अस्ति ।

SMPTE SD/HD/3G SDI IP कोरस्य उपयोगः GTX इत्यनेन सह अवश्यं भवति उपयोक्तृपक्षतः विडियो डेटा, ततः BT1120 विडियो SDI विडियो आउटपुट् मध्ये एन्कोड् करोति एतत् समाधानं आधिकारिक Xilinx डिजाइनं निर्दिशति;

BT1120 तः RGB मॉड्यूलस्य कार्यं SMPTE SD/HD/3G SDI IP कोर डिकोडिंग् द्वारा BT1120 विडियो आउटपुट् RGB888 विडियो मध्ये परिवर्तयितुं भवति अस्मिन् त्रयः मॉड्यूलाः सन्ति: BT1120 तः CEA861 मॉड्यूल, YUV422 तः YUV444 मॉड्यूल, YUV444 तः RGB888 च .

अस्य डिजाइनस्य विडियो कैश समाधानं 2-चैनल Xilinx आधिकारिक VDMA इमेज कैश आर्किटेक्चर स्वीकरोति; .द्वितीयः SDI विडियो VDMA मार्गेण DDR मध्ये लिखित्वा, एतत् न पठ्यते, अपितु DDR3 तः विडियो फ्यूजन ओवरले मॉड्यूल् इत्यस्य माध्यमेन पठ्यते परियोजना स्रोत कोड 1 उदाहरणरूपेण गृहीत्वा, VDMA Xilinx इत्यस्य Block Design इत्यस्य उपयोगेन डिजाइनं कृतम् अस्ति विवादो, यथा अधः दर्शितम् :

विलम्बतां न्यूनीकर्तुं VDMA इत्येतत् cache 1 frame इति सेट् भवति, यथा निम्नलिखितम् ।

बहुचैनल-वीडियो-संलयन-ओवरले-डिजाइन-खण्ड-चित्रं निम्नलिखितम् अस्ति ।

बहु-चैनल-वीडियो-संलयनं तथा ओवरले-इत्येतत् अन्तर्निहितस्य विडियोस्य तथा ओवरले-वीडियोस्य संलयनेन सुपरपोजिशनेन च निर्मितं भवति, अन्तर्निहितः विडियो प्रथमस्य चैनलस्य इनपुट्-वीडियो भवति, तथा च ओवरले-वीडियो द्वितीयस्य चैनलस्य स्केल-कृतः विडियो भवति videos are fused together and output, which can be SDK सॉफ्टवेयर गतिशीलरूपेण 2-चैनल विडियो संलयनस्य पारदर्शिता, ओवरले विडियो इत्यस्य जूम आकार, ओवरले विडियो इत्यस्य प्रदर्शनस्थानं अन्यसूचनाः च विन्यस्यति HLS समाधान C++ कोड, तथा च RTL मध्ये संश्लेषितं भवति तथा च IP मध्ये संलग्नं भवति, यस्य उपयोगः vivado Call the IP इत्यत्र कर्तुं शक्यते अस्य समाधानस्य विषये विवरणार्थं कृपया मम पूर्वस्य ब्लॉगं पश्यन्तु।

प्रत्यक्षतया गन्तुं क्लिक् कुर्वन्तु

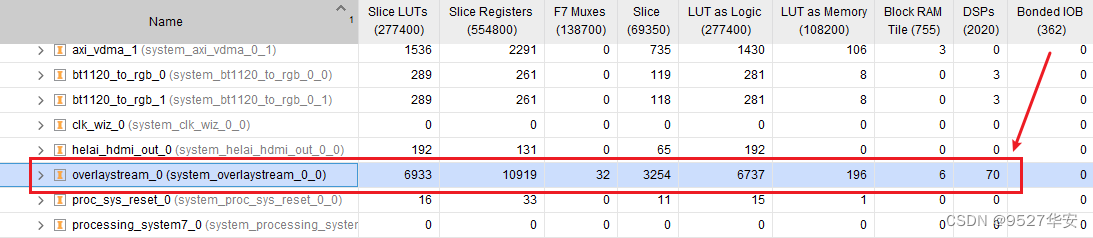

विवाडो इत्यस्मिन् अस्य IP इत्यस्य व्यापकः संसाधनप्रयोगः निम्नलिखितरूपेण अस्ति ।

HLS बहु-चैनल-वीडियो-संलयन-ओवरले-इत्येतत् सम्यक् कार्यं कर्तुं SDK-मध्ये चालकं उपयोक्तृ-कार्यक्रमं च चालयितुं आवश्यकम् अस्ति, मया परियोजनायां C भाषा-कार्यक्रमः प्रदत्तः, विवरणार्थं परियोजना-स्रोत-सङ्केतः पश्यन्तु channel video fusion overlay call इत्येतत् निम्नलिखितम् अस्ति ।

HDMI विडियो आउटपुट् आर्किटेक्चर इत्येतत् निम्नलिखितम् अस्ति ।

Xilinx आधिकारिक डिजाइनस्य सन्दर्भं दत्त्वा, AXI4-Stream तः Native प्रारूपं प्रति आउटपुट् विडियो परिवर्तयितुं VTC+AXI4-Stream To Video Out आर्किटेक्चरस्य उपयोगं कुर्वन्तु ततः RGB888 तः HDMI मध्ये परिवर्तयितुं शुद्ध verilog कोड् मध्ये कार्यान्वितस्य RGB888 तः HDMI मॉड्यूलस्य उपयोगं कुर्वन्तु, अन्ते च प्रदर्शनं कुर्वन्तु it through the monitor , RGB888 तः HDMI मॉड्यूल कोड संरचना निम्नलिखितरूपेण अस्ति:

RGB888 to HDMI मॉड्यूलस्य विषये कृपया मम पूर्वं ब्लोग्, ब्लॉग् पतां पश्यन्तु:प्रत्यक्षतया गन्तुं क्लिक् कुर्वन्तु

SDI विडियो आउटपुट् आर्किटेक्चर प्रथमं VDMA द्वारा पठितं AXI4-Stream इत्येतत् Native प्रारूपे परिवर्तयितुं शक्नोति ततः RGB इत्येतत् BT1120 इत्यत्र BT1120 विडियो इत्यत्र परिवर्तयितुं शक्नोति ।

SDI आउटपुट् मोड् मध्ये VGA समय मॉड्यूलस्य पिक्सेल घड़ी SMPTE SD/HD/3G SDI IP कोरस्य प्रेषकेन उपयोक्तृघटिका द्वारा प्रदत्ता भवति उदाहरणार्थं 3G-SDI मोड् मध्ये पिक्सेल घड़ी भिन्ना भवति , पिक्सेलघटिका 148.5M अस्ति HD-SDI 720P@60Hz मोड् मध्ये पिक्सेलघटिका 74.25M अस्ति;

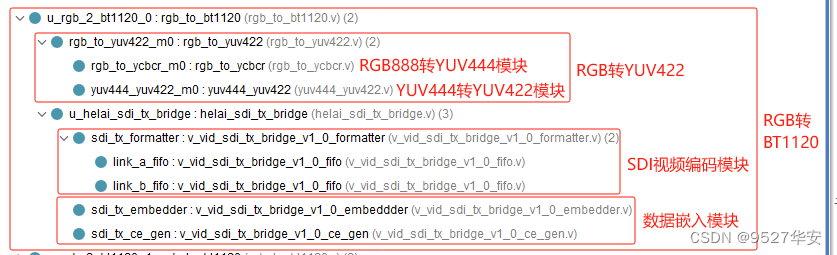

SDI आउटपुट् मोड् मध्ये RGB तः BT1120 मॉड्यूल् इत्यस्य उपयोगः आवश्यकः अस्ति यत् उपयोक्तृपक्षे RGB विडियो BT1200 विडियो मध्ये परिवर्त्य SMPTE SD/HD/3G SDI IP मध्ये आउटपुट् करणीयम् कोरः RGB तः BT1120 मॉड्यूल् , YUV444 तः YUV422 मॉड्यूल, SDI विडियो एन्कोडिंग मॉड्यूल, तथा च डेटा एम्बेडिंग मॉड्यूल् इत्येतत् समाधानं Xilinx तः RGB मॉड्यूलस्य आधिकारिकं डिजाइनं निर्दिशति यथा- १.

एतौ भागौ ग्राहकप्रक्रियायाः सह तत्सम्बद्धान् मॉड्यूलान् साझां कुर्वन्ति, ये कार्यात्मकरूपेण ग्राहकप्रक्रियायाः विपरीतप्रक्रियाः सन्ति, पुनः वर्णिताः न भविष्यन्ति

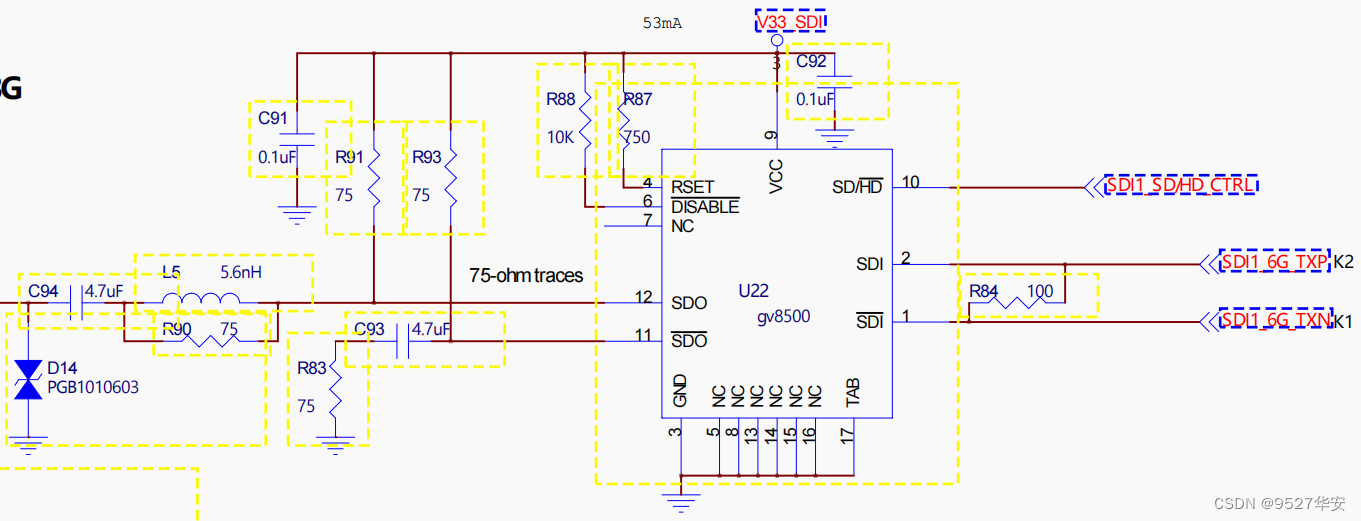

Gv8500 चिप् एकल-अन्तयुक्ते वर्धिते च चालके विभेदकरूपान्तरणस्य कार्याणि साक्षात्करोति यतः एतत् आधिकारिकं Xilinx समाधानं आकर्षयति । Gv8500 चालकस्य योजनाबद्धचित्रं निम्नलिखितम् अस्ति ।

SDI आउटपुट् मोड् मध्ये, भवद्भिः SDI to HDMI box इत्यस्य उपयोगः आवश्यकः, यतः मम हस्ते मॉनिटरे SDI interface नास्ति, केवलं HDMI interface अस्ति SDI video प्रदर्शयितुं, एतत् केवलं कर्तुं शक्यते, यदि your monitor has an SDI interface, you can directly संयोजनं दर्शयति यत् मम SDI to HDMI पेटी एकस्मिन् निश्चिते भण्डारे 100 युआन् इत्यस्मात् न्यूनतया क्रीतवती आसीत्;

अयं ब्लॉगः परियोजना स्रोतसङ्केतानां २ समुच्चयान् प्रदाति परियोजना स्रोतसङ्केतः १ उदाहरणरूपेण गृहीत्वा, अन्ये परियोजनाः अपि एतादृशाः सन्ति ।

परियोजना स्रोतसङ्केतः १ उदाहरणरूपेण गृहीत्वा परियोजना स्रोतसङ्केतसंरचना निम्नलिखितरूपेण अस्ति ।

परियोजना स्रोतसङ्केतस्य PL पार्श्वघटिका Zynq सॉफ्टकोरद्वारा प्रदत्ता भवति, अतः Zynq आरभ्यत इति SDK चालयितुं आवश्यकं तदतिरिक्तं, IP कोर इत्यादीनां विडियो फ्यूजन ओवरले तथा VDMA इत्यस्य सम्यक् कार्यं कर्तुं सॉफ्टवेयर चालकान् चालयितुं आवश्यकम् अस्ति SDK सॉफ्टवेयर कोड संरचना निम्नलिखितरूपेण अस्ति ।

SDK कोड् मध्ये विन्यासः निम्नलिखितरूपेण अस्ति, उपयोक्तारः स्वस्य आवश्यकतानुसारं मनमानारूपेण परिवर्तनं कर्तुं शक्नुवन्ति;

प्रथमः विडियो १९२०x१०८० रिजोल्यूशनयुक्तः अधः स्तरस्य विडियो अस्ति;

द्वितीयः चैनल्-वीडियो १९२०x१०८० रिजोल्यूशनयुक्तः ओवरले-वीडियो अस्ति ।

पूर्वस्मिन् चरणे प्राप्तं 600x600 ओवरले फ्यूजन विडियो 960x540 यावत् स्केल कुर्वन्तु;

अन्तर्निहितस्य विडियोस्य (0,0) निर्देशांकात् आरभ्य पूर्वस्मिन् चरणे 960x540 सुपरइम्पोज्ड् फ्यूजन विडियो ओवरले कुर्वन्तु, तथा च अन्तर्निहितस्य तथा ओवरले स्तरस्य पारदर्शितां 80 इति सेट् कुर्वन्तु

विकास बोर्ड FPGA मॉडल: Xilinx-Zynq7100-xc7z100ffg900-2;

विकास वातावरण: विवाडो2019.1;

इनपुट्: 3G-SDI कैमरा अथवा HDMI तः SDI बॉक्स, रिजोल्यूशन 1920x1080@60Hz;

आउटपुट: एचडीएमआई, संकल्प 1920x1080 @ 60Hz;

कैशिंग समाधान: Xilinx आधिकारिक VDMA समाधान;

कैश मीडिया: PS पक्ष DDR3;

विडियो संलयनं तथा ओवरले समाधानम् : एचएलएस आधारितं स्वविकसितं बहुचैनलविडियो संलयनं तथा ओवरले;

परियोजना भूमिका: अस्याः परियोजनायाः उद्देश्यं पाठकाः HDMI मध्ये SDI कार्यान्वितुं Zynq श्रृङ्खला FPGA इत्यस्य डिजाइनक्षमतासु निपुणतां प्राप्तुं शक्नुवन्ति, येन ते स्वकीयानां परियोजनानां प्रत्यारोपणं डिजाइनं च कर्तुं शक्नुवन्ति

परियोजनाखण्डनिर्माणस्य परियोजनासङ्केतवास्तुकलानां च कृते कृपया अध्याये 3 मध्ये "परियोजनास्रोतसङ्केतवास्तुकला" इति विभागं पश्यन्तु;

परियोजनायाः संसाधनस्य उपभोगः विद्युत् उपभोगः च निम्नलिखितरूपेण भवति ।

विकास बोर्ड FPGA मॉडल: Xilinx-Zynq7100-xc7z100ffg900-2;

विकास वातावरण: विवाडो2019.1;

इनपुट्: 3G-SDI कैमरा अथवा HDMI तः SDI बॉक्स, रिजोल्यूशन 1920x1080@60Hz;

आउटपुट: 3G-SDI, संकल्प 1920x1080 @ 60Hz;

कैशिंग समाधान: Xilinx आधिकारिक VDMA समाधान;

कैश मीडिया: PS पक्ष DDR3;

विडियो संलयनं तथा ओवरले समाधानम् : एचएलएस आधारितं स्वविकसितं बहुचैनलविडियो संलयनं तथा ओवरले;

परियोजना भूमिका: अस्याः परियोजनायाः उद्देश्यं पाठकाः HDMI मध्ये SDI कार्यान्वितुं Zynq श्रृङ्खला FPGA इत्यस्य डिजाइनक्षमतासु निपुणतां प्राप्तुं शक्नुवन्ति, येन ते स्वकीयानां परियोजनानां प्रत्यारोपणं डिजाइनं च कर्तुं शक्नुवन्ति

परियोजनाखण्डनिर्माणस्य परियोजनासङ्केतवास्तुकलानां च कृते कृपया अध्याये 3 मध्ये "परियोजनास्रोतसङ्केतवास्तुकला" इति विभागं पश्यन्तु;

परियोजनायाः संसाधनस्य उपभोगः विद्युत् उपभोगः च निम्नलिखितरूपेण भवति ।

1: यदि भवतः vivado संस्करणम् अस्य परियोजनायाः vivado संस्करणेन सह सङ्गतम् अस्ति तर्हि परियोजनां प्रत्यक्षतया उद्घाटयन्तु;

2: यदि भवतः vivado संस्करणम् अस्य परियोजनायाः vivado संस्करणात् न्यूनं भवति तर्हि भवतः परियोजनां उद्घाट्य File –> Save As इत्यत्र क्लिक् करणीयम् तथापि एषा पद्धतिः सुरक्षिता नास्ति अस्य परियोजनायाः संस्करणस्य अथवा उच्चतरस्य;

3: यदि भवतः vivado संस्करणम् अस्य परियोजनायाः vivado संस्करणात् अधिकं भवति तर्हि समाधानं निम्नलिखितम् अस्ति।

परियोजनां उद्घाट्य भवन्तः पश्यन्ति यत् IPs ताडिताः सन्ति, यथा ।

अस्मिन् समये भवद्भिः IP उन्नयनं कर्तव्यम् अस्ति ।

यदि भवतः FPGA मॉडल् मम सह असङ्गतम् अस्ति तर्हि भवता FPGA मॉडल् निम्नलिखितरूपेण परिवर्तयितव्यम् ।

FPGA मॉडल् परिवर्तनानन्तरं भवद्भिः IP उन्नयनं कर्तव्यम् IP उन्नयनस्य विधिः पूर्वं वर्णिता अस्ति;

1: यतः प्रत्येकस्य बोर्डस्य DDR अनिवार्यतया समानं न भवति, अतः MIG IP भवतः स्वस्य योजनाबद्धचित्रस्य अनुसारं विन्यस्तं कर्तुं आवश्यकम् अस्ति यत् भवान् मम मूलप्रकल्पस्य MIG इत्येतत् प्रत्यक्षतया अपि विलोपयितुं शक्नोति तथा च IP पुनः योजयित्वा पुनः विन्यस्तं कर्तुं शक्नोति

2: स्वस्य योजनाबद्धचित्रस्य अनुसारं पिन-प्रतिबन्धान् परिवर्तयन्तु तथा च xdc सञ्चिकायां परिवर्तयन्तु;

3: Zynq मध्ये शुद्धं FPGA प्रत्यारोपयितुं, परियोजनायां zynq सॉफ्ट कोरं योजयितुं आवश्यकम्;

यत् उपकरणं सज्जीकर्तुं आवश्यकं तत् निम्नलिखितम् अस्ति ।

FPGA विकास बोर्ड;

SDI कॅमेरा अथवा HDMI to SDI box;

SDI to HDMI पेटी;

HDMI प्रदर्शनम्;

मम विकासमण्डलं निम्नलिखितरूपेण सम्बद्धम् अस्ति ।

परियोजना स्रोतसङ्केतः १ उदाहरणरूपेण गृहीत्वा, उत्पादनं निम्नलिखितम् अस्ति ।

Zynq-SDI-Video संलयन ओवरले

बोनसः अभियांत्रिकी कोडस्य अधिग्रहणम्

कोडः अतीव विशालः अस्ति, ईमेलद्वारा प्रेषयितुं न शक्यते ।

सूचनां कथं प्राप्नुयात् : निजीरूपेण, अथवा लेखस्य अन्ते V बिजनेस कार्ड्।

संजालडिस्कसूचना निम्नलिखितरूपेण अस्ति ।

तदतिरिक्तं अनेके मित्राणि अस्य ब्लोगरस्य बहुमतानि सुझावानि च दत्तवन्तः, सेवासामग्रीविकल्पान् च समृद्धीकर्तुं आशां कुर्वन्तः यतः भिन्नमित्राणां भिन्नाः आवश्यकताः सन्ति, अतः अयं ब्लोगरः निम्नलिखितसेवाः अपि प्रदाति।