informasi kontak saya

Surat[email protected]

2024-07-12

한어Русский языкEnglishFrançaisIndonesianSanskrit日本語DeutschPortuguêsΕλληνικάespañolItalianoSuomalainenLatina

Saat ini, ada dua solusi bagi FPGA untuk mengimplementasikan pengkodean dan decoding video SDI: satu adalah dengan menggunakan chip pengkodean dan decoding khusus, seperti penerima GS2971, dan pemancar GS2972. Keuntungannya adalah kesederhanaan mendekodekan SDI menjadi YCrCb422 paralel, dan GS2972 mentransmisikan Perangkat secara langsung mengkodekan YCrCb422 paralel ke dalam video SDI. Kerugiannya adalah biayanya relatif tinggi. Anda dapat mencari harga GS2971 dan GS2972 di Baidu Departemen sumber daya logika FPGA untuk mengimplementasikan pengkodean dan decoding SDI dan menggunakan sumber daya GTP/GTX dari FPGA seri Xilinx. Untuk mencapai deserialisasi, gunakan sumber daya SMPTE SDI dari FPGA seri Xilinx untuk mengimplementasikan pengkodean dan decoding SDI sumber daya dimanfaatkan secara wajar dan sumber daya GTP/GTX tidak digunakan dengan sia-sia. Kerugiannya adalah pengoperasiannya lebih sulit dan memerlukan tingkat teknis pengembang FPGA yang lebih tinggi. Menariknya, kedua solusi ini memiliki solusi yang sesuai di blog ini, termasuk papan pengembangan perangkat keras FPGA, kode sumber teknik, dll.

Desain ini didasarkan pada papan pengembangan Zynq7100 FPGA dari seri Zynq untuk mengimplementasikan pengkodean dan decoding video SDI + penskalaan gambar + penyambungan video multi-saluran, satu adalah kamera 3G-SDI dengan resolusi 1920x1080@. 60Hz, dan HD-SDI juga dapat digunakan Atau kamera SD-SDI, karena desain ini adaptif terhadap tiga video SDI; kotak HDMI ke 3G-SDI lainnya, kotak tersebut terhubung ke laptop untuk mensimulasikan dua kamera SDI; Video SDI dihubungkan ke papan pengembangan FPGA melalui kabel koaksial soket BNC, dan kemudian video koaksial melewati chip Gv8601a bawaan untuk mewujudkan fungsi konversi ujung tunggal ke EQ diferensial dan seimbang; kemudian sinyal video SDI diferensial memasuki GTX sumber daya berkecepatan tinggi di dalam FPGA untuk mewujudkan konversi data serial ke paralel berkecepatan tinggi. Bo menyebutnya deserialisasi; video paralel yang dideserialisasi kemudian dikirim ke inti IP SMPTE SD/HD/3G SDI unik dari FPGA seri Xilinx untuk melakukan operasi decoding video SDI dan keluaran video BT1120. Pada titik ini, operasi decoding video SDI telah selesai dan Anda dapat Melakukan operasi pemrosesan gambar rutin;

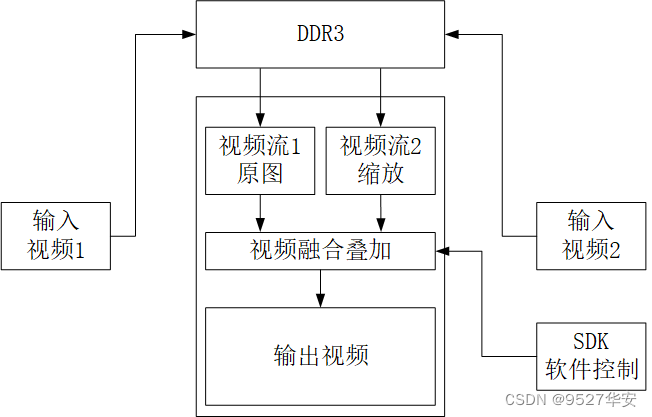

Tujuan dari desain ini adalah untuk menghasilkan video SDI yang didekodekan setelah penskalaan gambar + fusi dan superposisi video multi-saluran. Sebagai tanggapan terhadap kebutuhan proyek arus utama di pasar, blog ini telah merancang dua metode keluaran, satu adalah keluaran HDMI, dan lainnya adalah keluaran 3G -SDI, kedua metode memerlukan decoding video BT1120 untuk dikonversi ke RGB dan operasi cache gambar; desain ini menggunakan modul BT1120 ke RGB untuk mencapai konversi format video yang digunakan arsitektur cache gambar VDMA resmi 2 arah Xilinx; menerapkan caching gambar dan caching Media adalah DDR3 sisi PS onboard; video SDI pertama ditulis ke DDR melalui VDMA dan kemudian dibaca dan dikirim ke modul overlay fusi video melalui VDMA, tetapi di-overlay melalui fusi video. Modul membaca dari DDR3. Pada titik ini, video 2 saluran telah masuk ke modul overlay fusi video, dan kemudian dilakukan proses overlay fusi kemudian masuk ke modul pengiriman HDMI ke mengeluarkan tampilan HDMI, yang merupakan metode keluaran HDMI; atau format video diimplementasikan melalui konversi modul RGB ke BT1120, kemudian video memasuki inti IP SMPTE SD/HD/3G SDI, melakukan operasi pengkodean video SDI dan mengeluarkan video SDI , dan kemudian melewati sumber daya berkecepatan tinggi GTX di dalam FPGA untuk mewujudkan konversi data paralel ke serial berkecepatan tinggi, yang blog ini sebut serial, sinyal diferensial berkecepatan tinggi kemudian memasuki chip Gv8500 onboard untuk mewujudkan fungsi konversi diferensial ke ujung tunggal dan peningkatan driver. Video SDI dikeluarkan melalui soket BNC pada papan pengembangan FPGA, dan dihubungkan ke kotak SDI ke HDMI melalui kabel koaksial ke layar HDMI. blog ini menyediakan 2 set kode sumber proyek, sebagai berikut:

Dua kumpulan kode sumber proyek di atas dijelaskan sebagai berikut untuk memudahkan pemahaman pembaca:

Kode sumber proyek 1

Model FPGA dari papan pengembangan adalah Xilinx–>Xilinx-Zynq7100–xc7z100ffg900-2; ada dua sumber input, satu adalah kamera 3G-SDI dengan resolusi 1920x1080@60Hz, dan yang lainnya adalah HDMI ke 3G-SDI kotak. Kotak tersebut terhubung ke laptop. Kamera SDI analog dengan resolusi 1920x1080@60Hz; dua video masukan dikirim ke FPGA melalui dua chip Gv8601a bawaan untuk mencapai konversi ujung tunggal ke EQ diferensial dan seimbang; melalui dua saluran GTX, video SDI dideserialisasi menjadi data paralel; Kemudian melalui 2 saluran inti IP SMPTE SDI untuk memecahkan kode SDI menjadi 2 saluran data BT1120; video; kemudian melalui 2 saluran Video resmi Xilinx Ke inti IP AXI4-Stream untuk mewujudkan konversi aliran data data RGB888 ke AXI4-Stream; kemudian video tersebut ditulis ke cache DDR3 sisi PS melalui gambar VDMA resmi 2 saluran Xilinx solusi cache; kemudian fusi video multi-saluran yang dikembangkan sendiri dan inti IP overlay berdasarkan HLS mengimplementasikan operasi fusi dan overlay video 2 saluran, Kemudian masukkan inti IP AXI4-Stream To Video Out resmi Xilinx untuk mengonversi AXI4-Stream; aliran video ke aliran video Asli; lalu kirim video overlay fusi ke modul RGB ke HDMI untuk mengonversi video RGB888 ke video HDMI dan resolusi keluarannya adalah 1920x1080@60Hz akhir artikel; gambar akhirnya ditampilkan melalui layar HDMI; proyek ini memerlukan pengoperasian soft core Zynq yang cocok untuk penyambungan video SDI ke skenario HDMI;

Kode sumber proyek 2

Model FPGA dari papan pengembangan adalah Xilinx–>Xilinx-Zynq7100–xc7z100ffg900-2; ada dua sumber input, satu adalah kamera 3G-SDI dengan resolusi 1920x1080@60Hz, dan yang lainnya adalah HDMI ke 3G-SDI kotak. Kotak tersebut terhubung ke laptop. Kamera SDI analog dengan resolusi 1920x1080@60Hz; dua video masukan dikirim ke FPGA melalui dua chip Gv8601a bawaan untuk mencapai konversi ujung tunggal ke EQ diferensial dan seimbang; melalui dua saluran GTX, video SDI dideserialisasi menjadi data paralel; Kemudian melalui 2 saluran inti IP SMPTE SDI untuk memecahkan kode SDI menjadi 2 saluran data BT1120; video; kemudian melalui 2 saluran Video resmi Xilinx Ke inti IP AXI4-Stream untuk mewujudkan konversi aliran data data RGB888 ke AXI4-Stream; kemudian video tersebut ditulis ke cache DDR3 sisi PS melalui gambar VDMA resmi 2 saluran Xilinx solusi cache; kemudian fusi video multi-saluran yang dikembangkan sendiri dan inti IP overlay berdasarkan HLS mengimplementasikan operasi fusi dan overlay video 2 saluran, Kemudian masukkan inti IP AXI4-Stream To Video Out resmi Xilinx untuk mengonversi AXI4-Stream; aliran video ke aliran video asli; kemudian kirim video overlay fusi ke modul RGB ke BT1120 untuk mengubah video RGB888 menjadi video BT1120; dan kemudian meneruskan inti IP SMPTE SD /HD/3G SDI, mengkodekan video BT1120 menjadi video SDI; kemudian mengubah data paralel SDI menjadi sinyal serial berkecepatan tinggi melalui sumber daya berkecepatan tinggi GTX di dalam FPGA, dan kemudian menggunakan chip Gv8500 bawaan untuk mengimplementasikan konversi diferensial ke ujung tunggal dan driver Setelah peningkatan, resolusi keluaran adalah 1920x1080@60Hz; terakhir, kotak SDI ke HDMI digunakan untuk menyambungkan ke layar HDMI untuk tampilan; proyek ini memerlukan pengoperasian inti lunak Zynq yang cocok untuk skenario SDI ke SDI;

Proyek ini dan kode sumbernya mencakup bagian yang saya tulis sendiri dan bagian yang diperoleh dari saluran publik di Internet (termasuk CSDN, situs resmi Xilinx, situs resmi Altera, dll.). mengkritik dan mendidik; berdasarkan hal ini, proyek ini dan kode sumbernya hanya untuk studi dan penelitian pribadi oleh pembaca atau penggemar, dan dilarang digunakan untuk tujuan komersial jika timbul masalah hukum dari penggunaan komersial oleh pembaca atau penggemar itu sendiri , blog ini dan blogger tidak ada hubungannya dengan itu, jadi harap gunakan dengan hati-hati. . .

Beranda blog saya memiliki kolom video SDI, yang penuh dengan kode sumber rekayasa SDI codec FPGA dan pengenalan blog; ada codec SDI berdasarkan GS2971/GS2972, dan codec SDI berdasarkan sumber daya GTP/GTX; SDI, 6G-SDI, 12G-SDI, dll; tautan alamat kolomnya adalah sebagai berikut:

Klik untuk langsung menuju

Blog ini telah mengembangkan sendiri aplikasi overlay fusi video multi-channel. Saya telah menulis blog khusus sebelumnya. Tautan alamat blog adalah sebagai berikut:

Klik untuk langsung menuju

Diagram blok prinsip desain adalah sebagai berikut:

Melihat! ! ! !

Melihat! ! ! !

Panah ungu: jalur keluaran 3G-SDI

Panah merah: jalur keluaran HDMI

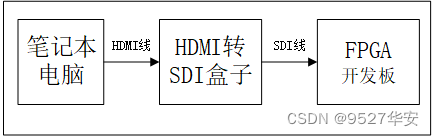

Ada dua perangkat input SDI, yang terhubung ke antarmuka input video SDI 2 arah dari papan pengembangan FPGA; satu adalah kamera 3G-SDI dengan resolusi 1920x1080@60Hz juga bisa digunakan karena desain ini adaptif terhadap tiga jenis video SDI; kotak HDMI ke 3G-SDI lainnya, kotak tersebut terhubung ke laptop untuk mensimulasikan kamera SDI yang relatif mahal, dan teman-teman dengan anggaran terbatas dapat mempertimbangkannya menggunakan kotak HDMI ke SDI untuk mensimulasikan kamera SDI. Hezibao berharga sekitar 100 yuan; saat menggunakan kotak HDMI ke SDI, sumber input dapat berupa laptop, yaitu menggunakan laptop untuk menyambung ke antarmuka input HDMI dari HDMI. Ke kotak SDI melalui kabel HDMI, dan kemudian gunakan kabel SDI untuk menghubungkan kotak HDMI ke SDI Antarmuka keluaran SDI ke papan pengembangan FPGA adalah sebagai berikut:

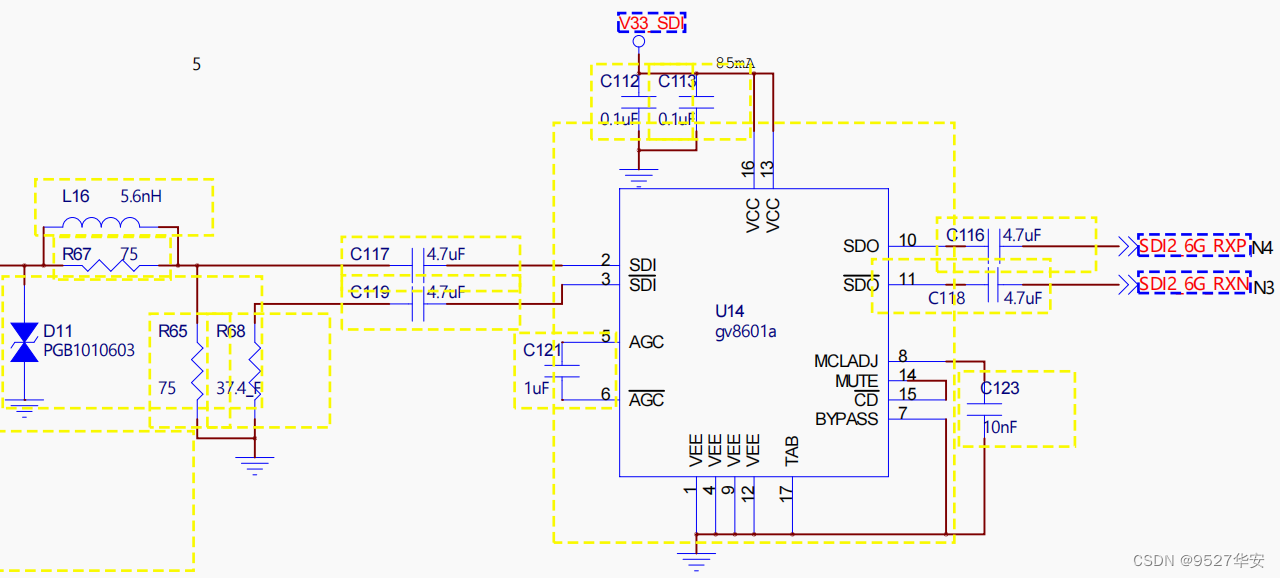

Chip Gv8601a mewujudkan fungsi konversi ujung tunggal ke EQ diferensial dan seimbang. Gv8601a dipilih di sini karena menggunakan solusi resmi Xilinx. Diagram skema equalizer Gv8601a adalah sebagai berikut:

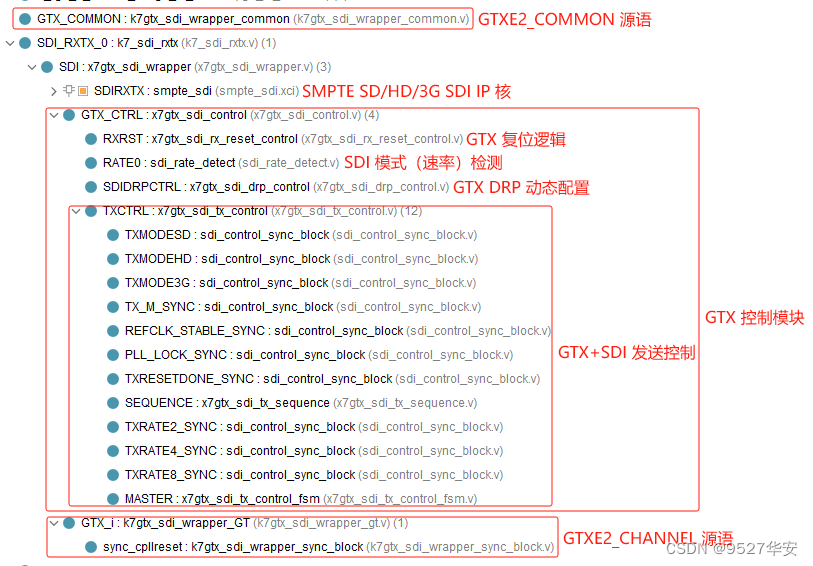

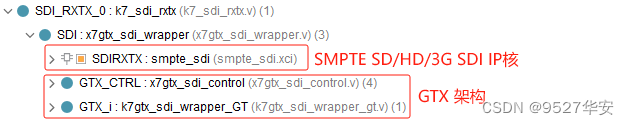

Desain ini menggunakan sumber daya pemrosesan sinyal berkecepatan tinggi GTX unik Xilinx untuk mencapai deserialisasi dan serialisasi sinyal video diferensial SDI, GTX memainkan peran deserialisasi, yaitu mendekode input sinyal diferensial serial berkecepatan tinggi menjadi digital paralel. sinyal; untuk transmisi video SDI, GTX memainkan peran serialisasi, yaitu membuat serial sinyal digital paralel input menjadi sinyal diferensial serial berkecepatan tinggi; penggunaan GTX umumnya memerlukan instantiasi inti IP GTX, melalui vivado Konfigurasikan UI antarmuka, tetapi desain ini memerlukan identifikasi otomatis dan pemrosesan adaptif video SD-SDI, HD-SDI, dan 3G-SDI, sehingga GTX perlu memiliki fungsi mengubah laju saluran secara dinamis. Ini juga dapat dikonfigurasi melalui antarmuka rate GTX, sehingga Anda tidak dapat menggunakan antarmuka UI vivado untuk konfigurasi, Anda dapat langsung membuat instance bahasa sumber GTXE2_CHANNEL dan GTXE2_COMMON dari GTX dan menggunakan sumber daya GTX secara langsung. untuk mengkonfigurasi laju garis GTX secara dinamis, Anda juga memerlukan modul kontrol GTX, modul ini mengacu pada rencana desain resmi Xilinx, dan memiliki fungsi pemantauan dinamis mode SDI, konfigurasi dinamis DRP, dll.; rencana mengacu pada desain resmi Xilinx; struktur kode modul deserialisasi dan serialisasi GTX adalah sebagai berikut:

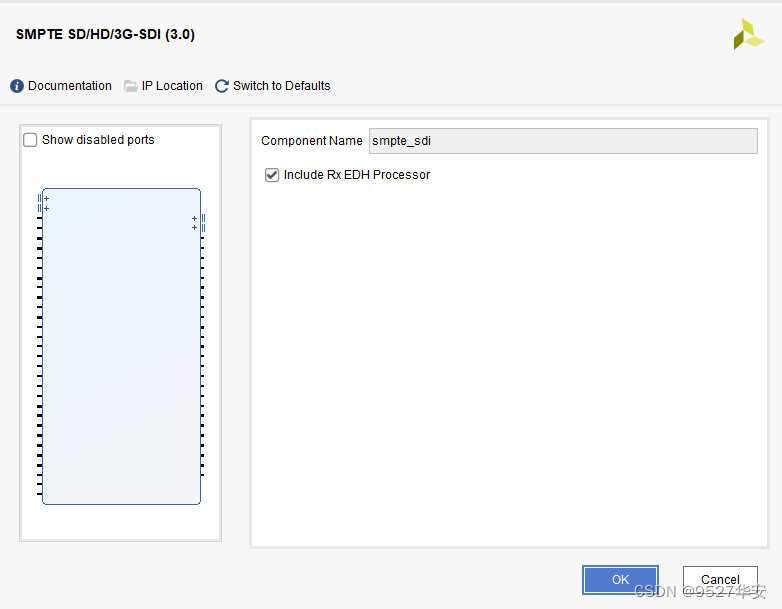

Inti IP SMPTE SD/HD/3G SDI adalah IP unik untuk pengkodean dan penguraian kode video SDI FPGA seri Xilinx. Konfigurasi IP sangat mudah digunakan. Antarmuka UI vivado adalah sebagai berikut:

Inti IP SMPTE SD/HD/3G SDI harus digunakan dengan GTX. Untuk penerimaan video SDI, IP menerima data dari GTX, dan kemudian menerjemahkan video SDI menjadi output video BT1120 data video dari sisi pengguna, dan kemudian mengkodekan video BT1120 ke dalam output video SDI; solusi ini mengacu pada desain resmi Xilinx; struktur kode inti IP SMPTE SD/HD/3G adalah sebagai berikut:

Fungsi modul BT1120 ke RGB adalah untuk mengubah output video BT1120 dengan decoding inti IP SMPTE SD/HD/3G SDI menjadi video RGB888. Terdiri dari tiga modul: modul BT1120 ke CEA861, modul YUV422 ke YUV444, dan modul YUV444 ke RGB888 Solusi ini mengacu pada desain resmi Xilinx yang diadopsi. Struktur kode modul BT1120 ke RGB adalah sebagai berikut:

Solusi cache video dari desain ini mengadopsi arsitektur cache gambar VDMA resmi 2 saluran Xilinx; media cache adalah DDR3 sisi PS; video SDI pertama ditulis ke DDR melalui VDMA dan kemudian dibaca dan dikirim ke modul overlay fusi video Video SDI kedua Setelah ditulis ke DDR melalui VDMA, video tersebut tidak dibacakan, tetapi dibaca dari DDR3 melalui modul overlay fusi video. Mengambil kode sumber proyek 1 sebagai contoh, VDMA dirancang menggunakan Desain Blok Xilinx hidup, seperti yang ditunjukkan di bawah ini:

Untuk mengurangi latensi, VDMA diatur ke cache 1 frame, sebagai berikut:

Diagram blok desain overlay fusi video multisaluran adalah sebagai berikut:

Penggabungan dan hamparan video multisaluran dibentuk oleh penggabungan dan superposisi video dasar dan video hamparan. Video dasar adalah video masukan dari saluran pertama, dan video hamparan adalah video berskala dari saluran kedua video digabungkan bersama dan dikeluarkan, yang dapat berupa Perangkat lunak SDK secara dinamis mengkonfigurasi transparansi penggabungan video 2 saluran, ukuran zoom video overlay, posisi tampilan video overlay dan informasi lainnya yang disain diimplementasikan menggunakan Kode C++ solusi HLS, dan disintesis menjadi RTL dan kemudian dienkapsulasi sebagai IP, yang dapat digunakan di vivado Hubungi IP. Untuk detail tentang solusi ini, silakan merujuk ke blog saya sebelumnya Tautan blognya adalah sebagai berikut:

Klik untuk langsung menuju

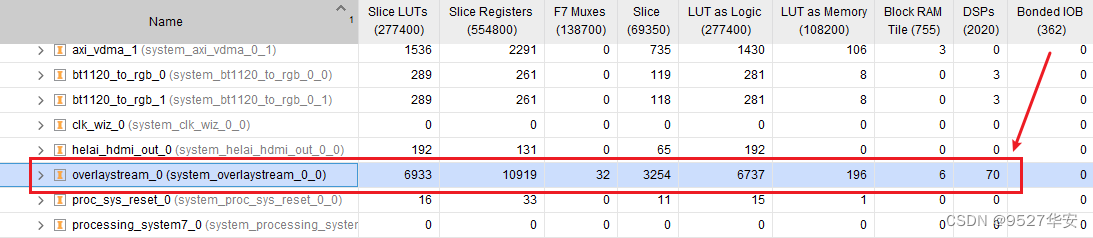

Penggunaan sumber daya komprehensif dari IP ini di vivado adalah sebagai berikut:

Hamparan fusi video multi-saluran HLS perlu menjalankan driver dan program pengguna di SDK agar berfungsi dengan baik. Saya telah menyediakan program bahasa C dalam proyek, silakan merujuk ke kode sumber proyek untuk detailnya; panggilan hamparan fusi video saluran adalah sebagai berikut:

Arsitektur keluaran video HDMI adalah sebagai berikut:

Mengacu pada desain resmi Xilinx, gunakan arsitektur VTC+AXI4-Stream To Video Out untuk mengonversi video keluaran dari AXI4-Stream ke format Asli; kemudian gunakan modul RGB888 ke HDMI yang diimplementasikan dalam kode Verilog murni untuk mengonversi RGB888 ke HDMI, dan akhirnya ditampilkan melalui monitor, struktur kode modul RGB888 ke HDMI adalah sebagai berikut:

Mengenai modul RGB888 to HDMI silahkan merujuk pada blog saya sebelumnya, alamat blog :Klik untuk langsung menuju

Arsitektur keluaran video SDI terlebih dahulu harus mengubah AXI4-Stream yang dibaca oleh VDMA ke dalam format Asli. Setelah mendapatkan video RGB888, kemudian dapat mengkonversi video RGB ke BT1120 ke BT1120.

Dalam mode keluaran SDI, jam piksel modul pengaturan waktu VGA disediakan oleh jam pengguna pengirim inti IP SMPTE SD/HD/3G SDI. Jam piksel berbeda dalam mode SDI yang berbeda , jam piksel adalah 148,5M. Dalam mode HD-SDI 720P@60Hz, jam piksel adalah 74,25M;

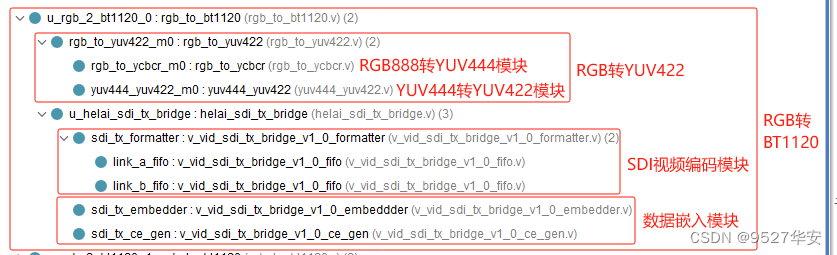

Dalam mode keluaran SDI, modul RGB ke BT1120 perlu digunakan. Fungsi modul RGB ke BT1200 adalah untuk mengubah video RGB di sisi pengguna menjadi video BT1200 dan mengeluarkannya ke IP SMPTE SD/HD/3G SDI; inti; modul RGB ke BT1120 terdiri dari modul RGB888 ke YUV444, modul YUV444 ke YUV422, modul pengkodean video SDI, dan modul penyematan data. Solusi ini mengacu pada desain resmi modul BT1120 ke RGB sebagai berikut:

Kedua bagian ini berbagi modul yang sesuai dengan proses penerimaan, yang secara fungsional merupakan proses kebalikan dari proses penerimaan dan tidak akan dijelaskan lagi;

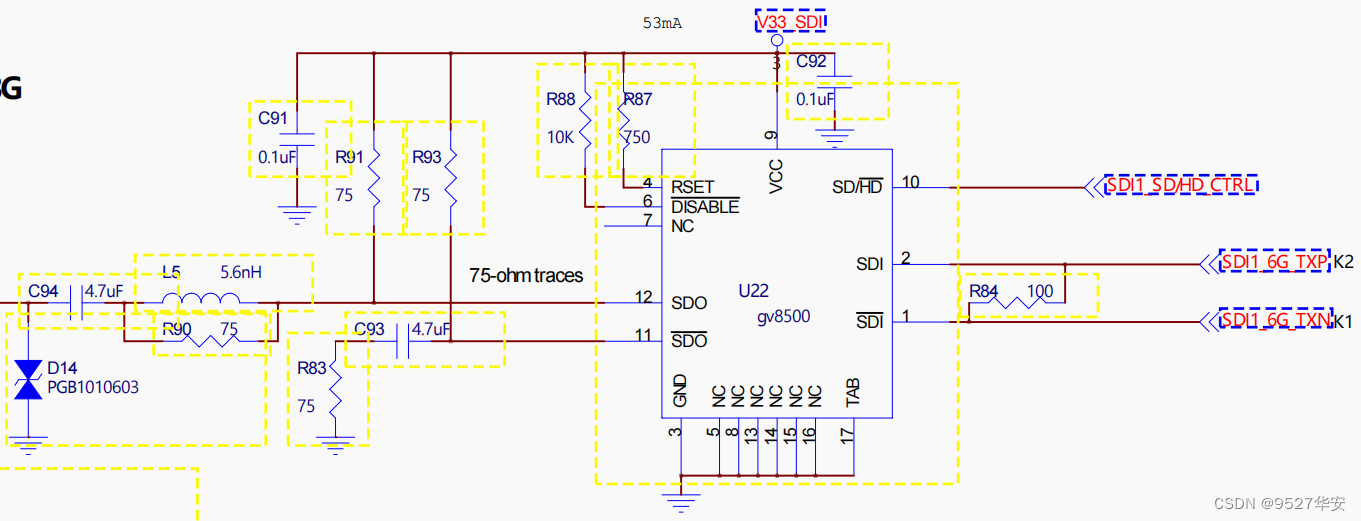

Chip Gv8500 mewujudkan fungsi konversi diferensial menjadi driver ujung tunggal dan ditingkatkan. Gv8500 dipilih di sini karena menggunakan solusi resmi Xilinx. Diagram skema driver Gv8500 adalah sebagai berikut:

Dalam mode output SDI, Anda perlu menggunakan kotak SDI ke HDMI, karena monitor di tangan saya tidak memiliki antarmuka SDI, tetapi hanya antarmuka HDMI, untuk menampilkan video SDI, tentu saja saya hanya dapat melakukan ini. jika monitor Anda memiliki antarmuka SDI, Anda dapat langsung Koneksi menunjukkan bahwa kotak SDI ke HDMI saya dibeli di toko tertentu dengan harga kurang dari 100 yuan;

Blog ini menyediakan 2 set kode sumber proyek. Mengambil kode sumber proyek 1 sebagai contoh, desain Blok Desain vivado adalah sebagai berikut.

Mengambil kode sumber proyek 1 sebagai contoh, struktur kode sumber proyek adalah sebagai berikut.

Jam samping PL dari kode sumber proyek disediakan oleh soft core Zynq, sehingga SDK perlu dijalankan untuk memulai Zynq. Selain itu, inti IP seperti video fusion overlay dan VDMA perlu menjalankan driver perangkat lunak agar berfungsi dengan baik Struktur kode perangkat lunak SDK adalah sebagai berikut:

Konfigurasi dalam kode SDK adalah sebagai berikut, pengguna dapat memodifikasinya sesuka hati sesuai kebutuhannya;

Video pertama adalah video lapisan bawah dengan resolusi 1920x1080;

Video kedua adalah video overlay dengan resolusi 1920x1080. Ambil area 1000x800 dari koordinat video overlay (400, 200) sebagai asal video fusion overlay;

Skalakan video fusi overlay 600x600 yang diperoleh pada langkah sebelumnya menjadi 960x540;

Overlay video fusi yang ditumpangkan 960x540 pada langkah sebelumnya dimulai dari koordinat (0,0) video yang mendasarinya, dan atur transparansi lapisan yang mendasari dan overlay ke 80;

Model FPGA papan pengembangan: Xilinx-Zynq7100–xc7z100ffg900-2;

Lingkungan pengembangan: Vivado2019.1;

Input: kamera 3G-SDI atau kotak HDMI ke SDI, resolusi 1920x1080@60Hz;

Keluaran: HDMI, resolusi 1920x1080@60Hz;

Solusi caching: solusi VDMA resmi Xilinx;

Media cache: sisi PS DDR3;

Solusi penggabungan dan overlay video: penggabungan dan overlay video multi-saluran yang dikembangkan sendiri berdasarkan HLS;

Peran proyek: Tujuan dari proyek ini adalah untuk memungkinkan pembaca menguasai kemampuan desain FPGA seri Zynq untuk mengimplementasikan SDI ke HDMI, sehingga mereka dapat mentransplantasikan dan merancang proyek mereka sendiri;

Untuk Desain Blok proyek dan arsitektur kode proyek, silakan lihat bagian "Arsitektur Kode Sumber Proyek" di Bab 3;

Konsumsi sumber daya dan konsumsi daya proyek adalah sebagai berikut:

Model FPGA papan pengembangan: Xilinx-Zynq7100–xc7z100ffg900-2;

Lingkungan pengembangan: Vivado2019.1;

Input: kamera 3G-SDI atau kotak HDMI ke SDI, resolusi 1920x1080@60Hz;

Keluaran: 3G-SDI, resolusi 1920x1080@60Hz;

Solusi caching: solusi VDMA resmi Xilinx;

Media cache: sisi PS DDR3;

Solusi penggabungan dan overlay video: penggabungan dan overlay video multi-saluran yang dikembangkan sendiri berdasarkan HLS;

Peran proyek: Tujuan dari proyek ini adalah untuk memungkinkan pembaca menguasai kemampuan desain FPGA seri Zynq untuk mengimplementasikan SDI ke HDMI, sehingga mereka dapat mentransplantasikan dan merancang proyek mereka sendiri;

Untuk Desain Blok proyek dan arsitektur kode proyek, silakan lihat bagian "Arsitektur Kode Sumber Proyek" di Bab 3;

Konsumsi sumber daya dan konsumsi daya proyek adalah sebagai berikut:

1: Jika versi vivado Anda konsisten dengan versi vivado proyek ini, buka proyek secara langsung;

2: Jika versi vivado Anda lebih rendah dari versi vivado proyek ini, Anda perlu membuka proyek dan klik File -> Simpan Sebagai; namun, cara paling aman adalah dengan mengupgrade versi vivado Anda ke vivado versi proyek ini atau lebih tinggi;

3: Jika versi vivado Anda lebih tinggi dari versi vivado proyek ini, solusinya adalah sebagai berikut:

Setelah membuka proyek, Anda akan menemukan bahwa IP terkunci, sebagai berikut:

Saat ini, Anda perlu mengupgrade IP. Langkah-langkahnya adalah sebagai berikut:

Jika model FPGA Anda tidak sesuai dengan model saya, Anda perlu mengubah model FPGA sebagai berikut:

Setelah mengubah model FPGA, Anda perlu mengupgrade IP. Metode upgrade IP telah dijelaskan sebelumnya;

1: Karena DDR setiap papan belum tentu sama persis, IP MIG perlu dikonfigurasi sesuai dengan diagram skematik Anda sendiri. Anda bahkan dapat langsung menghapus MIG dari proyek asli saya di sini dan menambahkan kembali IP dan mengkonfigurasi ulang ;

2: Ubah batasan pin sesuai dengan diagram skematik Anda sendiri dan modifikasi di file xdc;

3: Mentransplantasikan FPGA murni ke Zynq memerlukan penambahan inti lunak zynq ke proyek;

Perlengkapan yang perlu dipersiapkan adalah sebagai berikut:

papan pengembangan FPGA;

Kamera SDI atau kotak HDMI ke SDI;

Kotak SDI ke HDMI;

tampilan HDMI;

Papan pengembangan saya terhubung sebagai berikut:

Mengambil kode sumber proyek 1 sebagai contoh, outputnya adalah sebagai berikut:

Hamparan Penggabungan Video Zynq-SDI

Bonus: Akuisisi kode teknik

Kode terlalu besar dan tidak dapat dikirim melalui email. Kode akan dikirim melalui tautan disk jaringan tertentu.

Cara memperoleh informasi: secara pribadi, atau kartu nama V di akhir artikel.

Informasi disk jaringan adalah sebagai berikut:

Selain itu banyak sekali teman-teman yang banyak memberikan pendapat dan saran kepada blogger ini, dengan harapan dapat memperkaya konten dan pilihan layanan. Karena beda teman beda kebutuhannya, maka blogger ini juga menyediakan layanan sebagai berikut: