2024-07-12

한어Русский языкEnglishFrançaisIndonesianSanskrit日本語DeutschPortuguêsΕλληνικάespañolItalianoSuomalainenLatina

Derzeit gibt es zwei Lösungen für FPGA zur Implementierung der SDI-Videokodierung: Eine besteht darin, dedizierte Kodierungs- und Dekodierungschips wie den typischen Empfänger GS2971 und den GS2971-Empfänger direkt zu verwenden dekodiert SDI in paralleles YCrCb422 und der GS2972 kodiert das parallele YCrCb422-Video. Der Nachteil ist, dass die Kosten relativ hoch sind. Sie können auf Baidu nach den Preisen suchen Die FPGA-Logikressourcenabteilung implementiert die SDI-Kodierung und -Dekodierung und nutzt die GTP/GTX-Ressourcen des FPGA der Xilinx-Serie. Um eine Deserialisierung zu erreichen, werden die SMPTE-SDI-Ressourcen des FPGA der Xilinx-Serie verwendet Die Ressourcen werden angemessen genutzt und die GTP/GTX-Ressourcen werden nicht umsonst genutzt. Der Nachteil besteht darin, dass der Betrieb schwieriger ist und ein höheres technisches Niveau der FPGA-Entwickler erfordert. Interessanterweise gibt es hier in diesem Blog entsprechende Lösungen für diese beiden Lösungen, einschließlich Hardware-FPGA-Entwicklungsplatinen, technischem Quellcode usw.

Dieses Design basiert auf dem Zynq7100 FPGA-Entwicklungsboard der Zynq-Serie zur Implementierung von SDI-Videokodierung und -dekodierung + Bildskalierung + Mehrkanal-Videospleißung. Es gibt zwei Eingangsquellen, eine ist eine 3G-SDI-Kamera mit einer Auflösung von 1920 x 1080@. 60 Hz und HD-SDI können ebenfalls verwendet werden. Da dieses Design an drei SDI-Videos anpassbar ist, wird die Box an einen Laptop angeschlossen, um die beiden Eingänge zu simulieren SDI-Videos werden über Koaxialkabel mit BNC-Buchse an die FPGA-Entwicklungsplatine angeschlossen, und dann wird das koaxiale Videosignal durch den integrierten Gv8601a-Chip geleitet, um die Funktionen der Single-Ended-Konvertierung in differenziellen und symmetrischen EQ zu realisieren; dann gelangt das differenzielle SDI-Videosignal in die GTX Hochgeschwindigkeitsressource innerhalb des FPGA zur Realisierung einer Hochgeschwindigkeits-Seriell-Parallel-Konvertierung von Daten. Das deserialisierte parallele Video wird dann an den einzigartigen SMPTE SD/HD/3G SDI IP-Kern des FPGA der Xilinx-Serie gesendet, um SDI durchzuführen Videodekodierungsvorgang und BT1120-Videoausgabe. An diesem Punkt ist der SDI-Videodekodierungsvorgang abgeschlossen und Sie können routinemäßige Bildverarbeitungsvorgänge durchführen.

Der Zweck dieses Entwurfs besteht darin, dekodiertes SDI-Video nach der Bildskalierung + Mehrkanal-Videofusion und -Überlagerung auszugeben. Als Reaktion auf die aktuellen Mainstream-Projektanforderungen auf dem Markt hat dieser Blog zwei Ausgabemethoden entwickelt, eine ist die HDMI-Ausgabe und die andere Das andere ist die 3G-SDI-Ausgabe. Bei beiden Methoden muss BT1120-Video in RGB konvertiert werden. Bei diesem Design wird das BT1120-zu-RGB-Modul verwendet, um die Videoformatkonvertierung zu erreichen Bild-Caching und Caching implementieren. Das Medium ist Onboard-PS-seitiges DDR3; das erste SDI-Video wird über VDMA in DDR geschrieben und dann ausgelesen und an das Video-Fusion-Overlay-Modul gesendet. Das zweite SDI-Video wird nach dem Schreiben in DDR nicht ausgelesen über VDMA, wird aber durch Videofusion überlagert. Zu diesem Zeitpunkt gelangt das 2-Kanal-Video zur Fusion und Overlay-Verarbeitung in das HDMI-Sendemodul Anzeige, bei der es sich um die HDMI-Ausgabemethode handelt; oder das Videoformat wird durch die Konvertierung von RGB in BT1120 realisiert, dann gelangt das Video in den SMPTE SD/HD/3G SDI IP-Kern, führt SDI-Videokodierungsvorgänge durch und gibt SDI-Video aus Durchläuft die GTX-Hochgeschwindigkeitsressourcen im FPGA, um die Konvertierung paralleler Daten in serielle Hochgeschwindigkeitsdaten zu realisieren, die in diesem Blog als seriell bezeichnet werden. Das differenzielle Hochgeschwindigkeitssignal gelangt dann in den integrierten Gv8500-Chip, um die Funktionen der differenziellen Konvertierung zu realisieren Das SDI-Video wird über die BNC-Buchse des FPGA-Entwicklungsboards ausgegeben und über ein Koaxialkabel mit dem HDMI-Display verbunden 2 Sätze Projektquellcodes, wie folgt:

Um den Lesern das Verständnis zu erleichtern, werden die beiden oben genannten Sätze von Projektquellcodes wie folgt erläutert:

Projektquellcode 1

Das FPGA-Modell des Entwicklungsboards ist Xilinx–>Xilinx-Zynq7100–xc7z100ffg900-2; es gibt zwei Eingangsquellen, eine ist eine 3G-SDI-Kamera mit einer Auflösung von 1920 x 1080 bei 60 Hz und die andere ist ein HDMI-zu-3G-SDI Die Box wird an eine analoge SDI-Kamera mit einer Auflösung von 1920 x 1080 bei 60 Hz angeschlossen Über die beiden GTX-Kanäle wird das SDI-Video in parallele Daten deserialisiert. Anschließend werden zwei Kanäle des SMPTE-SDI-IP-Kerns durchlaufen, um SDI in zwei Kanäle von BT1120-Daten zu dekodieren Gehen Sie dann über zwei Kanäle des offiziellen Xilinx-Videoeingangs zum AXI4-Stream-IP-Kern, um die Konvertierung von RGB888-Daten in den AXI4-Stream-Datenstrom zu realisieren. Anschließend wird das Video über das offizielle 2-Kanal-VDMA-Image von Xilinx in den DDR3-Cache der PS-Seite geschrieben Cache-Lösung; dann implementiert der selbst entwickelte Mehrkanal-Videofusions- und Overlay-IP-Kern auf Basis von HLS den 2-Kanal-Videofusions- und Overlay-Betrieb. Geben Sie dann den offiziellen AXI4-Stream in den Video-Out-IP-Kern ein, um den AXI4-Stream zu konvertieren Senden Sie dann das Fusion-Overlay-Video an das RGB-zu-HDMI-Modul, um das RGB888-Video in HDMI-Video umzuwandeln und eine Auflösung von 1920 x 1080 bei 60 Hz auszugeben Ende des Artikels; das Bild wird schließlich über ein HDMI-Display angezeigt; dieses Projekt erfordert die Ausführung des Zynq-Softcores, der für SDI-Video-Splicing zu HDMI-Szenarien geeignet ist;

Projektquellcode 2

Das FPGA-Modell des Entwicklungsboards ist Xilinx–>Xilinx-Zynq7100–xc7z100ffg900-2; es gibt zwei Eingangsquellen, eine ist eine 3G-SDI-Kamera mit einer Auflösung von 1920 x 1080 bei 60 Hz und die andere ist ein HDMI-zu-3G-SDI Die Box wird an eine analoge SDI-Kamera mit einer Auflösung von 1920 x 1080 bei 60 Hz angeschlossen Über die beiden GTX-Kanäle wird das SDI-Video in parallele Daten deserialisiert. Anschließend werden zwei Kanäle des SMPTE-SDI-IP-Kerns durchlaufen, um SDI in zwei Kanäle von BT1120-Daten zu dekodieren Gehen Sie dann über zwei Kanäle des offiziellen Xilinx-Videoeingangs zum AXI4-Stream-IP-Kern, um die Konvertierung von RGB888-Daten in den AXI4-Stream-Datenstrom zu realisieren. Anschließend wird das Video über das offizielle 2-Kanal-VDMA-Image von Xilinx in den DDR3-Cache der PS-Seite geschrieben Cache-Lösung; dann implementiert der selbst entwickelte Mehrkanal-Video-Fusion- und Overlay-IP-Kern auf Basis von HLS den 2-Kanal-Video-Fusion- und Overlay-Betrieb. Geben Sie dann den offiziellen AXI4-Stream in den Video-Out-IP-Kern ein, um den AXI4-Stream zu konvertieren Videostream zum nativen Videostream; dann wird das Fusions-Overlay-Video an das RGB-zu-BT1120-Video gesendet und dann wird der SMPTE-SD/HD/3G-SDI-IP-Core in SDI-Video umgewandelt; wandelt SDI-Paralleldaten über die GTX-Hochgeschwindigkeitsressourcen im FPGA in Hochgeschwindigkeitssignale um und implementiert dann den integrierten Gv8500-Chip, um die Differenzkonvertierung in Single-Ended und Treiber zu implementieren. Nach der Verbesserung beträgt die Ausgabeauflösung schließlich 1920 x 1080 bei 60 Hz Für die Anzeige wird eine SDI-zu-HDMI-Box verwendet; für dieses Projekt ist die Ausführung eines Zynq-Softcores erforderlich, der für SDI-zu-SDI-Szenarien geeignet ist;

Dieses Projekt und sein Quellcode umfassen sowohl von mir selbst geschriebene Teile als auch Teile, die von öffentlichen Kanälen im Internet bezogen wurden (einschließlich CSDN, der offiziellen Website von Xilinx, der offiziellen Website von Altera usw.). Wenn Sie das Gefühl haben, dass es anstößig ist, senden Sie bitte eine private Nachricht an Kritisieren und informieren Sie dieses Projekt. Das Projekt und sein Quellcode dienen nur dem persönlichen Studium und der Recherche durch Leser oder Fans und dürfen nicht für kommerzielle Zwecke verwendet werden, wenn sich aus der kommerziellen Nutzung rechtliche Probleme ergeben , dieser Blog und der Blogger haben nichts damit zu tun, also verwenden Sie ihn bitte mit Vorsicht. . .

Auf meiner Blog-Homepage gibt es eine SDI-Videospalte, die voll von FPGA-Codec-SDI-Engineering-Quellcode und Blog-Einführung ist. Es gibt SDI-Codecs, die auf GS2971/GS2972 basieren, und SDI-Codecs, die auf GTP/GTX-Ressourcen basieren. SDI, 6G-SDI, 12G-SDI usw.; der Spaltenadresslink lautet wie folgt:

Klicken Sie hier, um direkt zu gelangen

Dieser Blog hat selbst eine Mehrkanal-Video-Fusion-Overlay-Anwendung entwickelt. Der Link zur Blog-Adresse lautet wie folgt:

Klicken Sie hier, um direkt zu gelangen

Das Blockdiagramm des Konstruktionsprinzips lautet wie folgt:

Beachten! ! ! !

Beachten! ! ! !

Lila Pfeil: 3G-SDI-Ausgabepfad

Roter Pfeil: HDMI-Ausgabepfad

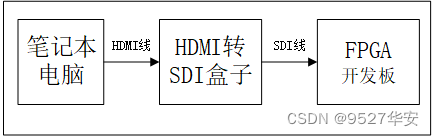

Es gibt zwei SDI-Eingabegeräte, die an die 2-Wege-SDI-Videoeingangsschnittstelle des FPGA-Entwicklungsboards angeschlossen werden können; eines davon ist eine 3G-SDI-Kamera mit einer Auflösung von 1920x1080@60Hz Aufgrund dieses Designs ist es adaptiv für drei Arten von SDI-Videos; eine weitere HDMI-zu-3G-SDI-Box, die an einen Laptop angeschlossen wird, um eine SDI-Kamera zu simulieren, ist relativ teuer und kann von Freunden mit einem begrenzten Budget verwendet werden Erwägen Sie die Verwendung einer HDMI-zu-SDI-Box zur Simulation einer SDI-Kamera. Bei Verwendung einer HDMI-zu-SDI-Box kann die Eingangsquelle ein Laptop sein, d HDMI-zu-SDI-Box über ein HDMI-Kabel, und dann verwenden Sie ein SDI-Kabel, um die HDMI-zu-SDI-Box anzuschließen. Die SDI-Ausgangsschnittstelle zur FPGA-Entwicklungsplatine ist wie folgt:

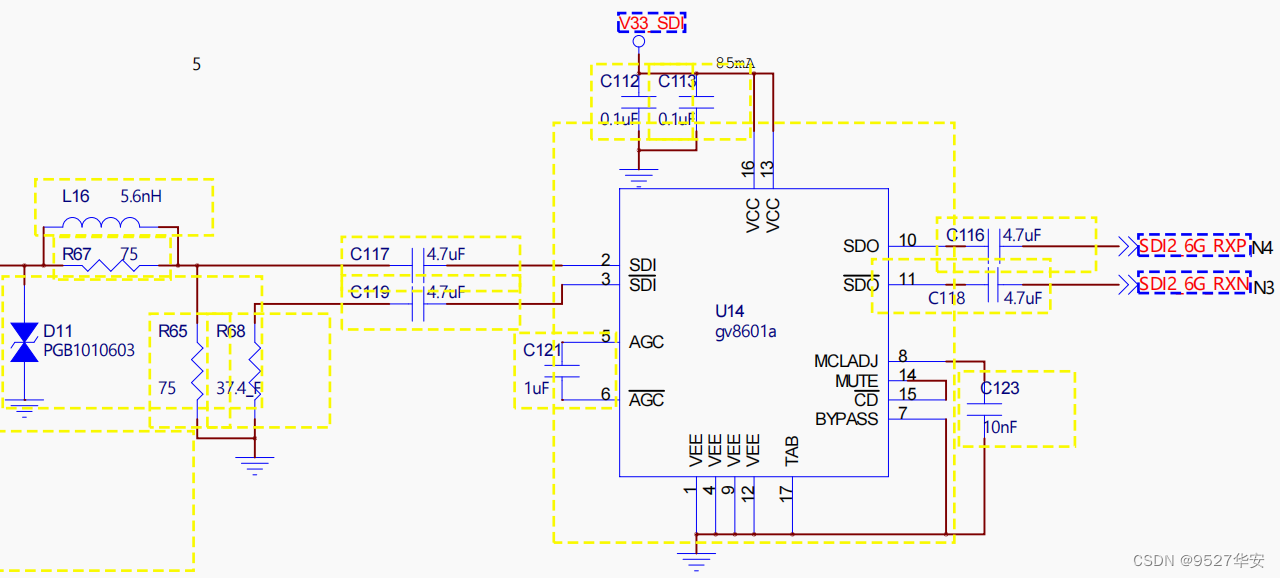

Der Gv8601a-Chip realisiert die Funktionen der Single-Ended-Konvertierung in den differenziellen und symmetrischen EQ. Der Gv8601a wird hier ausgewählt, da er auf die offizielle Xilinx-Lösung zurückgreift. Das schematische Diagramm des Gv8601a-Equalizers sieht wie folgt aus:

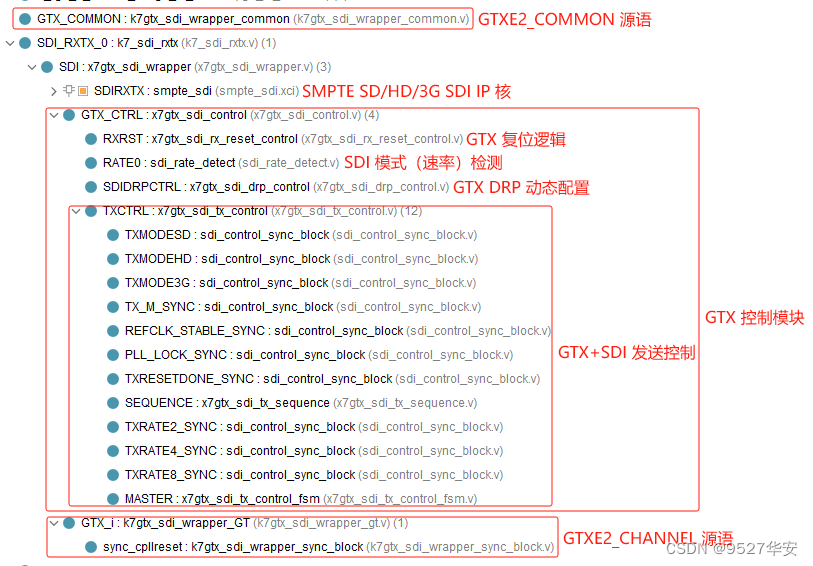

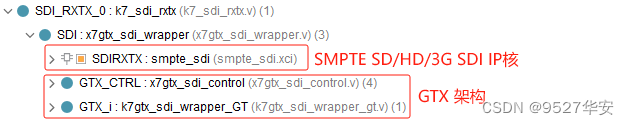

Dieses Design nutzt die einzigartigen GTX-Hochgeschwindigkeitssignalverarbeitungsressourcen, um eine Deserialisierung und Serialisierung von SDI-Differenzvideosignalen zu erreichen. Beim SDI-Videoempfang übernimmt GTX die Rolle der Deserialisierung, d Bei der SDI-Videoübertragung übernimmt GTX die Rolle der Serialisierung, d Schnittstelle, aber dieses Design erfordert eine automatische Identifizierung und adaptive Verarbeitung von SD-SDI-, HD-SDI- und 3G-SDI-Videos, daher muss GTX über die Funktion verfügen, die Zeilenrate dynamisch zu ändern. Diese Funktion kann über die DRP-Schnittstelle konfiguriert werden. Es kann auch über die Rate-Schnittstelle von GTX konfiguriert werden, sodass Sie nicht die UI-Schnittstelle von Vivado für die Konfiguration verwenden können. Stattdessen können Sie die GTXE2_CHANNEL- und GTXE2_COMMON-Quellsprachen direkt instanziieren und die GTX-Ressourcen direkt verwenden. Um die GTX-Leitungsrate dynamisch zu konfigurieren, benötigen Sie außerdem ein GTX-Steuermodul. Dieses Modul bezieht sich auf den offiziellen Designplan von Xilinx und verfügt über die Funktionen der dynamischen Überwachung des SDI-Modus, der dynamischen Konfiguration von DRP usw.; Plan bezieht sich auf das offizielle Design von Xilinx. Die Codestruktur des GTX-Deserialisierungs- und Serialisierungsmoduls ist wie folgt:

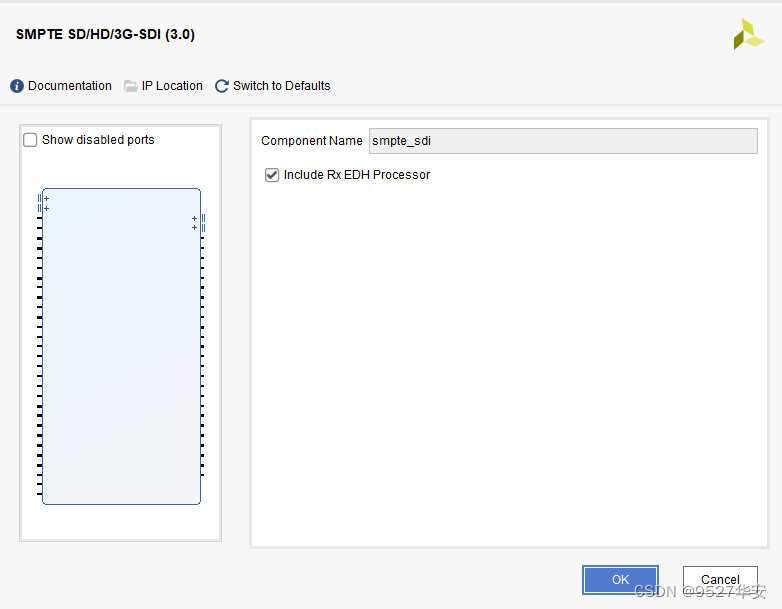

Der SMPTE SD/HD/3G SDI IP-Core ist eine einzigartige IP für die SDI-Videokodierung und -dekodierung von FPGAs der Xilinx-Serie. Die IP-Konfiguration ist sehr einfach. Die UI-Schnittstelle von vivado ist wie folgt.

Der SMPTE SD/HD/3G SDI IP-Kern muss mit GTX verwendet werden. Für den SDI-Videoempfang empfängt die IP Daten von GTX und dekodiert dann das SDI-Video in die BT1120-Videoausgabe. Für die SDI-Videoübertragung empfängt die IP BT1120 Videodaten von der Benutzerseite und kodiert dann das BT1120-Video in SDI-Videoausgabe; diese Lösung bezieht sich auf das offizielle Xilinx-Design. Die SMPTE SD/HD/3G SDI IP-Kerncodestruktur ist wie folgt:

Die Funktion des BT1120-zu-RGB-Moduls besteht darin, die BT1120-Videoausgabe durch SMPTE SD/HD/3G SDI-IP-Core-Dekodierung in RGB888-Video umzuwandeln. Es besteht aus drei Modulen: BT1120-zu-CEA861-Modul, YUV422-zu-YUV444-Modul und YUV444-zu-RGB888 Diese Lösung bezieht sich auf das offizielle Xilinx-Design. Die Codestruktur des BT1120-zu-RGB-Moduls lautet wie folgt:

Die Video-Cache-Lösung dieses Designs übernimmt die offizielle 2-Kanal-VDMA-Bild-Cache-Architektur; das Cache-Medium ist PS-seitiges DDR3; das erste SDI-Video wird über VDMA in DDR geschrieben und dann ausgelesen und an das Video-Fusion-Overlay-Modul gesendet . Das zweite SDI-Video wird nach dem Schreiben in DDR nicht über das Video-Fusion-Overlay-Modul aus DDR3 ausgelesen. Am Beispiel des Projektquellcodes 1 wird VDMA mit dem Blockdesign von Xilinx entworfen vivado, wie unten gezeigt:

Um die Latenz zu reduzieren, wird VDMA wie folgt so eingestellt, dass 1 Frame zwischengespeichert wird:

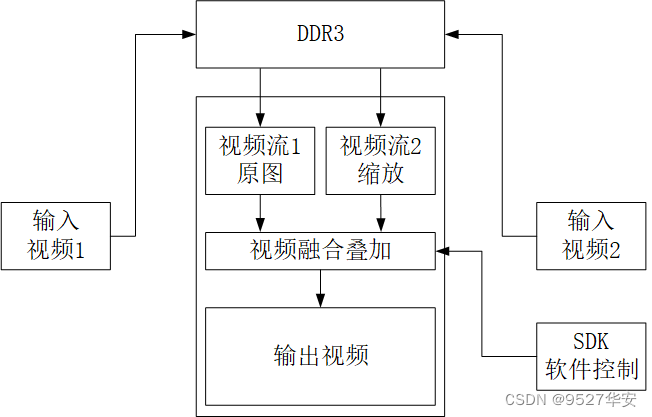

Das Blockdiagramm des Mehrkanal-Video-Fusion-Overlay-Designs sieht wie folgt aus:

Die Fusion und Überlagerung von Mehrkanalvideos erfolgt durch die Fusion und Überlagerung des zugrunde liegenden Videos und des Overlay-Videos. Das zugrunde liegende Video ist das Eingabevideo des ersten Kanals und das Overlay-Video ist das skalierte Video des zweiten Kanals Videos werden zusammengeführt und ausgegeben. Die SDK-Software konfiguriert dynamisch die Transparenz der 2-Kanal-Videofusion, die Zoomgröße des Overlay-Videos, die Anzeigeposition des Overlay-Videos und andere Informationen Der C++-Code der HLS-Lösung wird in RTL synthetisiert und in IP gekapselt, das in vivado verwendet werden kann. Weitere Informationen zu dieser Lösung finden Sie in meinem vorherigen Blog. Der Blog-Link lautet wie folgt:

Klicken Sie hier, um direkt zu gelangen

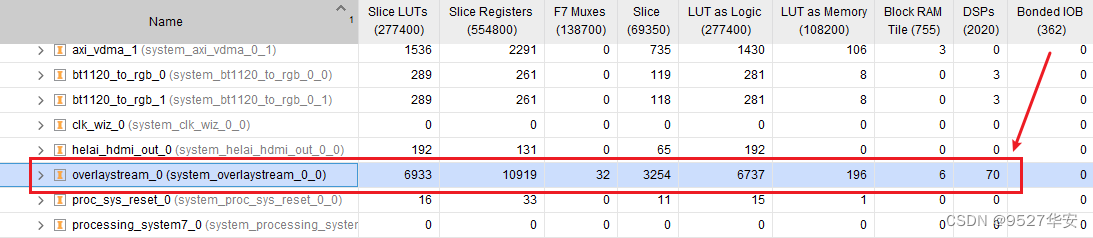

Die umfassende Ressourcennutzung dieser IP in vivado ist wie folgt:

Das HLS-Mehrkanal-Videofusions-Overlay muss den Treiber und das Benutzerprogramm im SDK ausführen, damit es ordnungsgemäß funktioniert. Weitere Informationen finden Sie im Quellcode des Projekts. Der Overlay-Aufruf für die Kanalvideofusion lautet wie folgt:

Die HDMI-Videoausgabearchitektur ist wie folgt:

Unter Bezugnahme auf das offizielle Design von Xilinx wird die VTC+AXI4-Stream To Video Out-Architektur verwendet, um das Ausgabevideo von AXI4-Stream in das native Format zu konvertieren. Anschließend wird das in reinem Verilog-Code implementierte RGB888-zu-HDMI-Modul verwendet, um RGB888 in HDMI zu konvertieren und schließlich anzuzeigen Wenn es über den Monitor läuft, ist die Codestruktur des RGB888-zu-HDMI-Moduls wie folgt:

Informationen zum RGB888-zu-HDMI-Modul finden Sie in meinem vorherigen Blog, Blog-Adresse:Klicken Sie hier, um direkt zu gelangen

Die SDI-Videoausgabearchitektur muss zunächst den von VDMA gelesenen AXI4-Stream in das native Format konvertieren. Nach Erhalt des RGB888-Videos kann dann das RGB-Video in BT1120-Video umgewandelt werden. Die Architektur ist wie folgt:

Im SDI-Ausgabemodus wird der Pixeltakt des VGA-Timing-Moduls vom sendenden Benutzertakt des SMPTE SD/HD/3G SDI-IP-Kerns bereitgestellt. Der Pixeltakt ist in verschiedenen SDI-Modi unterschiedlich , beträgt der Pixeltakt 148,5 Mio. Im HD-SDI 720P@60Hz-Modus beträgt der Pixeltakt 74,25 Mio.;

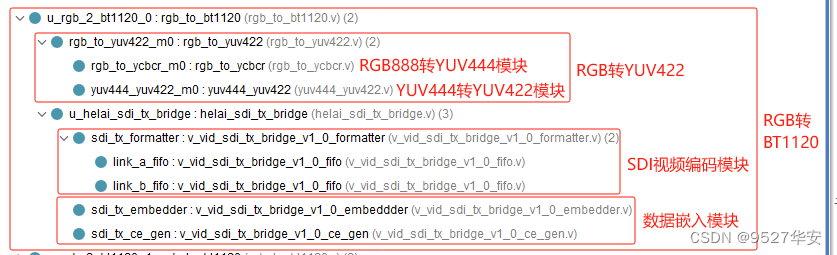

Im SDI-Ausgabemodus muss das RGB-zu-BT1120-Modul verwendet werden; die Funktion des RGB-zu-BT1200-Moduls besteht darin, das RGB-Video auf der Benutzerseite in BT1200-Video umzuwandeln und es an die SMPTE SD/HD/3G SDI-IP auszugeben Der Kern besteht aus einem RGB888-zu-YUV444-Modul, einem SDI-Videokodierungsmodul und einem Dateneinbettungsmodul. Diese Lösung bezieht sich auf die Codestruktur des BT1120-zu-RGB-Moduls wie folgt:

Diese beiden Teile teilen sich die entsprechenden Module mit dem Empfangsprozess, die funktional den umgekehrten Prozess des Empfangsprozesses darstellen und nicht noch einmal beschrieben werden;

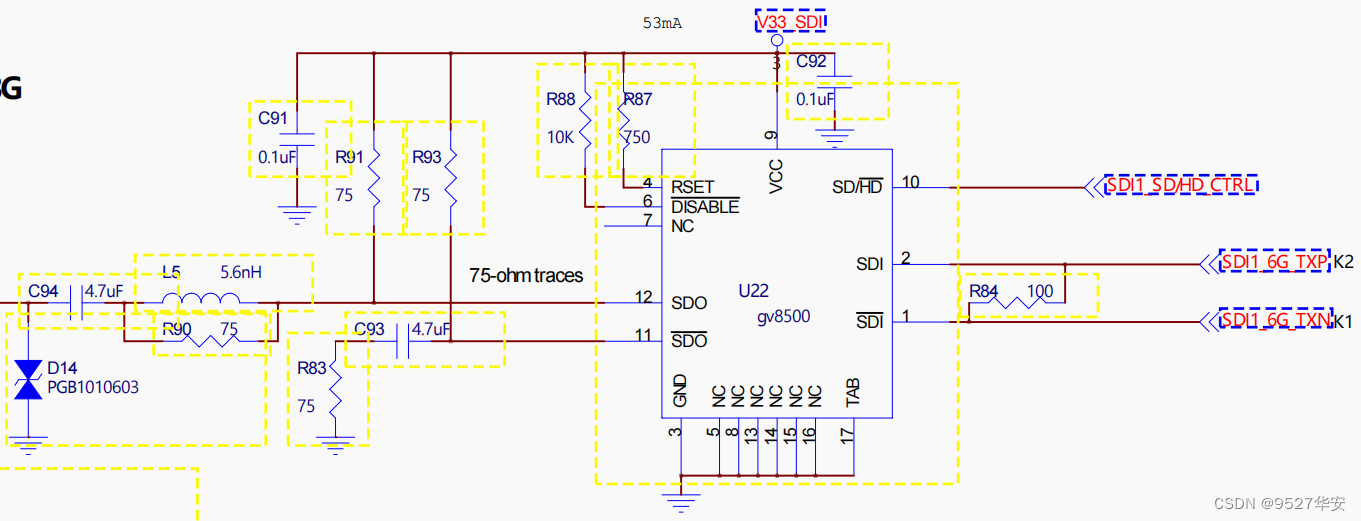

Der Gv8500-Chip realisiert die Funktionen der differenziellen Konvertierung zu Single-Ended und Enhanced Driver. Der Gv8500 wird hier ausgewählt, da er auf der offiziellen Xilinx-Lösung basiert. Natürlich können auch andere Gerätetypen verwendet werden. Das schematische Diagramm des Gv8500-Treibers sieht wie folgt aus:

Im SDI-Ausgabemodus müssen Sie eine SDI-zu-HDMI-Box verwenden, da der Monitor in meiner Hand keine SDI-Schnittstelle, sondern nur eine HDMI-Schnittstelle hat. Um SDI-Video anzuzeigen, ist dies natürlich nur möglich Wenn Ihr Monitor über eine SDI-Schnittstelle verfügt, können Sie diese direkt anschließen. Die Verbindung zeigt, dass meine SDI-zu-HDMI-Box in einem bestimmten Geschäft für weniger als 100 Yuan gekauft wurde.

Dieser Blog stellt zwei Sätze von Projektquellcodes bereit. Das Design von vivado Block Design ist wie folgt: Das Design von Block Design ist Teil der Bildcache-Architektur.

Am Beispiel von Projektquellcode 1 sieht die Struktur des Projektquellcodes wie folgt aus: Andere Projekte sind ähnlich:

Der PL-seitige Takt des Projektquellcodes wird vom Zynq-Softcore bereitgestellt, daher muss das SDK ausgeführt werden, um Zynq zu starten. Darüber hinaus müssen IP-Kerne wie Video Fusion Overlay und VDMA ausgeführt werden, um ordnungsgemäß zu funktionieren Die Codestruktur der SDK-Software ist wie folgt:

Die Konfiguration im SDK-Code ist wie folgt: Benutzer können sie entsprechend ihren eigenen Anforderungen beliebig ändern.

Das erste Video ist das Video der untersten Ebene mit einer Auflösung von 1920 x 1080;

Das zweite Kanalvideo ist das Overlay-Video mit einer Auflösung von 1920 x 1080. Nehmen Sie einen 1000 x 800-Bereich aus den Overlay-Videokoordinaten (400, 200) als Ursprung für das Overlay-Fusion-Video.

Skalieren Sie das im vorherigen Schritt erhaltene 600x600-Overlay-Fusion-Video auf 960x540.

Überlagern Sie das überlagerte Fusionsvideo im Format 960 x 540 im vorherigen Schritt, beginnend mit der Koordinate (0,0) des zugrunde liegenden Videos, und stellen Sie die Transparenz der darunter liegenden und überlagerten Ebene auf 80 ein.

Entwicklungsplatine FPGA-Modell: Xilinx-Zynq7100–xc7z100ffg900-2;

Entwicklungsumgebung: Vivado2019.1;

Eingang: 3G-SDI-Kamera oder HDMI-zu-SDI-Box, Auflösung 1920 x 1080 bei 60 Hz;

Ausgang: HDMI, Auflösung 1920 x 1080 bei 60 Hz;

Caching-Lösung: Offizielle VDMA-Lösung von Xilinx;

Cache-Medien: PS-seitiges DDR3;

Videofusions- und Overlay-Lösung: selbstentwickelte Mehrkanal-Videofusion und Overlay auf Basis von HLS;

Projektrolle: Der Zweck dieses Projekts besteht darin, den Lesern die Möglichkeit zu geben, die Designfunktionen des FPGA der Zynq-Serie zur Implementierung von SDI zu HDMI zu beherrschen, damit sie ihre eigenen Projekte übertragen und entwerfen können.

Informationen zum Projektblockdesign und zur Projektcodearchitektur finden Sie im Abschnitt „Projektquellcodearchitektur“ in Kapitel 3;

Der Ressourcenverbrauch und der Stromverbrauch des Projekts sind wie folgt:

Entwicklungsplatine FPGA-Modell: Xilinx-Zynq7100–xc7z100ffg900-2;

Entwicklungsumgebung: Vivado2019.1;

Eingang: 3G-SDI-Kamera oder HDMI-zu-SDI-Box, Auflösung 1920 x 1080 bei 60 Hz;

Ausgabe: 3G-SDI, Auflösung 1920 x 1080 bei 60 Hz;

Caching-Lösung: Offizielle VDMA-Lösung von Xilinx;

Cache-Medien: PS-seitiges DDR3;

Videofusions- und Overlay-Lösung: selbstentwickelte Mehrkanal-Videofusion und Overlay auf Basis von HLS;

Projektrolle: Der Zweck dieses Projekts besteht darin, den Lesern die Möglichkeit zu geben, die Designfunktionen des FPGA der Zynq-Serie zur Implementierung von SDI zu HDMI zu beherrschen, damit sie ihre eigenen Projekte übertragen und entwerfen können.

Informationen zum Projektblockdesign und zur Projektcodearchitektur finden Sie im Abschnitt „Projektquellcodearchitektur“ in Kapitel 3;

Der Ressourcenverbrauch und der Stromverbrauch des Projekts sind wie folgt:

1: Wenn Ihre Vivado-Version mit der Vivado-Version dieses Projekts übereinstimmt, öffnen Sie das Projekt direkt.

2: Wenn Ihre Vivado-Version niedriger ist als die Vivado-Version dieses Projekts, müssen Sie das Projekt öffnen und auf Datei –> Speichern unter klicken. Die sicherste Methode ist jedoch, Ihre Vivado-Version auf das Vivado zu aktualisieren dieses Projekts oder höher;

3: Wenn Ihre Vivado-Version höher ist als die Vivado-Version dieses Projekts, lautet die Lösung wie folgt:

Nach dem Öffnen des Projekts werden Sie feststellen, dass die IPs wie folgt gesperrt sind:

Zu diesem Zeitpunkt müssen Sie die IP aktualisieren. Die Schritte sind wie folgt:

Wenn Ihr FPGA-Modell nicht mit meinem übereinstimmt, müssen Sie das FPGA-Modell wie folgt ändern:

Nach dem Ändern des FPGA-Modells müssen Sie die IP aktualisieren. Die Methode zur Aktualisierung der IP wurde bereits beschrieben.

1: Da die DDR jeder Karte nicht unbedingt genau gleich ist, muss die MIG-IP gemäß Ihrem eigenen Schaltplan konfiguriert werden. Sie können die MIG meines ursprünglichen Projekts sogar direkt löschen und die IP erneut hinzufügen und neu konfigurieren.

2: Ändern Sie die Pin-Einschränkungen gemäß Ihrem eigenen Schaltplan und ändern Sie sie in der xdc-Datei.

3: Um reines FPGA auf Zynq zu übertragen, muss dem Projekt ein Zynq-Softcore hinzugefügt werden.

Die Ausrüstung, die vorbereitet werden muss, ist wie folgt:

FPGA-Entwicklungsboard;

SDI-Kamera oder HDMI-zu-SDI-Box;

SDI-zu-HDMI-Box;

HDMI-Anzeige;

Mein Entwicklungsboard ist wie folgt angeschlossen:

Am Beispiel des Projektquellcodes 1 sieht die Ausgabe wie folgt aus:

Zynq-SDI-Video Fusion Overlay

Bonus: Erwerb von Engineering-Code

Der Code ist zu groß und kann nicht per E-Mail gesendet werden. Er wird über einen bestimmten Netzwerk-Festplattenlink gesendet.

So erhalten Sie Informationen: privat oder über die V-Visitenkarte am Ende des Artikels.

Die Informationen zur Netzwerkfestplatte lauten wie folgt:

Darüber hinaus haben viele Freunde diesem Blogger viele Meinungen und Vorschläge gegeben, in der Hoffnung, den Serviceinhalt und die Optionen zu bereichern. Da verschiedene Freunde unterschiedliche Bedürfnisse haben, bietet dieser Blogger auch die folgenden Dienste an: