minhas informações de contato

Correspondência[email protected]

2024-07-12

한어Русский языкEnglishFrançaisIndonesianSanskrit日本語DeutschPortuguêsΕλληνικάespañolItalianoSuomalainenLatina

Atualmente, existem duas soluções para FPGA implementar codificação e decodificação de vídeo SDI: uma é usar chips de codificação e decodificação dedicados, como o receptor típico GS2971 e o transmissor GS2972. A vantagem é a simplicidade, por exemplo, o receptor GS2971. decodifica SDI em YCrCb422 paralelo, e o GS2972 transmite O dispositivo codifica diretamente o YCrCb422 paralelo em vídeo SDI. A desvantagem é que o custo é relativamente alto. Você pode pesquisar os preços de GS2971 e GS2972 no Baidu. Departamento de recursos lógicos FPGA para implementar codificação e decodificação SDI e usar os recursos GTP/GTX do FPGA da série Xilinx. Para obter a desserialização, use os recursos SMPTE SDI do FPGA da série Xilinx para implementar a codificação e decodificação SDI. os recursos são razoavelmente utilizados e os recursos GTP/GTX não são usados em vão. A desvantagem é que a operação é mais difícil e requer maior nível técnico dos desenvolvedores de FPGA. Curiosamente, essas duas soluções têm soluções correspondentes aqui neste blog, incluindo placas de desenvolvimento de hardware FPGA, código-fonte de engenharia, etc.

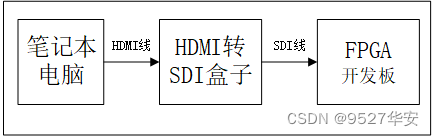

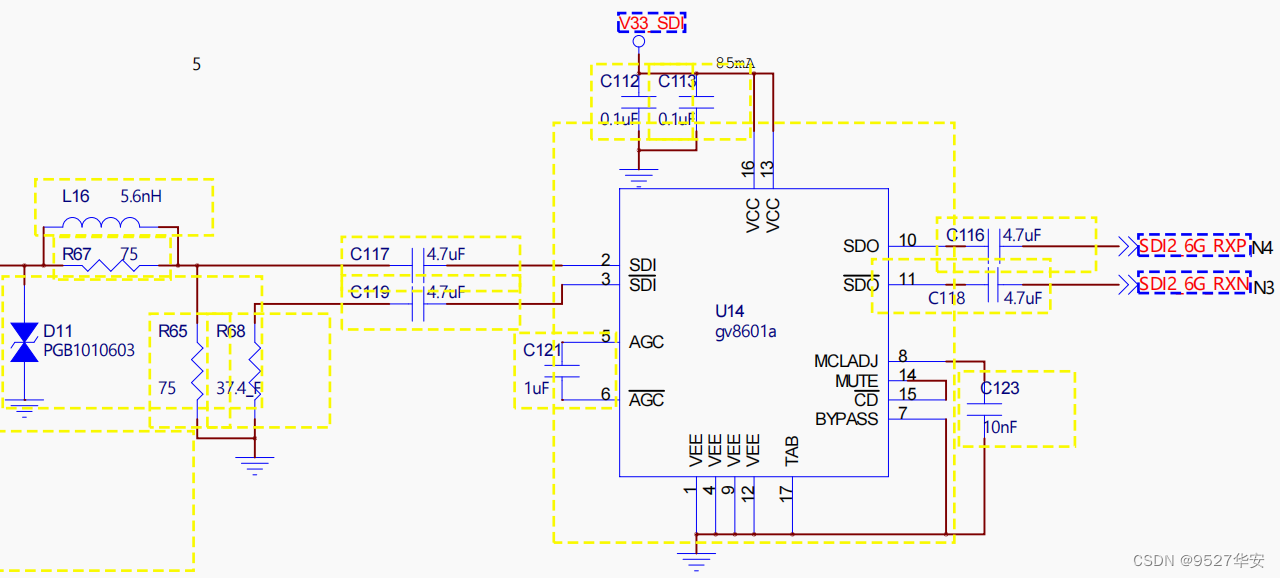

Este design é baseado na placa de desenvolvimento Zynq7100 FPGA da série Zynq para implementar codificação e decodificação de vídeo SDI + dimensionamento de imagem + emenda de vídeo multicanal. Existem duas fontes de entrada, uma é uma câmera 3G-SDI com resolução de 1920x1080@. 60Hz e HD-SDI também podem ser usados. Ou câmera SD-SDI, porque este design é adaptável a três vídeos SDI; outra caixa HDMI para 3G-SDI, a caixa é conectada a um laptop para simular uma câmera SDI; Os vídeos SDI são conectados à placa de desenvolvimento FPGA através do soquete BNC de cabos coaxiais e, em seguida, o vídeo coaxial passa pelo chip Gv8601a integrado para realizar as funções de conversão de extremidade única para EQ diferencial e balanceado e, em seguida, o sinal de vídeo SDI diferencial entra no GTX; recurso de alta velocidade dentro do FPGA para realizar conversão de dados serial em paralelo de alta velocidade. Bo chama isso de desserialização; o vídeo paralelo desserializado é então enviado para o núcleo SMPTE SD/HD/3G SDI IP exclusivo do FPGA da série Xilinx para executar SDI. operação de decodificação de vídeo e saída de vídeo BT1120. Neste ponto, a operação de decodificação de vídeo SDI foi concluída e você pode realizar operações de processamento de imagem de rotina;

O objetivo deste design é produzir vídeo SDI decodificado após dimensionamento de imagem + fusão e superposição de vídeo multicanal. Em resposta às atuais necessidades de projetos convencionais no mercado, este blog projetou dois métodos de saída, um é a saída HDMI e o outro. a outra é a saída 3G -SDI, ambos os métodos exigem a decodificação do vídeo BT1120 para ser convertido em operações de cache de imagem RGB e este design usa o módulo BT1120 para RGB para obter a conversão do formato de vídeo, a arquitetura de cache de imagem VDMA oficial da Xilinx de 2 vias é usada; implementar cache de imagem e cache O meio é DDR3 integrado no lado PS, o primeiro vídeo SDI é gravado em DDR por meio de VDMA e depois lido e enviado para o módulo de sobreposição de fusão de vídeo. através de VDMA, mas é sobreposto através de fusão de vídeo. O módulo lê DDR3. Neste ponto, o vídeo de 2 canais entrou no módulo de fusão e sobreposição de vídeo para processamento de fusão e sobreposição. display, que é o método de saída HDMI; ou o formato de vídeo é realizado através da conversão do módulo RGB para BT1120, então o vídeo entra no núcleo SMPTE SD/HD/3G SDI IP, executa operações de codificação de vídeo SDI e produz vídeo SDI e, em seguida, passa pelos recursos de alta velocidade GTX dentro do FPGA para realizar a conversão de dados paralelos em serial de alta velocidade, que este blog chama de serial, o sinal diferencial de alta velocidade então entra no chip Gv8500 integrado para realizar as funções de conversão diferencial para aprimoramento de driver e de extremidade única. O vídeo SDI é emitido através do soquete BNC da placa de desenvolvimento FPGA e é conectado à caixa SDI para HDMI por meio de um cabo coaxial ao monitor HDMI. 2 conjuntos de códigos-fonte do projeto, como segue:

Os dois conjuntos de códigos-fonte do projeto acima são explicados a seguir para facilitar a compreensão dos leitores:

Código fonte do projeto 1

O modelo FPGA da placa de desenvolvimento é Xilinx–>Xilinx-Zynq7100–xc7z100ffg900-2, há duas fontes de entrada, uma é uma câmera 3G-SDI com resolução de 1920x1080@60Hz e a outra é HDMI para 3G-SDI; caixa é conectada a um laptop. Câmera SDI analógica com resolução de 1920x1080@60Hz; os dois vídeos de entrada são enviados para o FPGA através dos dois chips Gv8601a integrados para obter conversão de extremidade única para equalizador diferencial e balanceado; através dos dois canais GTX, o vídeo SDI é desserializado em dados paralelos; em seguida, passe por 2 canais do núcleo SMPTE SDI IP para decodificar SDI em 2 canais de dados BT1120 e depois passe por 2 canais do módulo BT1120 para RGB para converter BT1120 em RGB888; o vídeo passa por 2 canais do núcleo IP AXI4-Stream oficial da Xilinx para realizar a conversão de dados RGB888 em fluxo de dados AXI4-Stream e, em seguida, o vídeo é gravado no cache DDR3 do lado PS por meio da imagem VDMA oficial da Xilinx de 2 canais; solução de cache; em seguida, o núcleo IP de sobreposição e fusão de vídeo multicanal autodesenvolvido baseado em HLS implementa a operação de fusão e sobreposição de vídeo de 2 canais. Em seguida, insira o núcleo AXI4-Stream To Video Out IP oficial para converter o AXI4-Stream; fluxo de vídeo para o fluxo de vídeo nativo; em seguida, envie o vídeo de sobreposição de fusão para o módulo RGB para HDMI para converter o vídeo RGB888 em vídeo HDMI e a resolução de saída é 1920x1080@60Hz. final do artigo; a imagem é finalmente exibida através de um display HDMI; este projeto requer a execução do soft core Zynq adequado para emenda de vídeo SDI para cenários HDMI;

Código fonte do projeto 2

O modelo FPGA da placa de desenvolvimento é Xilinx–>Xilinx-Zynq7100–xc7z100ffg900-2, há duas fontes de entrada, uma é uma câmera 3G-SDI com resolução de 1920x1080@60Hz e a outra é HDMI para 3G-SDI; caixa é conectada a um laptop. Câmera SDI analógica com resolução de 1920x1080@60Hz; através dos dois canais GTX, o vídeo SDI é desserializado em dados paralelos; em seguida, passe por 2 canais do núcleo SMPTE SDI IP para decodificar SDI em 2 canais de dados BT1120 e depois passe por 2 canais do módulo BT1120 para RGB para converter BT1120 em RGB888; o vídeo, em seguida, passa por 2 canais do núcleo IP AXI4-Stream oficial da Xilinx para realizar a conversão de dados RGB888 em fluxo de dados AXI4-Stream e, em seguida, o vídeo é gravado no cache DDR3 do lado PS por meio da imagem VDMA oficial da Xilinx de 2 canais; solução de cache; em seguida, o núcleo IP de sobreposição e fusão de vídeo multicanal autodesenvolvido baseado em HLS implementa a operação de fusão e sobreposição de vídeo de 2 canais. Em seguida, insira o núcleo AXI4-Stream To Video Out IP oficial para converter o AXI4-Stream; fluxo de vídeo para o fluxo de vídeo nativo; em seguida, envie o vídeo de sobreposição de fusão para o módulo RGB para BT1120 para converter o vídeo RGB888 em vídeo BT1120 e, em seguida, passe o núcleo SMPTE SD /HD/3G SDI IP que codifica o vídeo BT1120 em vídeo SDI; converte dados paralelos SDI em sinais seriais de alta velocidade através dos recursos de alta velocidade GTX dentro do FPGA e, em seguida, usa o chip Gv8500 integrado para implementar a conversão diferencial para driver e terminação única. Após o aprimoramento, a resolução de saída é finalmente 1920x1080@60Hz; , uma caixa SDI para HDMI é usada para conectar a um monitor HDMI para exibição; este projeto requer a execução de soft core Zynq adequado para cenários SDI para SDI;

Este projeto e seu código-fonte incluem partes escritas por mim e partes obtidas de canais públicos na Internet (incluindo CSDN, site oficial da Xilinx, site oficial da Altera, etc.). Se você achar que é ofensivo, envie uma mensagem privada para). criticar e educar com base nisso, este projeto O projeto e seu código-fonte são apenas para estudo pessoal e pesquisa de leitores ou fãs, e estão proibidos de serem usados para fins comerciais se surgirem questões legais do uso comercial pelos próprios leitores ou fãs. , este blog e o blogueiro não têm nada a ver com isso, portanto, use-o com cautela. . .

A página inicial do meu blog tem uma coluna de vídeo SDI, que está cheia de código-fonte de engenharia SDI do codec FPGA e introdução do blog, existem codecs SDI baseados em GS2971/GS2972 e codecs SDI baseados em recursos GTP/GTX; SDI, 6G-SDI, 12G-SDI, etc.; o link do endereço da coluna é o seguinte:

Clique para ir diretamente

Este blog desenvolveu um aplicativo de sobreposição de fusão de vídeo multicanal. Já escrevi um blog especificamente. O link do endereço do blog é o seguinte:

Clique para ir diretamente

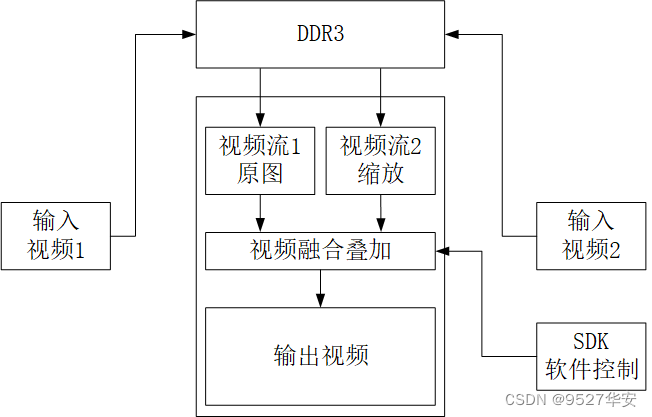

O diagrama de blocos do princípio do design é o seguinte:

Perceber! ! ! !

Perceber! ! ! !

Seta roxa: caminho de saída 3G-SDI

Seta vermelha: caminho de saída HDMI

Existem dois dispositivos de entrada SDI, que são conectados à interface de entrada de vídeo SDI de 2 vias da placa de desenvolvimento FPGA; um deles é uma câmera 3G-SDI com resolução de 1920x1080@60Hz. ser usado por causa deste design É adaptável a três tipos de vídeos SDI; outra caixa HDMI para 3G-SDI, a caixa é conectada a um laptop para simular uma câmera SDI é relativamente cara e amigos com um orçamento limitado podem; considere usar uma caixa HDMI para SDI para simular uma câmera Hezibao custa cerca de 100 yuans. Ao usar uma caixa HDMI para SDI, a fonte de entrada pode ser um laptop, ou seja, usar um laptop para conectar-se à interface de entrada HDMI do; Caixa HDMI para SDI através de um cabo HDMI e, em seguida, use um cabo SDI para conectar a caixa HDMI para SDI. A interface de saída SDI para a placa de desenvolvimento FPGA é a seguinte:

O chip Gv8601a realiza as funções de conversão single-ended para equalizador diferencial e balanceado. O Gv8601a é escolhido aqui porque se baseia na solução oficial da Xilinx. Claro, outros tipos de dispositivos também podem ser usados. O diagrama esquemático do equalizador Gv8601a é o seguinte:

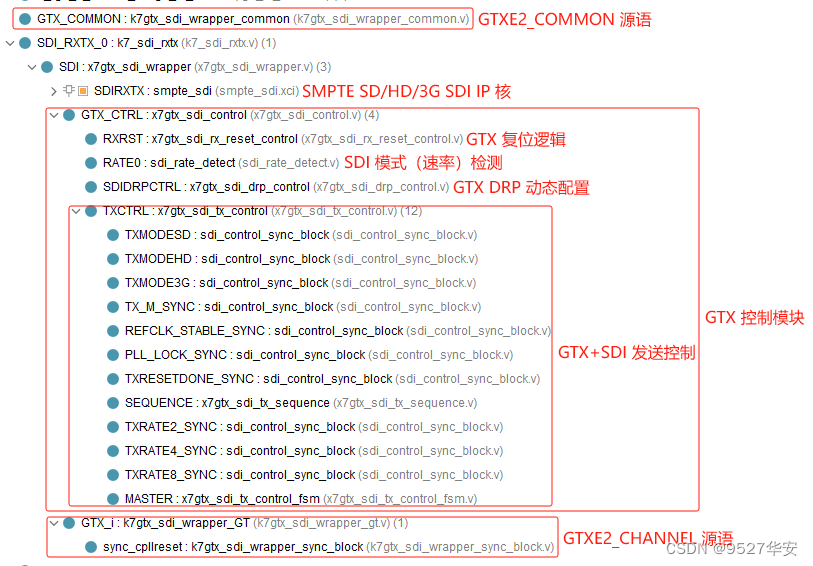

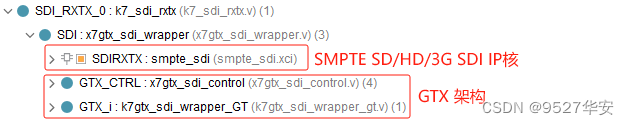

Este design usa os recursos exclusivos de processamento de sinal de alta velocidade GTX da Xilinx para obter a desserialização e serialização de sinais de vídeo diferenciais SDI. Para recepção de vídeo SDI, o GTX desempenha o papel de desserialização, ou seja, decodificar os sinais diferenciais seriais de entrada de alta velocidade em digital paralelo. sinal; para transmissão de vídeo SDI, GTX desempenha o papel de serialização, ou seja, serializar o sinal digital paralelo de entrada em um sinal diferencial serial de alta velocidade, o uso de GTX geralmente requer instanciação do núcleo GTX IP, através do vivado Configure a UI; interface, mas esse design requer identificação automática e processamento adaptativo de vídeos SD-SDI, HD-SDI e 3G-SDI, portanto, GTX precisa ter a função de alterar dinamicamente a taxa de linha. Essa função pode ser configurada por meio da interface DRP. Ele também pode ser configurado por meio da interface de taxa do GTX, portanto, você não pode usar a interface UI do vivado para configuração. Em vez disso, você pode instanciar diretamente os idiomas de origem GTXE2_CHANNEL e GTXE2_COMMON e usar os recursos do GTX diretamente. para configurar dinamicamente a taxa de linha GTX, você também precisa de um módulo de controle GTX, este módulo refere-se ao plano de design oficial da Xilinx e possui as funções de monitoramento dinâmico do modo SDI, configuração dinâmica de DRP, etc.; plano refere-se ao design oficial do Xilinx, a estrutura de código do módulo de desserialização e serialização GTX é a seguinte:

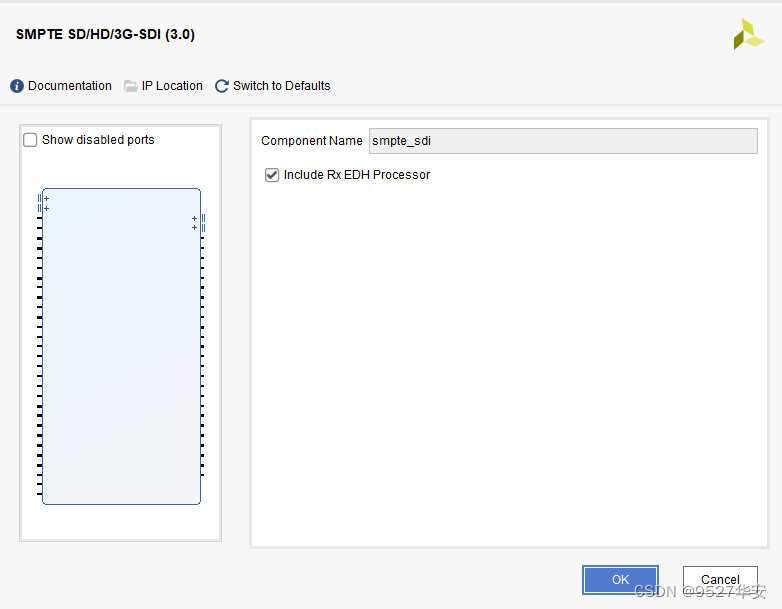

O núcleo SMPTE SD/HD/3G SDI IP é um IP exclusivo para codificação e decodificação de vídeo SDI de FPGAs da série Xilinx. A configuração IP é muito simples de usar.

O núcleo SMPTE SD/HD/3G SDI IP deve ser usado com GTX. Para recepção de vídeo SDI, o IP recebe dados do GTX e, em seguida, decodifica o vídeo SDI na saída de vídeo BT1120. Para transmissão de vídeo SDI, o IP recebe BT1120. dados de vídeo do lado do usuário e, em seguida, codifica o vídeo BT1120 na saída de vídeo SDI; esta solução refere-se ao design oficial da Xilinx; a estrutura de código principal SMPTE SD/HD/3G SDI IP é a seguinte:

A função do módulo BT1120 para RGB é converter a saída de vídeo BT1120 pela decodificação do núcleo SMPTE SD/HD/3G SDI IP em vídeo RGB888. Ele consiste em três módulos: BT1120 para módulo CEA861, módulo YUV422 para YUV444 e YUV444 para RGB888. . Esta solução refere-se ao design oficial do Xilinx, a estrutura de código do módulo BT1120 para RGB é a seguinte:

A solução de cache de vídeo deste design adota a arquitetura de cache de imagem VDMA oficial da Xilinx de 2 canais; o meio de cache é DDR3 do lado PS, o primeiro vídeo SDI é gravado em DDR por meio de VDMA e depois lido e enviado para o módulo de sobreposição de fusão de vídeo; O segundo vídeo SDI Depois de gravar em DDR por meio de VDMA, ele não é lido, mas é lido em DDR3 por meio do módulo de sobreposição de fusão de vídeo. Tomando o código-fonte do projeto 1 como exemplo, o VDMA é projetado usando o Block Design do Xilinx. vivado, conforme mostrado abaixo:

Para reduzir a latência, o VDMA é configurado para armazenar em cache 1 quadro, da seguinte forma:

O diagrama de blocos do projeto de sobreposição de fusão de vídeo multicanal é o seguinte:

A fusão e sobreposição de vídeo multicanal é formada pela fusão e superposição do vídeo subjacente e do vídeo de sobreposição. O vídeo subjacente é o vídeo de entrada do primeiro canal, e o vídeo de sobreposição é o vídeo dimensionado do segundo canal. os vídeos são fundidos e produzidos, o que pode ser O software SDK configura dinamicamente a transparência da fusão de vídeo de 2 canais, o tamanho do zoom do vídeo sobreposto, a posição de exibição do vídeo sobreposto e outras informações o design é implementado usando o; Código C++ da solução HLS, e é sintetizado em RTL e encapsulado em IP, que pode ser usado em vivado Ligue para o IP. Para obter detalhes sobre esta solução, consulte meu blog anterior. O link do blog é o seguinte:

Clique para ir diretamente

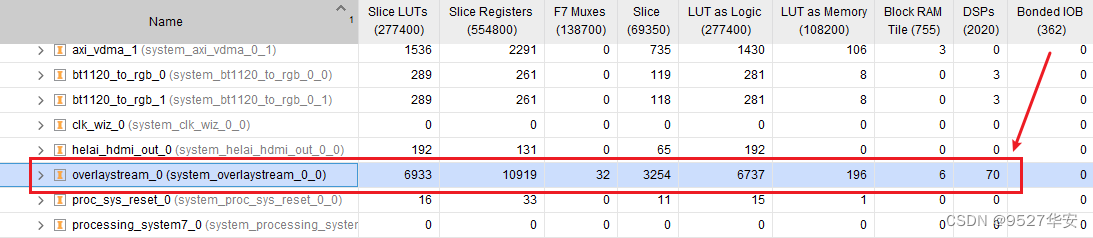

O uso abrangente de recursos deste IP em vivado é o seguinte:

A sobreposição de fusão de vídeo multicanal HLS precisa executar o driver e o programa do usuário no SDK para funcionar corretamente. Forneci um programa em linguagem C no projeto, consulte o código-fonte do projeto para obter detalhes na captura de tela do multicanal HLS; a chamada de sobreposição de fusão de vídeo do canal é a seguinte:

A arquitetura de saída de vídeo HDMI é a seguinte:

Referindo-se ao design oficial da Xilinx, use a arquitetura VTC + AXI4-Stream To Video Out para converter o vídeo de saída do formato AXI4-Stream para o formato nativo, em seguida, use o módulo RGB888 para HDMI implementado em código verilog puro para converter RGB888 para HDMI e, finalmente, exibir; através do monitor, a estrutura de código do módulo RGB888 para HDMI é a seguinte:

Em relação ao módulo RGB888 para HDMI, consulte meu blog anterior, endereço do blog:Clique para ir diretamente

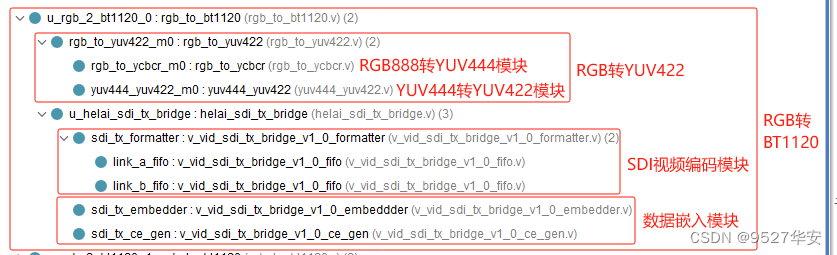

A arquitetura de saída de vídeo SDI deve primeiro converter o AXI4-Stream lido pelo VDMA para o formato nativo. Depois de obter o vídeo RGB888, ele pode então converter o vídeo RGB para BT1120 para BT1120.

No modo de saída SDI, o clock de pixel do módulo de temporização VGA é fornecido pelo clock do usuário de envio do núcleo SMPTE SD/HD/3G SDI IP. O clock de pixel é diferente em diferentes modos SDI. , o clock do pixel é de 148,5M. No modo HD-SDI 720P@60Hz, o clock do pixel é de 74,25M;

No modo de saída SDI, o módulo RGB para BT1120 precisa ser usado; a função do módulo RGB para BT1200 é converter o vídeo RGB do lado do usuário em vídeo BT1200 e enviá-lo para o SMPTE SD/HD/3G SDI IP. núcleo; o módulo RGB para BT1120 consiste em um módulo RGB888 para YUV444, módulo YUV444 para YUV422, módulo de codificação de vídeo SDI e módulo de incorporação de dados. Esta solução refere-se ao design oficial do Xilinx; do seguinte modo:

Estas duas partes partilham os módulos correspondentes com o processo de recepção, que são funcionalmente o processo inverso do processo de recepção e não serão descritos novamente;

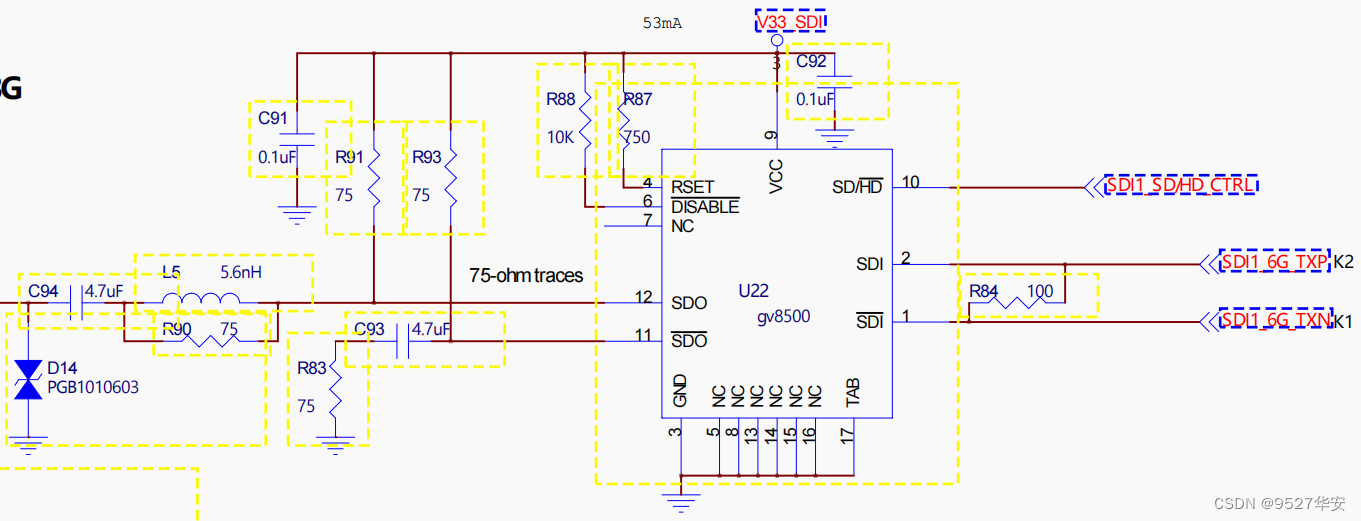

O chip Gv8500 realiza as funções de conversão diferencial para driver single-ended e aprimorado. O Gv8500 é escolhido aqui porque se baseia na solução oficial da Xilinx. É claro que outros tipos de dispositivos também podem ser usados. O diagrama esquemático do driver Gv8500 é o seguinte:

No modo de saída SDI, você precisa usar uma caixa SDI para HDMI, porque o monitor em minhas mãos não possui uma interface SDI, apenas uma interface HDMI. Para exibir vídeo SDI, isso só pode ser feito. seu monitor tem uma interface SDI, você pode diretamente A conexão mostra que minha caixa SDI para HDMI foi comprada em uma determinada loja por menos de 100 yuans;

Este blog fornece 2 conjuntos de códigos-fonte do projeto. Tomando o código-fonte do projeto 1 como exemplo, o design do Vivado Block Design é o seguinte. O design do Block Design faz parte da arquitetura do cache de imagem:

Tomando o código-fonte do projeto 1 como exemplo, a estrutura do código-fonte do projeto é a seguinte:

O clock lateral PL do código-fonte do projeto é fornecido pelo soft core do Zynq, portanto, o SDK precisa ser executado para iniciar o Zynq. Além disso, os núcleos IP, como sobreposição de fusão de vídeo e VDMA, precisam executar drivers de software para funcionar corretamente. A estrutura do código do software SDK é a seguinte:

A configuração no código SDK é a seguinte, os usuários podem modificá-lo arbitrariamente de acordo com suas próprias necessidades;

O primeiro vídeo é o vídeo da camada inferior com resolução de 1920x1080;

O vídeo do segundo canal é o vídeo de sobreposição com resolução de 1920x1080. Pegue uma área de 1000x800 das coordenadas do vídeo de sobreposição (400, 200) como origem do vídeo de fusão de sobreposição;

Dimensione o vídeo de fusão de sobreposição de 600x600 obtido na etapa anterior para 960x540;

Sobreponha o vídeo de fusão sobreposto de 960x540 na etapa anterior, começando na coordenada (0,0) do vídeo subjacente e defina a transparência das camadas subjacentes e de sobreposição para 80;

Modelo FPGA da placa de desenvolvimento: Xilinx-Zynq7100 – xc7z100ffg900-2;

Ambiente de desenvolvimento: Vivado2019.1;

Entrada: câmera 3G-SDI ou caixa HDMI para SDI, resolução 1920x1080@60Hz;

Saída: HDMI, resolução 1920x1080@60Hz;

Solução de cache: solução VDMA oficial da Xilinx;

Mídia de cache: DDR3 do lado PS;

Solução de fusão e sobreposição de vídeo: fusão e sobreposição de vídeo multicanal autodesenvolvida com base em HLS;

Função do projeto: O objetivo deste projeto é permitir que os leitores dominem os recursos de design do FPGA da série Zynq para implementar SDI para HDMI, para que possam transplantar e projetar seus próprios projetos;

Para design de bloco de projeto e arquitetura de código de projeto, consulte a seção "Arquitetura de código-fonte do projeto" no Capítulo 3;

O consumo de recursos e consumo de energia do projeto são os seguintes:

Modelo FPGA da placa de desenvolvimento: Xilinx-Zynq7100 – xc7z100ffg900-2;

Ambiente de desenvolvimento: Vivado2019.1;

Entrada: câmera 3G-SDI ou caixa HDMI para SDI, resolução 1920x1080@60Hz;

Saída: 3G-SDI, resolução 1920x1080@60Hz;

Solução de cache: solução VDMA oficial da Xilinx;

Mídia de cache: DDR3 do lado PS;

Solução de fusão e sobreposição de vídeo: fusão e sobreposição de vídeo multicanal autodesenvolvida com base em HLS;

Função do projeto: O objetivo deste projeto é permitir que os leitores dominem os recursos de design do FPGA da série Zynq para implementar SDI para HDMI, para que possam transplantar e projetar seus próprios projetos;

Para design de bloco de projeto e arquitetura de código de projeto, consulte a seção "Arquitetura de código-fonte do projeto" no Capítulo 3;

O consumo de recursos e consumo de energia do projeto são os seguintes:

1: Se a sua versão vivado for consistente com a versão vivado deste projeto, abra o projeto diretamente;

2: Se a sua versão vivado for inferior à versão vivado deste projeto, você precisa abrir o projeto e clicar em Arquivo -> Salvar como, porém este método não é seguro. desta versão do projeto ou superior;

3: Se a sua versão vivado for superior à versão vivado deste projeto, a solução é a seguinte:

Após abrir o projeto, você descobrirá que os IPs estão bloqueados, conforme segue:

Neste momento, você precisa atualizar o IP. As etapas são as seguintes:

Se o seu modelo FPGA for inconsistente com o meu, você precisará alterar o modelo FPGA da seguinte forma:

Após alterar o modelo FPGA, você precisa atualizar o IP. O método de atualização do IP foi descrito anteriormente;

1: Como o DDR de cada placa não é necessariamente o mesmo, o IP MIG precisa ser configurado de acordo com seu próprio diagrama esquemático. Você pode até excluir diretamente o MIG do meu projeto original e adicionar novamente o IP e reconfigurá-lo;

2: Modifique as restrições dos pinos de acordo com seu próprio diagrama esquemático e modifique-o no arquivo xdc;

3: O transplante de FPGA puro para Zynq requer a adição de soft core zynq ao projeto;

O equipamento que precisa ser preparado é o seguinte:

Placa de desenvolvimento FPGA;

Câmera SDI ou caixa HDMI para SDI;

Caixa SDI para HDMI;

Tela HDMI;

Minha placa de desenvolvimento está conectada da seguinte forma:

Tomando o código-fonte 1 do projeto como exemplo, a saída é a seguinte:

Sobreposição de fusão Zynq-SDI-Video

Bônus: Aquisição de código de engenharia

O código é muito grande e não pode ser enviado por e-mail. Ele será enviado por meio de um determinado link de disco de rede.

Como obter informações: em particular, ou o cartão de visita V no final do artigo.

As informações do disco de rede são as seguintes:

Além disso, muitos amigos deram muitas opiniões e sugestões a este blogueiro, na esperança de enriquecer o conteúdo e as opções do serviço. Como amigos diferentes têm necessidades diferentes, este blogueiro também oferece os seguintes serviços: