2024-07-12

한어Русский языкEnglishFrançaisIndonesianSanskrit日本語DeutschPortuguêsΕλληνικάespañolItalianoSuomalainenLatina

In praesenti, duae solutiones sunt pro FPGA ad efficiendum SDI video modum translitterandi et decoctionis: una utendum est decisis decisis et decoctionis aptis, ut receptator typicus GS2971, et transfusor GS2972. Utilitas est simplicitas decodes SDI in parallelas YCrCb422, et GS2972 transmittit Fabrica directe encodes parallelum YCrCb422 in SDI video. Incommodum est quod sumptus est relative altum Facultas logica FPGA ad efficiendum SDI modum describendi et decocendi et utendi GTP/GTX facultatum seriei Xilinx FPGA facultates rationabiliter adhibentur et facultates GTP/GTX frustra non sunt adhibitae. Incommodum est quod operatio difficilior est et altior technica FPGA tincidunt requirit. Interestingly, hae duae solutiones respondentes solutiones in hoc diario hic habent, inter ferramenta FPGA tabularum evolutionis, codicem ipsum fontem, etc.

Hoc consilium in Zynq7100 FPGA evolutionis tabula seriei Zynq fundatum est ad efficiendum SDI video modum translitterandi et decoctionis + imaginis scalae + multi-alvei video splicing. 60Hz, et HD-SDI etiam camera Vel SD-SDI adhiberi potest, quia hoc consilium adaptavit tribus SDI videos; SDI videos connectuntur FPGA ad tabulam evolutionis per retinacula coaxiales BNC nervum, et tunc video coaxialem per onboard Gv8601a chip ad cognoscendas functiones conversionis unius finitae ad differentialem et libratam EQ; summus celeritas subsidii intra FPGA ad cognoscendum altum celeritatem Vide ad conversionem parallelam datarum. Bo vocat deserializationem; video decoding operationem et video BT1120 output. Hic, SDI operatio video decoding confecta est et exercitationes imaginis processus operationes praestare potes;

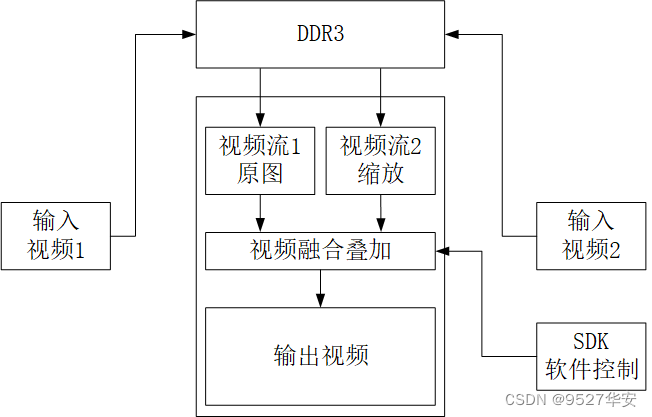

Propositum huius designationis est SDI videre decoded output cum multi-alvei imaginis scandere + videndi fusionem et superpositionem. alia est 3G -SDI output, utraque methodus decoctionis BT1120 requiret ut RGB et imaginis operationes caching convertantur; instrumentum imaginis caching et caching Medium est in navi PS-DDR3 latus; primum video SDI ad DDR per VDMA scriptum est et deinde ad fusionem laminis moduli emissae legit per VDMA, sed obducitur per fusionem video. Modulus legit ab DDR3. Hic, canalis 2 videndi fusione et obduces moduli ad fusionem et processus obduces ingreditur; ostensio, quae est methodus extrahendi HDMI; vel forma visibilis per RGB ad BT1120 conversionis moduli efficitur, tunc SMPTE SD/HD/3G SDI IP nucleus ingreditur, operationes translitterandi ac SDI video operationes SDI facit, ac deinde per GTX altae celeritatis subsidia intra FPGA transit ut cognoscat conversionem notitiarum parallelarum ad celeritatem Vide, quam hoc blog vocat Vide, signum differentiale summus velocitatis tunc ingreditur in navi Gv8500 chip ut cognoscat functiones conversionis differentialis ad Singula finita et amplificatio auriga 2 Propositiones codicis exstent principium, hoc modo:

In binis suprascriptis codicibus fonte projecti haec explicantur ad intellegentiam faciliorem lectorum:

Code Project source 1

Exemplar FPGA progressionis tabulae est Xilinx->Xilinx-Zynq7100-xc7z100ffg900-2; Arca cum laptop coniungitur. Analog SDI camera cum resolutione 1920x1080@60Hz; per duos GTX canales, SDI video in data parallela deseriatur; deinde per 2 nucleos SMPTE SDI IP core ad decode SDI in 2 ductus notitiarum BT1120; video; deinde per 2 canales officialis Xilinx Video In Ad AXI4-Fream IP core percipere RGB888 datam ad AXI4-Stream datam conversionem amnis; solutionem cache; dein multi-alvei video fusionis auto-excultae et IP nucleum obduces secundum operas 2-alvei video fusionis et obducendi operationem Xilinx intrant; video rivum ad Natalem video fluentum; tunc mitte fusionem deauratam video ad RGB ad HDMI moduli ut convertat RGB888 video ad HDMI video et output resolutio Est 1920x1080@60Hz finis articuli;

Code Project source 2

Exemplar FPGA progressionis tabulae est Xilinx->Xilinx-Zynq7100-xc7z100ffg900-2; Arca cum laptop coniungitur. Analog SDI camera cum resolutione 1920x1080@60Hz; per duos GTX canales, SDI video in data parallela deseriatur; deinde per 2 nucleos SMPTE SDI IP core ad decode SDI in 2 ductus notitiarum BT1120; video; deinde per 2 canales officialis Xilinx Video In Ad AXI4-Fream IP core percipere RGB888 datam ad AXI4-Stream datam conversionem amnis; solutionem cache; dein multi-alvei video fusionis auto-excultae et IP nucleum obduces secundum operas 2-alvei video fusionis et obducendi operationem Xilinx intrant; video rivum ad Natalem video rivum; conversis SDI parallelis data in celeritatem Vide significationibus per GTX altae celeritatis subsidia intra FPGA; et deinde utitur in navi Gv8500 chip ad conversionem differentialem efficiendi ad simplices exactores et post amplificationem, propositio resolutio est 1920x1080@60Hz; ;

Hoc consilium eiusque fons codicem includunt utrasque partes a me ipso scriptas et partes a meatibus publicis in Interreti impetratas (including CSDN, Xilinx officiali, Alterum officiale, etc.). reprehendere et erudire; in hoc, hoc project Project et eius fons codice solum ad personalem studium et inquisitionem a legentibus vel alits sunt, et prohibentur quominus ad usum mercatorum accedant , hoc diarium et blogger nihil ad rem habent, eo cauto utere. . .

Pagina mea blog in columna video SDI habet, quae plena est FPGA codec SDI machinalis source code et introductio diarii; SDI, 6G-SDI, 12G-SDI, etc.;

Click ut directe

Hoc blog auto-evolutum a multi- canali video fusione laminis applicationis. Scripsimus in specie ante blog.

Click ut directe

Consilium principale clausus diagramma talis est:

Animadverte! ! ! !

Animadverte! ! ! !

Purpura sagitta: 3G-SDI output path

Red arrow: HDMI output path

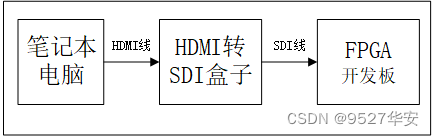

Duae SDI machinis inputatae sunt, quae cum 2-modo SDI video initus interfacies tabularum FPGA evolutionis connexae sunt; ob hoc consilio utendum est Ad tria genera videos SDI accommodata; alterum HDMI ad 3G-SDI cistam, capsa iuncta cum laptop ad cameram SDI simulandam; considera utendo HDMI ad SDI capsam ad cameram SDI simulandam. Hezibao constat circa 100 Yuan; cum HDMI ad SDI arca utens, principium initus esse potest laptop, hoc est, laptop coniungere ad HDMI input interfaciem ipsius; HDMI ad SDI cistam per funem HDMI, tum utere funem SDI ad capsam HDMI ad SDI applicandam. SDI output interfacies ad tabulam FPGA evolutionis hoc modo est;

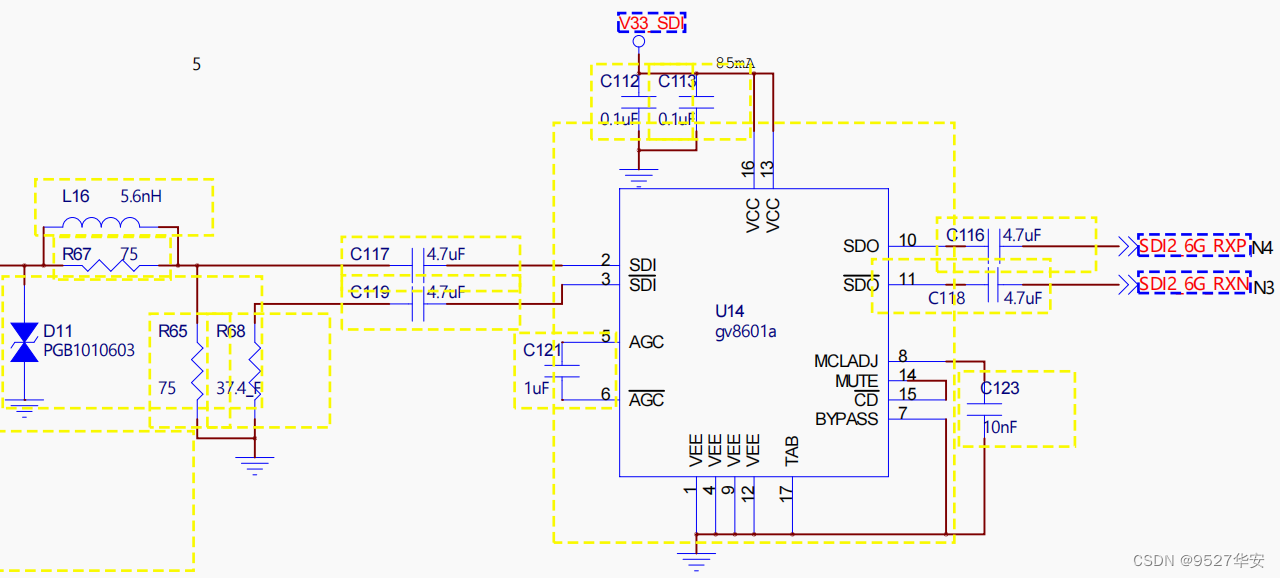

Gv8601a chip cognoscit functiones conversionis simplicis finitae ad differentialem et temperatam EQ. Gv8601a hic eligitur quia solutionem officialem Xilinx haurit. Schematicum schematicum Gv8601a aequatoris est talis:

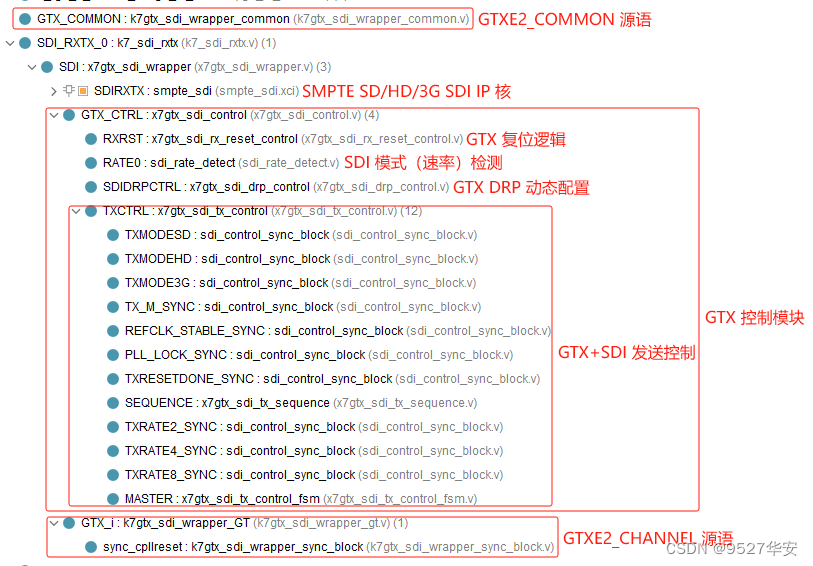

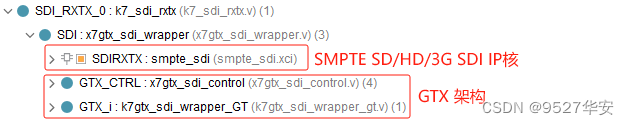

Hoc consilio utitur Xilinx singulari GTX summus velocitatis signo processus facultates ad deserializationem et serializationem SDI differentialium video significationum. signum; pro SDI video transmissione, GTX agit munus serializationis, hoc est, initus digitalis paralleli serialis in signo differentiali Vide magni velocitatis; interfacies, sed hoc consilium postulat identitatem automatariam ac adaptivam processui SD-SDI, HD-SDI et 3G-SDI videos, ita GTX debet habere munus dynamice mutandi lineam rate. Configurari etiam potest per interventus GTX, ut UI vivado ad configurationem uti non possis. Sed protinus instantia GTXE2_CHANNEL et GTXE2_ COMMUNE fons linguarum GTX ac GTX opibus directe utere. ut dynamice GTX lineam ratem configuret, moduli moderaminis GTX etiam opus est, cuius moduli consilium officialem Xilinx refert, et functiones dynamicae vigilantiae SDI modi, dynamicae schematismi DRP, etc Consilium de consilio officiali Xilinx refertur;

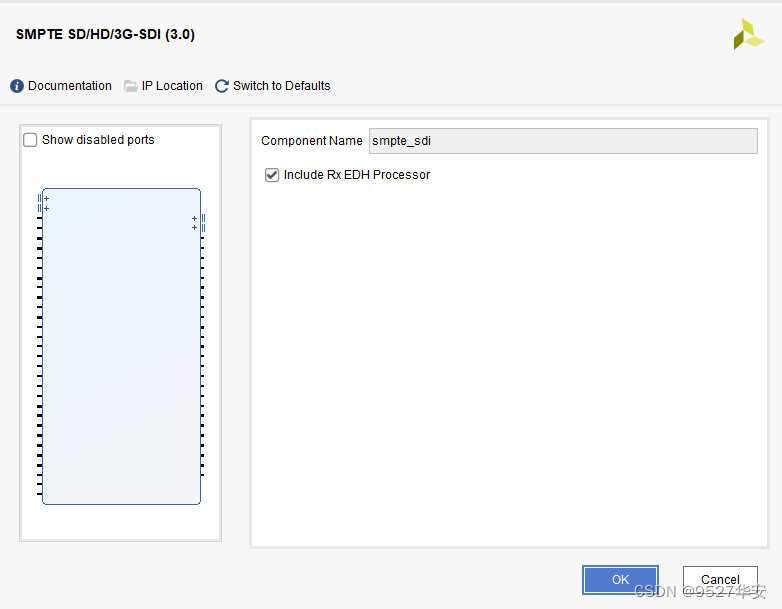

SMPTE SD/HD/3G SDI IP nucleus singularis est IP pro SDI video descriptam et decoctionem seriei Xilinx FPGAs.

SMPTE SD/HD/3G SDI IP nucleus adhibendus est cum GTX. Pro SDI video receptione, IP notitia ex GTX accipit, et tunc SDI video in BT1120 output decedit video datam ex parte utentis, et deinde in modum video BT1120 in SDI output video;

Munus moduli BT1120 ad RGB est convertendi BT1120 output ab SMPTE SD/HD/3G SDI IP core decoding in RGB888 video. Constat tribus modulis: BT1120 ad CEA861 moduli, YUV422 ad YUV444 moduli, et YUV444 ad RGB888 . Haec solutio ad Consilium officiale Xilinx adhibitum est;

Vide cache solutionem huius designationis adoptat 2 alveum Xilinx officialis VDMA imaginem cache architectura; Secundum SDI video Postquam scribens ad DDR per VDMA, non recitatur, sed ex DDR3 per fusionem laminis moduli video vivado, ut infra;

Ad latencym redigendum, VDMA ad tabulam 1 caches posita, hoc modo:

Multi-canali video fusione deauratium designationis obstructionum schematis sic est:

Multi-canale video fusione et obduces formatur ex fusione et superpositione videoi subiectae et video operimentorum videos simul conflantur et output, quae possunt esse Software SDK dynamice configurat perspicuitatem fusionis videndi 2 canali, zoom magnitudine video obductio, ostentatio positio de laminis et aliis informationibus; HLS solutionis C++ codicem, et in RTL constringitur et in IP encapsulatur, quod in vivado Voca IP adhiberi potest. Singula de hac solutione, quaeso, ad priorem blogum referendum est.

Click ut directe

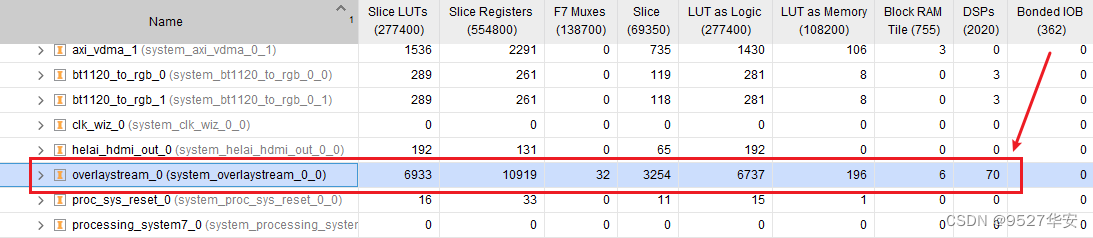

Facultas comprehensiva huius IP usus in vivado talis est:

HLS multi-alvei video fusione obductos necessarios ad currendum aurigae et programmatis usoris in SDK ad recte operandum. Ego programmata linguae C in incepto proposui, quaeso referre ad principium e codice pro details; canalis video fusione lamminis vocationis talis est;

HDMI architectura video output hoc est:

Referendo ad Xilinx officialem designandum, utere VTC+AXI4-Stream Ad Video Ex architectura ut output video ab AXI4-Stream ad formam Nativam convertendo; ea per monitorem, RGB888 ad HDMI moduli codicis structuram talis est:

Quoad RGB888 ad HDMI modulum, quaeso referre ad blog priorem meam, inscriptionem blog:Click ut directe

SDI architectura video output primum AXI4-Stream ab VDMA in formatam Nativam convertendam debet.

In SDI output modo, pixel horologium moduli timidi VGA praebetur a mittendo horologium SMPTE SD/HD/3G SDI IP nucleum pixel horologium 148.5M.

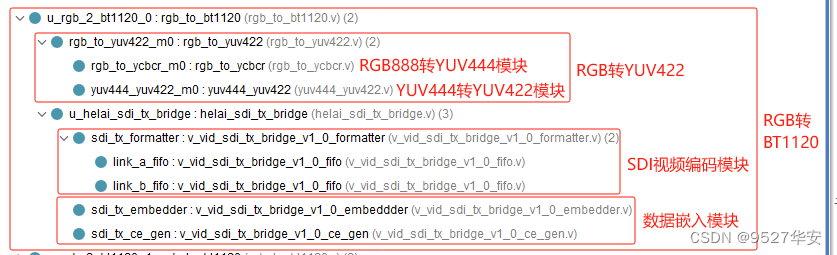

In SDI output modo, RGB ad BT1120 moduli utendum est; functio RGB ad BT1200 moduli est RGB video in parte utentis in BT1200 convertendi et ad SMPTE SD/HD/3G SDI IP coro; sic:

Hae duae partes correspondentes moduli cum processu recipienti communicant, qui officiatorie processus e contrario processus recipiendi sunt nec iterum describentur;

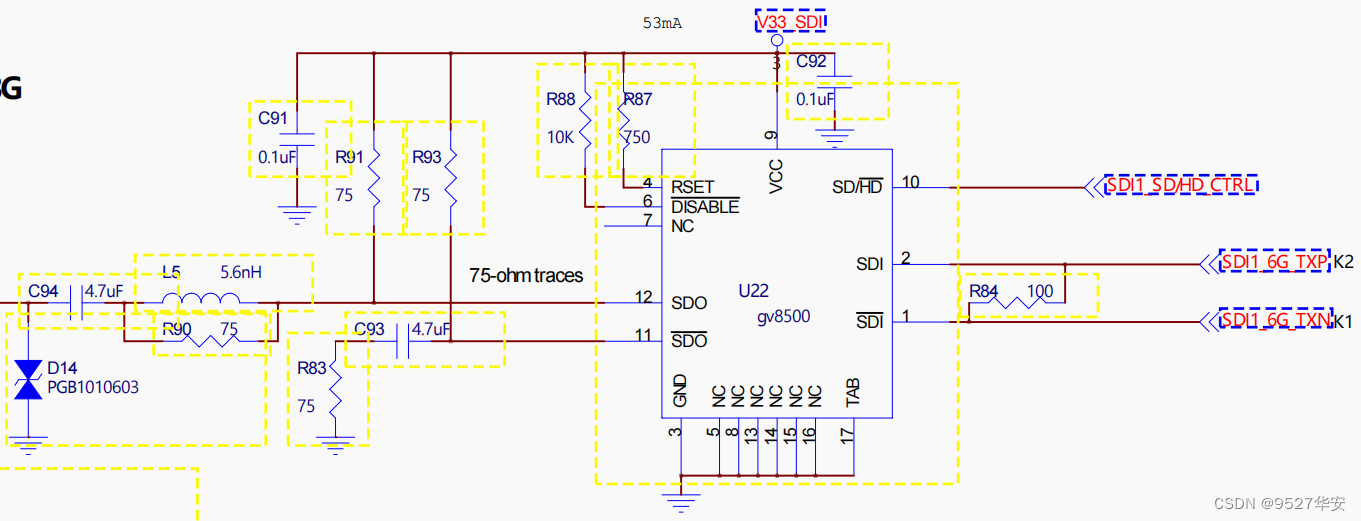

Chirographum Gv8500 cognoscit functiones conversionis differentialis ad unum-extremum et auctum agitatorem. Schematicum schematis rectoris Gv8500 est hoc modo:

In SDI output modum, debes uti arca SDI ad HDMI, quia monitor in manu mea non habet interfacem SDI, solum HDMI interface monitor tuus interface SDI habet, te directo Connexio ostendit quod arca mea SDI ad HDMI empta est in quadam copia pro minus quam 100 Yuan;

This blog providet 2 sets of project source code.

Cum exstent principium in codice 1 ut exemplum, fons documenti structurae codicis haec est.

In PL lateris horologii documenti fons codici a Zynq nucleo molli providetur, ergo SDK debet currere ut Zynq committitur. In addition, IP coros ut video fusione laminis et VDMA opus est ut rectoribus programmatibus ad bene operandum SDK structura programmatis haec est:

Configuratio in codice SDK talis est, utentes eam ad libitum iuxta necessitates suas mutare possunt;

Primum video esse fundum tabulatum video cum resolutione 1920x1080;

Alter canalis video video obduces cum resolutione 1920x1080. Sume area 1000x800 ex coordinatis video coordinatis (400, 200) ut origo sicut fusione laminis video;

Ascendite 600x600 fusionem obduces videndi consecuti in priori gradu ad 960x540;

Fusionem videndi superimpositam indue 960x540 in gradu priori ab (0,0) coordinatam video subiectae, et pone pellucentiam stratorum stratorum substratae et obduces ad 80;

Exemplar progressionis tabulae FPGA: Xilinx-Zynq7100-xc7z100ffg900-2;

Progressio ambitus: Vivado2019.1;

Input: 3G-SDI camera vel HDMI ad capsam SDI, resolutio 1920x1080@60Hz;

Output: HDMI, resolutio 1920x1080@60Hz;

Caching solution: Xilinx officialis VDMA solutio;

Cache media: PS latus DDR3;

Vide fusionem et solutionem obduces: auto-exculta multi- canali video fusione et obduces secundum HLS;

Propositum munus: Propositum huius consilii est ut lectores permittat consilium facultatum Zynq seriei FPGA permittere ad efficiendum SDI ad HDMI, ut incepta sua transferre et designare possint;

Pro project Block Design and project code architectura, placere ad "Project Source Code Architecture" section in Caput III;

Subsidium consumptio et consumptio consilii in potestate sunt haec:

Exemplar progressionis tabulae FPGA: Xilinx-Zynq7100-xc7z100ffg900-2;

Progressio ambitus: Vivado2019.1;

Input: 3G-SDI camera vel HDMI ad capsam SDI, resolutio 1920x1080@60Hz;

Output: 3G-SDI, resolutio 1920x1080@60Hz;

Caching solution: Xilinx officialis VDMA solutio;

Cache media: PS latus DDR3;

Vide fusionem et solutionem obduces: auto-exculta multi- canali video fusione et obduces secundum HLS;

Propositum munus: Propositum huius consilii est ut lectores permittat consilium facultatum Zynq seriei FPGA permittere ad efficiendum SDI ad HDMI, ut incepta sua transferre et designare possint;

Pro project Block Design and project code architectura, placere ad "Project Source Code Architecture" section in Caput III;

Subsidium consumptio et consumptio consilii in potestate sunt haec:

1: Si versio vivado consonat cum vivado huius propositi versio, propositum directe aperi;

2: Si versio vivado tua inferior est quam versio vivado huius propositi, opus est tabulam aperire et deprime -> Serva Ut, haec methodus tutissima non est rei literae.

3: Si versio vivado altior est quam versio vivado propositi huius, solutio haec est:

Post propositum aperiens, IPS clausas invenies, hoc modo:

Hoc tempore, opus IP upgrade sunt.

Si exemplar tuum FPGA cum meo repugnat, debes exemplum FPGA mutare ut sequitur:

Exemplar FPGA mutato, opus est ut IP upgrade.

1: Cum DDR cuiusque tabulae prorsus idem non sit, MIG IP configurari debet secundum tuum schematicum schematicum.

2: clavum angustiis temperare iuxta schematicum tuum schematicum et in xdc fasciculi modificare;

3: Transplantatio pura FPGA ad Zynq requirit addito zynq nucleo mollis ad exertum;

Apparatus paratus talis est:

FPGA explicatio tabulae;

SDI camera vel HDMI ad capsam SDI;

SDI ad arca HDMI;

HDMI propono;

Meam tabulam evolutionis ita connexam est:

In exposito fonte codice 1 ut exemplum, output hoc est:

Zynq-SDI-Video eget Overlay

Bonus: Acquisitionem ipsum codice

Codex nimis magnus est et ab electronico mitti non potest. In retiaculis retis ligamentum quoddam mittetur.

Quam rem habere privatim, seu V negotium in fine articuli.

A network orbis notitia talis est:

Praeterea multi amici hunc blogger multam opiniones et suggestiones dederunt, sperantes munus contentum et optiones ditare.