Mi informacion de contacto

Correo[email protected]

2024-07-12

한어Русский языкEnglishFrançaisIndonesianSanskrit日本語DeutschPortuguêsΕλληνικάespañolItalianoSuomalainenLatina

Actualmente, existen dos soluciones para que FPGA implemente la codificación y decodificación de video SDI: una es usar chips de codificación y decodificación dedicados, como el receptor típico GS2971 y el transmisor GS2972. La ventaja es la simplicidad, por ejemplo, el receptor GS2971 directamente. decodifica SDI en YCrCb422 paralelo y el GS2972 transmite. El dispositivo codifica directamente el YCrCb422 paralelo en video SDI. La desventaja es que el costo es relativamente alto. Puede buscar los precios de GS2971 y GS2972 en Baidu. Departamento de recursos lógicos FPGA para implementar la codificación y decodificación SDI y utilizar los recursos GTP/GTX de la FPGA de la serie Xilinx Para lograr la deserialización, utilice los recursos SMPTE SDI de la FPGA de la serie Xilinx para implementar la codificación y decodificación SDI. Los recursos se utilizan razonablemente y los recursos GTP/GTX no se utilizan en vano. La desventaja es que la operación es más difícil y requiere un mayor nivel técnico de los desarrolladores de FPGA. Curiosamente, estas dos soluciones tienen soluciones correspondientes aquí en este blog, incluidas placas de desarrollo de hardware FPGA, código fuente de ingeniería, etc.

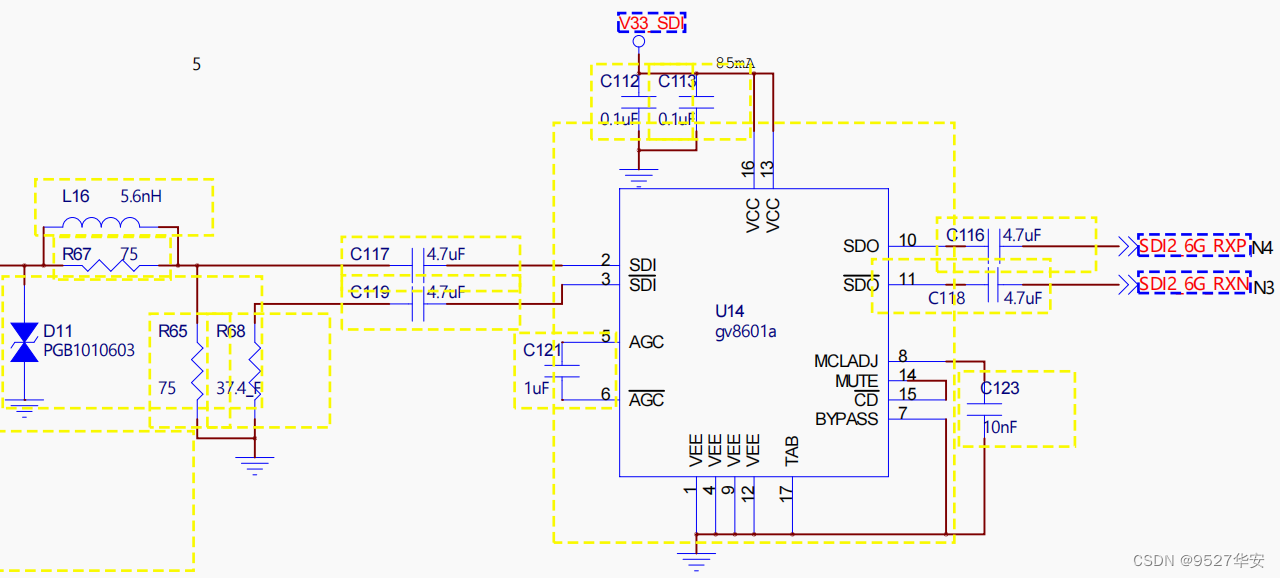

Este diseño se basa en la placa de desarrollo FPGA Zynq7100 de la serie Zynq para implementar codificación y decodificación de video SDI + escalado de imagen + empalme de video multicanal. Hay dos fuentes de entrada, una es una cámara 3G-SDI con una resolución de 1920x1080 @. 60 Hz y también se puede utilizar HD-SDI o cámara SD-SDI, porque este diseño se adapta a tres vídeos SDI y otra caja HDMI a 3G-SDI, la caja se conecta a una computadora portátil para simular las dos entradas; Los videos SDI se conectan a la placa de desarrollo FPGA a través del conector BNC del cable coaxial, y luego el video coaxial pasa a través del chip Gv8601a integrado para realizar las funciones de conversión de un solo extremo a EQ diferencial y balanceado, luego la señal de video SDI diferencial ingresa a la GTX; recurso de alta velocidad dentro de la FPGA para realizar la conversión de datos de serie a paralelo de alta velocidad. Bo lo llama deserialización, luego el video paralelo deserializado se envía al núcleo IP SMPTE SD/HD/3G SDI exclusivo de la FPGA de la serie Xilinx para realizar SDI. operación de decodificación de video y salida de video BT1120 En este punto, la operación de decodificación de video SDI se ha completado y puede realizar operaciones de procesamiento de imágenes de rutina;

El propósito de este diseño es generar video SDI decodificado después del escalado de imagen + fusión y superposición de video multicanal. En respuesta a las necesidades de proyectos actuales en el mercado, este blog ha diseñado dos métodos de salida, uno es salida HDMI y el otro. es salida 3G-SDI, ambos métodos requieren decodificar el video BT1120 para convertirlo a RGB y operaciones de almacenamiento en caché de imágenes; este diseño utiliza el módulo BT1120 a RGB para lograr la conversión de formato de video para implementar la arquitectura de caché de imágenes VDMA oficial de Xilinx bidireccional; almacenamiento en caché de imágenes y almacenamiento en caché El medio está integrado en DDR3 del lado PS; el primer video SDI se escribe en DDR a través de VDMA y luego se lee y se envía al módulo de superposición de fusión de video. El segundo video SDI no se lee después de escribirse en DDR a través. VDMA, pero se superpone mediante fusión de video. El módulo lee desde DDR3. En este punto, el video de 2 canales ha ingresado al módulo de fusión y superposición de video para el procesamiento de fusión y superposición. , que es el método de salida HDMI; o el formato de video se realiza a través de la conversión del módulo RGB a BT1120, luego el video ingresa al núcleo IP SMPTE SD/HD/3G SDI, realiza operaciones de codificación de video SDI y emite video SDI, y luego pasa a través de los recursos de alta velocidad GTX dentro de la FPGA para realizar la conversión de datos paralelos a serie de alta velocidad, que este blog llama serie, la señal diferencial de alta velocidad luego ingresa al chip Gv8500 integrado para realizar las funciones de conversión diferencial a única -Mejora del controlador y del terminal. El video SDI se emite a través del conector BNC de la placa de desarrollo FPGA y se conecta a la caja SDI a HDMI a través de un cable coaxial a la pantalla HDMI. Este es el método de salida SDI que proporciona este blog. conjuntos de códigos fuente del proyecto, como sigue:

Los dos conjuntos de códigos fuente del proyecto anteriores se explican a continuación para facilitar la comprensión de los lectores:

Código fuente del proyecto 1

El modelo FPGA de la placa de desarrollo es Xilinx–>Xilinx-Zynq7100–xc7z100ffg900-2. Hay dos fuentes de entrada, una es una cámara 3G-SDI con una resolución de 1920x1080@60Hz y la otra es HDMI a 3G-SDI; caja La caja está conectada a una cámara SDI analógica con una resolución de 1920x1080@60Hz; los dos videos de entrada se envían a la FPGA a través de los dos chips Gv8601a integrados para lograr una conversión de extremo único a ecualizador diferencial y balanceado; a través de los dos canales GTX, el vídeo SDI se deserializa en datos paralelos. Luego, a través de 2 canales del núcleo IP SMPTE SDI, el SDI se decodifica en 2 canales de datos BT1120 y luego, a través de 2 canales de BT1120 al módulo RGB, el BT1120 se convierte; en video RGB888 y luego a través de 2 canales de entrada de video oficial de Xilinx al núcleo IP AXI4-Stream para realizar la conversión de datos RGB888 a flujo de datos AXI4-Stream y luego escribir el video en el caché DDR3 del lado PS a través del VDMA oficial de Xilinx de 2 canales; solución de caché de imágenes; luego, el núcleo IP de superposición y fusión de video multicanal de desarrollo propio basado en HLS implementa la operación de superposición y fusión de video de 2 canales. Luego ingrese el núcleo IP AXI4-Stream To Video Out oficial de Xilinx para convertir el AXI4-; Transmita la transmisión de video a la transmisión de video nativa; luego envíe el video de superposición de fusión al módulo RGB a HDMI para convertir el video RGB888 a video HDMI y la resolución de salida es 1920x1080@60Hz. Para obtener efectos de visualización detallados, consulte el video de demostración de salida en. al final del artículo; la imagen finalmente se muestra a través de una pantalla HDMI; este proyecto requiere ejecutar el núcleo suave Zynq adecuado para empalmar video SDI a escenarios HDMI;

Código fuente del proyecto 2

El modelo FPGA de la placa de desarrollo es Xilinx–>Xilinx-Zynq7100–xc7z100ffg900-2. Hay dos fuentes de entrada, una es una cámara 3G-SDI con una resolución de 1920x1080@60Hz y la otra es HDMI a 3G-SDI; caja La caja está conectada a una cámara SDI analógica con una resolución de 1920x1080@60Hz; los dos videos de entrada se envían a la FPGA a través de los dos chips Gv8601a integrados para lograr una conversión de extremo único a ecualizador diferencial y balanceado; a través de los dos canales GTX, el vídeo SDI se deserializa en datos paralelos. Luego, a través de 2 canales del núcleo IP SMPTE SDI, el SDI se decodifica en 2 canales de datos BT1120 y luego, a través de 2 canales de BT1120 al módulo RGB, el BT1120 se convierte; en video RGB888 y luego a través de 2 canales de entrada de video oficial de Xilinx al núcleo IP AXI4-Stream para realizar la conversión de datos RGB888 a flujo de datos AXI4-Stream y luego escribir el video en el caché DDR3 del lado PS a través del VDMA oficial de Xilinx de 2 canales; solución de caché de imágenes; luego, el núcleo IP de superposición y fusión de video multicanal de desarrollo propio basado en HLS implementa la operación de superposición y fusión de video de 2 canales. Luego ingrese el núcleo IP AXI4-Stream To Video Out oficial de Xilinx para convertir el AXI4-; Transmita la transmisión de video a la transmisión de video nativa; luego envíe el video de superposición de fusión al módulo RGB a BT1120 para convertir el video RGB888 a video BT1120 y luego pase el núcleo IP SMPTE SD/HD/3G SDI que codifica el video BT1120 en video SDI; luego convierte datos paralelos SDI en señales en serie de alta velocidad a través de los recursos de alta velocidad GTX dentro de la FPGA y luego usa el chip Gv8500 integrado para implementar la conversión diferencial a controlador de un solo extremo. Después de la mejora, la resolución de salida es 1920x1080@60Hz; finalmente, se utiliza una caja SDI a HDMI para conectarse a una pantalla HDMI para visualización; este proyecto requiere ejecutar el núcleo suave Zynq adecuado para escenarios SDI a SDI;

Este proyecto y su código fuente incluyen partes escritas por mí y partes obtenidas de canales públicos en Internet (incluido CSDN, el sitio web oficial de Xilinx, el sitio web oficial de Altera, etc.). Si lo considera ofensivo, envíe un mensaje privado a. criticar y educar en base a esto, este proyecto El proyecto y su código fuente son solo para estudio e investigación personal por parte de lectores o fanáticos, y está prohibido su uso con fines comerciales si surgen problemas legales del uso comercial por parte de los propios lectores o fanáticos. , este blog y el blogger no tienen nada que ver con él, así que utilícelo con precaución. . .

La página de inicio de mi blog tiene una columna de video SDI, que está llena de código fuente de ingeniería de códecs FPGA SDI e introducción al blog; hay códecs SDI basados en GS2971/GS2972 y códecs SDI basados en recursos GTP/GTX; SDI, 6G-SDI, 12G-SDI, etc.; el enlace de dirección de la columna es el siguiente:

Haga clic para ir directamente

Este blog ha desarrollado una aplicación de superposición de fusión de video multicanal. He escrito un blog específicamente antes. El enlace de la dirección del blog es el siguiente.

Haga clic para ir directamente

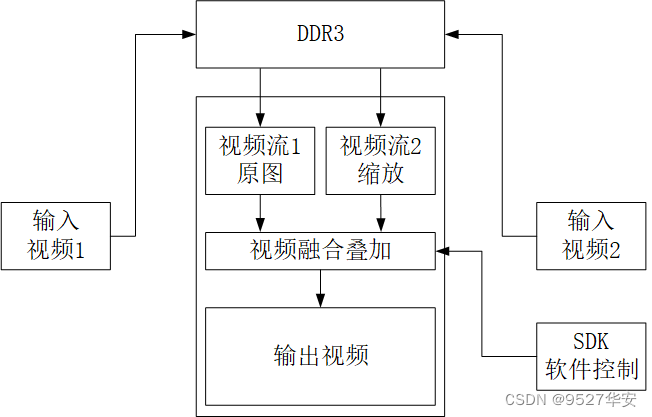

El diagrama de bloques del principio de diseño es el siguiente:

¡Aviso! ! ! !

¡Aviso! ! ! !

Flecha morada: ruta de salida 3G-SDI

Flecha roja: ruta de salida HDMI

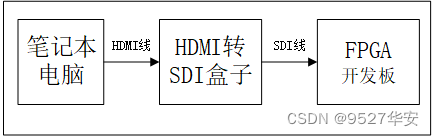

Hay dos dispositivos de entrada SDI, que están conectados a la interfaz de entrada de vídeo SDI de 2 vías de la placa de desarrollo FPGA; uno es una cámara 3G-SDI con una resolución de 1920x1080@60Hz. debido a este diseño, se adapta a tres tipos de videos SDI; otra caja HDMI a 3G-SDI, la caja está conectada a una computadora portátil para simular una cámara SDI. Las cámaras SDI son relativamente caras y los amigos con un presupuesto limitado pueden hacerlo; considere usar una caja HDMI a SDI para simular una cámara SDI que cuesta alrededor de 100 yuanes cuando usa una caja HDMI a SDI, la fuente de entrada puede ser una computadora portátil, es decir, use una computadora portátil para conectarse a la interfaz de entrada HDMI de la. Caja HDMI a SDI a través de un cable HDMI y luego use un cable SDI para conectar la caja HDMI a SDI. La interfaz de salida SDI a la placa de desarrollo FPGA es la siguiente:

El chip Gv8601a realiza las funciones de conversión de un solo extremo a ecualizador diferencial y balanceado. Se elige aquí el Gv8601a porque se basa en la solución oficial de Xilinx. Por supuesto, también se pueden utilizar otros tipos de dispositivos. El diagrama esquemático del ecualizador Gv8601a es el siguiente:

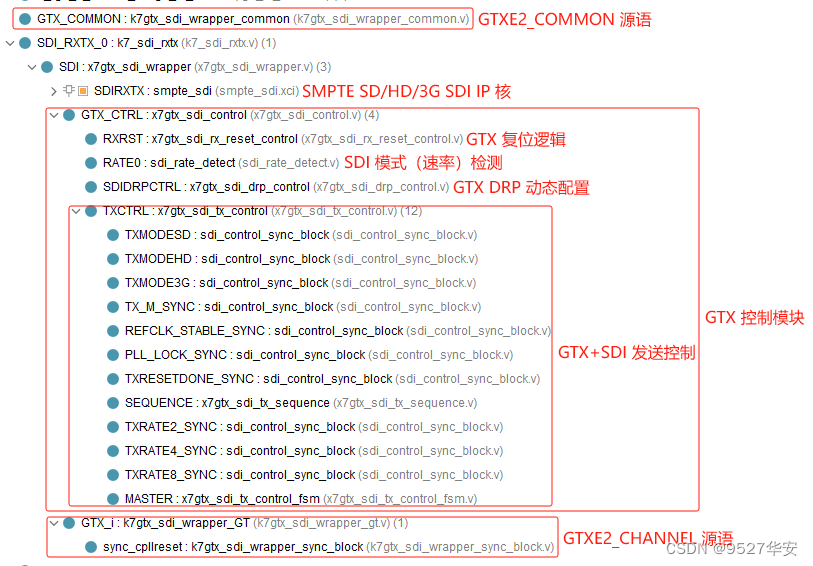

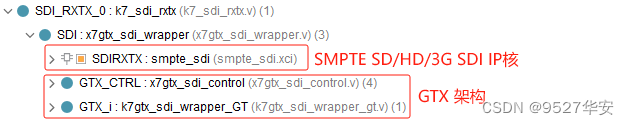

Este diseño utiliza los recursos exclusivos de procesamiento de señales de alta velocidad GTX de Xilinx para lograr la deserialización y serialización de señales de video diferenciales SDI. Para la recepción de video SDI, GTX desempeña el papel de deserialización, es decir, decodificar las señales diferenciales en serie de alta velocidad de entrada en digitales paralelas. para la transmisión de video SDI, GTX desempeña el papel de serialización, es decir, serializar la señal digital paralela de entrada en una señal diferencial en serie de alta velocidad. El uso de GTX generalmente requiere la creación de instancias del núcleo IP de GTX y configura la interfaz de usuario mediante vivado. interfaz, pero este diseño requiere reconocimiento automático y procesamiento adaptativo de videos SD-SDI, HD-SDI y 3G-SDI, por lo que GTX debe tener la función de cambiar dinámicamente la velocidad de línea. Esta función se puede configurar a través de la interfaz DRP. También se puede configurar a través de la interfaz de velocidad de GTX, por lo que no puede usar la interfaz UI de vivado para la configuración. En su lugar, puede crear una instancia directa de los lenguajes fuente GTXE2_CHANNEL y GTXE2_COMMON de GTX y usar los recursos de GTX directamente. para configurar dinámicamente la velocidad de la línea GTX, también necesita un módulo de control GTX. Este módulo se refiere al plan de diseño oficial de Xilinx y tiene las funciones de monitoreo dinámico del modo SDI, configuración dinámica de DRP, etc. El plan se refiere al diseño oficial de Xilinx; la estructura del código del módulo de serialización y deserialización GTX es la siguiente:

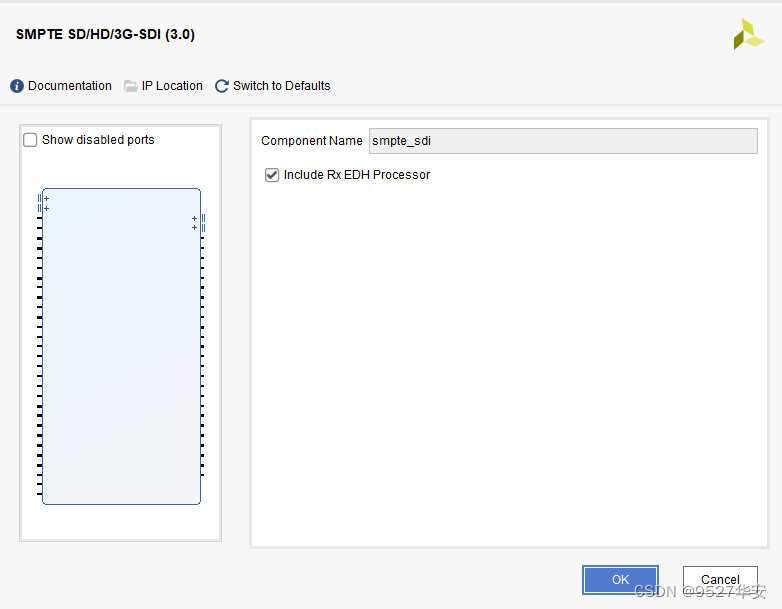

El núcleo IP SMPTE SD/HD/3G SDI es una IP única para la codificación y decodificación de video SDI de FPGA de la serie Xilinx. La configuración de IP es muy simple de usar. La interfaz UI de vivado es la siguiente.

El núcleo IP SMPTE SD/HD/3G SDI se debe usar con GTX. Para la recepción de video SDI, el IP recibe datos de GTX y luego decodifica el video SDI en la salida de video BT1120. Para la transmisión de video SDI, el IP recibe BT1120. datos de video del lado del usuario y luego codifica el video BT1120 en salida de video SDI; esta solución se refiere al diseño oficial de Xilinx; la estructura del código central SMPTE SD/HD/3G SDI IP es la siguiente:

La función del módulo BT1120 a RGB es convertir la salida de vídeo BT1120 mediante decodificación de núcleo IP SMPTE SD/HD/3G SDI en vídeo RGB888. Consta de tres módulos: módulo BT1120 a CEA861, módulo YUV422 a YUV444 y YUV444 a RGB888. Esta solución se refiere a Se adopta el diseño oficial de Xilinx. La estructura del código del módulo BT1120 a RGB es la siguiente:

La solución de caché de video de este diseño adopta la arquitectura de caché de imágenes VDMA oficial de Xilinx de 2 canales; el medio de caché es DDR3 del lado PS, el primer video SDI se escribe en DDR a través de VDMA y luego se lee y se envía al módulo de superposición de fusión de video; El segundo video SDI después de escribir en DDR a través de VDMA, no se lee, pero se lee desde DDR3 a través del módulo de superposición de fusión de video. Tomando el código fuente del proyecto 1 como ejemplo, VDMA está diseñado utilizando el diseño de bloques de Xilinx. vivado, como se muestra a continuación:

Para reducir la latencia, VDMA está configurado para almacenar en caché 1 fotograma, de la siguiente manera:

El diagrama de bloques del diseño de superposición de fusión de video multicanal es el siguiente:

La fusión y superposición de video multicanal se forma mediante la fusión y superposición del video subyacente y el video superpuesto. El video subyacente es el video de entrada del primer canal y el video superpuesto es el video escalado de los dos. los videos se fusionan y se emiten, que pueden ser El software SDK configura dinámicamente la transparencia de la fusión de video de 2 canales, el tamaño del zoom del video superpuesto, la posición de visualización del video superpuesto y otra información el diseño se implementa utilizando el; El código C ++ de la solución HLS se sintetiza en RTL y se encapsula en IP, que se puede usar en vivado Llame a IP. Para obtener detalles sobre esta solución, consulte mi blog anterior.

Haga clic para ir directamente

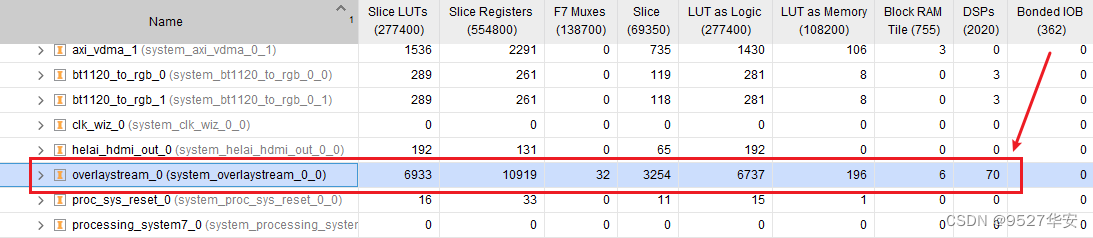

El uso integral de recursos de esta IP en vivado es el siguiente:

La superposición de fusión de video multicanal HLS necesita ejecutar el controlador y el programa de usuario en el SDK para funcionar correctamente. Proporcioné un programa en lenguaje C en el proyecto; consulte el código fuente del proyecto para obtener más detalles; La llamada de superposición de fusión de video del canal es la siguiente:

La arquitectura de salida de vídeo HDMI es la siguiente:

En referencia al diseño oficial de Xilinx, use la arquitectura VTC+AXI4-Stream To Video Out para convertir el video de salida de AXI4-Stream al formato nativo, luego use el módulo RGB888 a HDMI implementado en código verilog puro para convertir RGB888 a HDMI y finalmente mostrar; A través del monitor, la estructura del código del módulo RGB888 a HDMI es la siguiente:

Con respecto al módulo RGB888 a HDMI, consulte mi blog anterior, dirección del blog:Haga clic para ir directamente

La arquitectura de salida de video SDI primero debe convertir el AXI4-Stream leído por VDMA al formato nativo. Después de obtener el video RGB888, puede convertir el video RGB a BT1120 a BT1120.

En el modo de salida SDI, el reloj de píxeles del módulo de sincronización VGA lo proporciona el reloj del usuario emisor del núcleo IP SMPTE SD/HD/3G SDI. El reloj de píxeles es diferente en diferentes modos SDI. , el reloj de píxeles es de 148,5 M. En el modo HD-SDI 720P@60Hz, el reloj de píxeles es de 74,25 M;

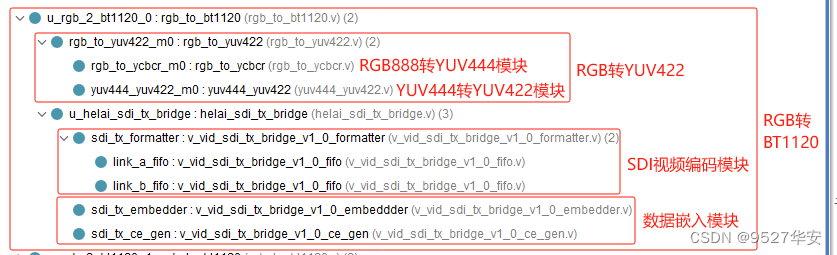

En el modo de salida SDI, es necesario utilizar el módulo RGB a BT1120. La función del módulo RGB a BT1200 es convertir el vídeo RGB del lado del usuario en vídeo BT1200 y enviarlo al SMPTE SD/HD/3G SDI IP; núcleo; el módulo RGB a BT1120 consta de un módulo RGB888 a YUV444, un módulo YUV444 a YUV422, un módulo de codificación de video SDI y un módulo de incrustación de datos. Esta solución se refiere al diseño oficial de Xilinx; la estructura del código del módulo BT1120 a RGB es. como sigue:

Estas dos partes comparten los módulos correspondientes con el proceso de recepción, que funcionalmente son el proceso inverso del proceso de recepción y no se describirán nuevamente;

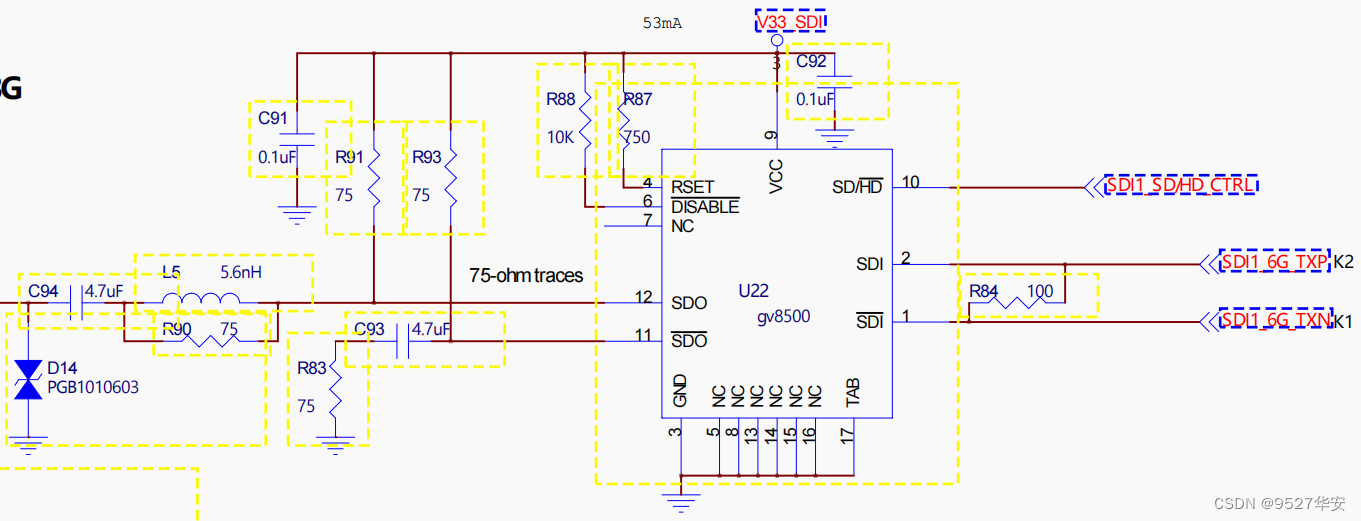

El chip Gv8500 realiza las funciones de conversión diferencial a controlador mejorado y de extremo único. El Gv8500 se elige aquí porque se basa en la solución oficial de Xilinx. Por supuesto, también se pueden utilizar otros tipos de dispositivos. El diagrama esquemático del controlador Gv8500 es el siguiente:

En el modo de salida SDI, es necesario utilizar una caja SDI a HDMI, porque el monitor que tengo en la mano no tiene una interfaz SDI, solo una interfaz HDMI. Por supuesto, esto solo se puede hacer si. su monitor tiene una interfaz SDI, puede directamente La conexión muestra que mi caja SDI a HDMI fue comprada en cierta tienda por menos de 100 yuanes;

Este blog proporciona 2 conjuntos de códigos fuente del proyecto. Tomando el código fuente del proyecto 1 como ejemplo, el diseño de Vivado Block Design es el siguiente. Otros proyectos son similares. El diseño de Block Design es parte de la arquitectura de caché de imágenes.

Tomando el código fuente del proyecto 1 como ejemplo, la estructura del código fuente del proyecto es la siguiente. Otros proyectos son similares:

El reloj lateral PL del código fuente del proyecto lo proporciona el núcleo suave de Zynq, por lo que es necesario ejecutar el SDK para iniciar Zynq. Además, los núcleos IP, como la superposición de fusión de video y VDMA, deben ejecutar controladores de software para funcionar correctamente. La estructura del código del software SDK es la siguiente:

La configuración en el código SDK es la siguiente, los usuarios pueden modificarla arbitrariamente según sus propias necesidades;

El primer vídeo es el vídeo de la capa inferior con una resolución de 1920x1080;

El video del segundo canal es el video superpuesto con una resolución de 1920x1080. Tome un área de 1000x800 de las coordenadas del video superpuesto (400, 200) como origen del video de fusión superpuesto;

Escale el vídeo de fusión superpuesto de 600x600 obtenido en el paso anterior a 960x540;

Superponga el video de fusión superpuesto de 960x540 en el paso anterior comenzando desde la coordenada (0,0) del video subyacente y establezca la transparencia de las capas subyacente y superpuesta en 80;

Modelo de placa de desarrollo FPGA: Xilinx-Zynq7100–xc7z100ffg900-2;

Entorno de desarrollo: Vivado2019.1;

Entrada: cámara 3G-SDI o caja HDMI a SDI, resolución 1920x1080@60Hz;

Salida: HDMI, resolución 1920x1080@60Hz;

Solución de almacenamiento en caché: solución VDMA oficial de Xilinx;

Medios de caché: DDR3 del lado PS;

Solución de superposición y fusión de vídeo: fusión y superposición de vídeo multicanal de desarrollo propio basado en HLS;

Función del proyecto: el propósito de este proyecto es permitir a los lectores dominar las capacidades de diseño de la FPGA de la serie Zynq para implementar SDI a HDMI, de modo que puedan trasplantar y diseñar sus propios proyectos;

Para conocer el diseño de bloques del proyecto y la arquitectura del código del proyecto, consulte la sección "Arquitectura del código fuente del proyecto" en el Capítulo 3;

El consumo de recursos y el consumo de energía del proyecto son los siguientes:

Modelo de placa de desarrollo FPGA: Xilinx-Zynq7100–xc7z100ffg900-2;

Entorno de desarrollo: Vivado2019.1;

Entrada: cámara 3G-SDI o caja HDMI a SDI, resolución 1920x1080@60Hz;

Salida: 3G-SDI, resolución 1920x1080@60Hz;

Solución de almacenamiento en caché: solución VDMA oficial de Xilinx;

Medios de caché: DDR3 del lado PS;

Solución de superposición y fusión de vídeo: fusión y superposición de vídeo multicanal de desarrollo propio basado en HLS;

Función del proyecto: el propósito de este proyecto es permitir a los lectores dominar las capacidades de diseño de la FPGA de la serie Zynq para implementar SDI a HDMI, de modo que puedan trasplantar y diseñar sus propios proyectos;

Para conocer el diseño de bloques del proyecto y la arquitectura del código del proyecto, consulte la sección "Arquitectura del código fuente del proyecto" en el Capítulo 3;

El consumo de recursos y el consumo de energía del proyecto son los siguientes:

1: Si su versión vivado es consistente con la versión vivado de este proyecto, abra el proyecto directamente;

2: Si su versión de vivado es inferior a la versión de vivado de este proyecto, debe abrir el proyecto y hacer clic en Archivo -> Guardar como; sin embargo, este método no es seguro. La forma más segura es actualizar su versión de vivado a vivado. de este proyecto.

3: Si su versión vivado es superior a la versión vivado de este proyecto, la solución es la siguiente:

Después de abrir el proyecto, encontrará que las IP están bloqueadas, de la siguiente manera:

En este momento, necesita actualizar la IP. Los pasos son los siguientes:

Si su modelo de FPGA no coincide con el mío, debe cambiar el modelo de FPGA de la siguiente manera:

Después de cambiar el modelo FPGA, necesita actualizar la IP. El método para actualizar la IP se describió anteriormente;

1: Dado que el DDR de cada placa no es necesariamente exactamente el mismo, la IP MIG debe configurarse de acuerdo con su propio diagrama esquemático. Incluso puede eliminar directamente la MIG de mi proyecto original y volver a agregar la IP y reconfigurarla;

2: Modifique las restricciones de los pines de acuerdo con su propio diagrama esquemático y modifíquelo en el archivo xdc;

3: Para trasplantar FPGA puro a Zynq, debe agregar el núcleo blando de zynq al proyecto;

El equipo que es necesario preparar es el siguiente:

placa de desarrollo FPGA;

Cámara SDI o caja HDMI a SDI;

Caja SDI a HDMI;

pantalla HDMI;

Mi placa de desarrollo está conectada de la siguiente manera:

Tomando el código fuente 1 del proyecto como ejemplo, el resultado es el siguiente:

Superposición de fusión de vídeo Zynq-SDI

Bonificación: Adquisición del código de ingeniería

El código es demasiado grande y no se puede enviar por correo electrónico. Se enviará a través de un determinado enlace de disco de red.

Cómo obtener información: de forma privada o en la tarjeta de presentación V al final del artículo.

La información del disco de red es la siguiente:

Además, muchos amigos le han dado muchas opiniones y sugerencias a este blogger, con la esperanza de enriquecer el contenido y las opciones del servicio. Debido a que diferentes amigos tienen diferentes necesidades, este blogger también brinda los siguientes servicios: