le mie informazioni di contatto

Posta[email protected]

2024-07-12

한어Русский языкEnglishFrançaisIndonesianSanskrit日本語DeutschPortuguêsΕλληνικάespañolItalianoSuomalainenLatina

Attualmente esistono due soluzioni per FPGA per implementare la codifica e decodifica video SDI: una consiste nell'utilizzare chip di codifica e decodifica dedicati, come il tipico ricevitore GS2971 e il trasmettitore GS2972. Il vantaggio è la semplicità. Ad esempio, il ricevitore GS2971 decodifica SDI in YCrCb422 parallelo e il GS2972 trasmette Il dispositivo codifica direttamente il YCrCb422 parallelo in video SDI. Lo svantaggio è che il costo è relativamente alto. Puoi cercare i prezzi di GS2971 e GS2972 su Baidu Dipartimento delle risorse logiche FPGA per implementare la codifica e la decodifica SDI e utilizzare le risorse GTP/GTX dell'FPGA della serie Xilinx. Per ottenere la deserializzazione, utilizzare le risorse SDI SMPTE dell'FPGA della serie Xilinx per implementare la codifica e la decodifica SDI le risorse vengono utilizzate in modo ragionevole e le risorse GTP/GTX non vengono utilizzate invano. Lo svantaggio è che l'operazione è più difficile e richiede un livello tecnico più elevato da parte degli sviluppatori FPGA. È interessante notare che queste due soluzioni hanno soluzioni corrispondenti qui su questo blog, incluse schede di sviluppo FPGA hardware, codice sorgente ingegneristico, ecc.

Questo progetto si basa sulla scheda di sviluppo FPGA Zynq7100 della serie Zynq per implementare la codifica e decodifica video SDI + ridimensionamento delle immagini + giunzione video multicanale. Sono presenti due sorgenti di ingresso, una è una fotocamera 3G-SDI con una risoluzione di 1920x1080@. 60Hz e è possibile utilizzare anche HD-SDI o una fotocamera SD-SDI, poiché questo design è adattivo a tre video SDI un'altra scatola da HDMI a 3G-SDI, la scatola è collegata a un laptop per simulare una fotocamera SDI; I video SDI sono collegati alla scheda di sviluppo FPGA tramite cavi coassiali con presa BNC, quindi il video coassiale passa attraverso il chip Gv8601a integrato per realizzare le funzioni di conversione single-ended in EQ differenziale e bilanciato, quindi il segnale video SDI differenziale entra nella GTX risorsa ad alta velocità all'interno dell'FPGA per realizzare la conversione dei dati da seriale a parallelo ad alta velocità. Bo la chiama deserializzazione; il video parallelo deserializzato viene quindi inviato all'esclusivo core IP SMPTE SD/HD/3G dell'FPGA della serie Xilinx per eseguire l'SDI. operazione di decodifica video e uscita video BT1120 A questo punto, l'operazione di decodifica video SDI è stata completata ed è possibile eseguire le operazioni di routine di elaborazione delle immagini;

Lo scopo di questo progetto è quello di produrre video SDI decodificato dopo il ridimensionamento dell'immagine + fusione e sovrapposizione video multicanale. In risposta alle attuali esigenze di progetto tradizionali sul mercato, questo blog ha progettato due metodi di output, uno è l'uscita HDMI e l'altro è un'uscita 3G -SDI, entrambi i metodi richiedono la decodifica del video BT1120 per essere convertito in RGB e operazioni di memorizzazione nella cache delle immagini; questo progetto utilizza il modulo da BT1120 a RGB per ottenere la conversione del formato video per l'implementazione dell'architettura di cache delle immagini VDMA ufficiale Xilinx; caching e memorizzazione nella cache delle immagini Il supporto è DDR3 lato PS integrato; il primo video SDI viene scritto su DDR tramite VDMA e quindi letto e inviato al modulo di sovrapposizione di fusione video. Il secondo video SDI non viene letto dopo essere stato scritto su DDR VDMA, ma viene sovrapposto tramite fusione video. Il modulo legge da DDR3. A questo punto, il video a 2 canali è entrato nel modulo di fusione e sovrapposizione video per l'elaborazione di fusione e sovrapposizione, quindi entra nel modulo di invio HDMI per emettere il display HDMI , che è il metodo di uscita HDMI; oppure il formato video viene realizzato tramite la conversione del modulo da RGB a BT1120, quindi il video entra nel core IP SMPTE SD/HD/3G SDI, esegue operazioni di codifica video SDI ed emette video SDI, quindi passa attraverso le risorse GTX ad alta velocità all'interno dell'FPGA per realizzare la conversione dei dati paralleli in seriale ad alta velocità, che questo blog chiama seriale, il segnale differenziale ad alta velocità entra quindi nel chip Gv8500 integrato per realizzare le funzioni di conversione differenziale in singolo -ended e miglioramento del driver Il video SDI viene emesso tramite la presa BNC della scheda di sviluppo FPGA ed è collegato al box SDI-HDMI tramite un cavo coassiale al display HDMI Questo è il metodo di uscita SDI fornito 2 insiemi di codici sorgente del progetto, come segue:

I due gruppi di codici sorgente del progetto sopra menzionati sono spiegati come segue per facilitare la comprensione dei lettori:

Codice sorgente del progetto 1

Il modello FPGA della scheda di sviluppo è Xilinx–>Xilinx-Zynq7100–xc7z100ffg900-2 ci sono due sorgenti di ingresso, una è una fotocamera 3G-SDI con una risoluzione di 1920x1080 a 60Hz e l'altra è un HDMI a 3G-SDI; box. Il box è collegato a un laptop. Telecamera SDI analogica con una risoluzione di 1920x1080 a 60 Hz; i due video in ingresso vengono inviati all'FPGA attraverso i due chip Gv8601a integrati per ottenere la conversione single-ended in EQ differenziale e bilanciato; attraverso i due canali GTX, il video SDI viene deserializzato in dati paralleli; quindi attraverso 2 canali del core IP SMPTE SDI, l'SDI viene decodificato in 2 canali di dati BT1120 quindi attraverso 2 canali del modulo BT1120 RGB, il BT1120 viene convertito nel video RGB888; quindi attraverso 2 canali di ingresso video ufficiale Xilinx nel core IP AXI4-Stream per realizzare la conversione del flusso di dati RGB888 in AXI4-Stream; quindi scrivere il video nella cache DDR3 lato PS tramite il VDMA ufficiale Xilinx a 2 canali soluzione di cache delle immagini; quindi il core IP di fusione e sovrapposizione video multicanale sviluppato autonomamente basato su HLS implementa l'operazione di fusione e sovrapposizione video a 2 canali, quindi inserire il core IP AXI4-Stream To Video Out ufficiale di Xilinx per convertire AXI4-; Trasmetti il flusso video al flusso video nativo; quindi invia il video fusion overlay al modulo da RGB a HDMI per convertire il video RGB888 in video HDMI e la risoluzione di uscita è 1920x1080 a 60 Hz. Per gli effetti di visualizzazione dettagliati, consultare il video dimostrativo dell'output all'indirizzo alla fine dell'articolo; l'immagine viene finalmente visualizzata tramite un display HDMI; questo progetto richiede l'esecuzione del soft core Zynq adatto per la giunzione di video SDI a scenari HDMI;

Codice sorgente del progetto 2

Il modello FPGA della scheda di sviluppo è Xilinx–>Xilinx-Zynq7100–xc7z100ffg900-2 ci sono due sorgenti di ingresso, una è una fotocamera 3G-SDI con una risoluzione di 1920x1080 a 60Hz e l'altra è un HDMI a 3G-SDI; box. Il box è collegato a un laptop. Telecamera SDI analogica con una risoluzione di 1920x1080 a 60 Hz; i due video in ingresso vengono inviati all'FPGA attraverso i due chip Gv8601a integrati per ottenere la conversione single-ended in EQ differenziale e bilanciato; attraverso i due canali GTX, il video SDI viene deserializzato in dati paralleli; quindi attraverso 2 canali del core IP SMPTE SDI, l'SDI viene decodificato in 2 canali di dati BT1120 quindi attraverso 2 canali del modulo BT1120 RGB, il BT1120 viene convertito nel video RGB888; quindi attraverso 2 canali di ingresso video ufficiale Xilinx nel core IP AXI4-Stream per realizzare la conversione del flusso di dati RGB888 in AXI4-Stream; quindi scrivere il video nella cache DDR3 lato PS tramite il VDMA ufficiale Xilinx a 2 canali soluzione di cache delle immagini; quindi il core IP di fusione e sovrapposizione video multicanale sviluppato autonomamente basato su HLS implementa l'operazione di fusione e sovrapposizione video a 2 canali, quindi inserire il core IP AXI4-Stream To Video Out ufficiale di Xilinx per convertire AXI4-; Trasmettere il flusso video al flusso video nativo; quindi inviare il video overlay di fusione al modulo RGB a BT1120 per convertire il video RGB888 in video BT1120; quindi passare il core IP SMPTE SD/HD/3G SDI per codificare il video BT1120 in video SDI; quindi converte i dati paralleli SDI in segnali seriali ad alta velocità attraverso le risorse GTX ad alta velocità all'interno dell'FPGA; quindi utilizza il chip Gv8500 integrato per implementare la conversione differenziale in single-ended e driver Dopo il miglioramento, la risoluzione di uscita è 1920x1080 a 60Hz; infine, viene utilizzato un box SDI a HDMI per connettersi a un display HDMI per la visualizzazione; questo progetto richiede l'esecuzione del soft core Zynq adatto per scenari SDI a SDI;

Questo progetto e il suo codice sorgente includono sia parti scritte da me che parti ottenute da canali pubblici su Internet (incluso CSDN, sito ufficiale Xilinx, sito ufficiale Altera, ecc.). Se ritieni che sia offensivo, invia un messaggio privato a criticare ed educare; sulla base di ciò, questo progetto e il suo codice sorgente sono solo per lo studio e la ricerca personale da parte di lettori o fan e non possono essere utilizzati per scopi commerciali se sorgono problemi legali dall'uso commerciale da parte dei lettori o dei fan stessi , questo blog e il blogger non hanno nulla a che fare con esso, quindi utilizzalo con cautela. . .

La home page del mio blog ha una colonna video SDI, che è piena di codice sorgente di ingegneria SDI del codec FPGA e introduzione al blog, ci sono codec SDI basati su GS2971/GS2972 e codec SDI basati su risorse GTP/GTX; SDI, 6G-SDI, 12G-SDI, ecc.; il collegamento dell'indirizzo della colonna è il seguente:

Fare clic per andare direttamente

Questo blog ha sviluppato autonomamente un'applicazione di sovrapposizione di fusione video multicanale. Ho già scritto un blog specifico in precedenza. Il collegamento all'indirizzo del blog è il seguente:

Fare clic per andare direttamente

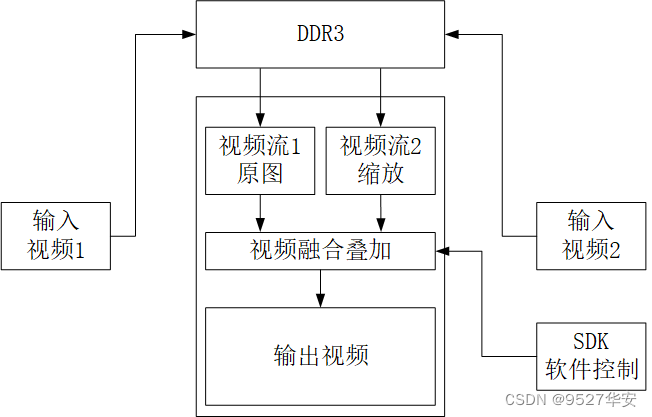

Lo schema a blocchi del principio di progettazione è il seguente:

Avviso! ! ! !

Avviso! ! ! !

Freccia viola: percorso di uscita 3G-SDI

Freccia rossa: percorso di uscita HDMI

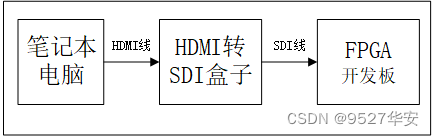

Sono presenti due dispositivi di ingresso SDI, collegati all'interfaccia di ingresso video SDI a 2 vie della scheda di sviluppo FPGA; uno è anche una telecamera 3G-SDI con una risoluzione di 1920x1080 a 60 Hz essere utilizzato a causa di questo design È adattivo a tre tipi di video SDI; un altro box HDMI a 3G-SDI, il box è collegato a un laptop per simulare una fotocamera SDI sono relativamente costose e gli amici con un budget limitato possono farlo; considerare l'utilizzo di un box da HDMI a SDI per simulare una fotocamera SDI costa circa 100 yuan; quando si utilizza un box da HDMI a SDI, la sorgente di ingresso può essere un laptop, ovvero utilizzare un laptop per connettersi all'interfaccia di ingresso HDMI del. Scatola da HDMI a SDI tramite un cavo HDMI, quindi utilizzare un cavo SDI per collegare la scatola da HDMI a SDI. L'interfaccia di uscita SDI alla scheda di sviluppo FPGA è la seguente:

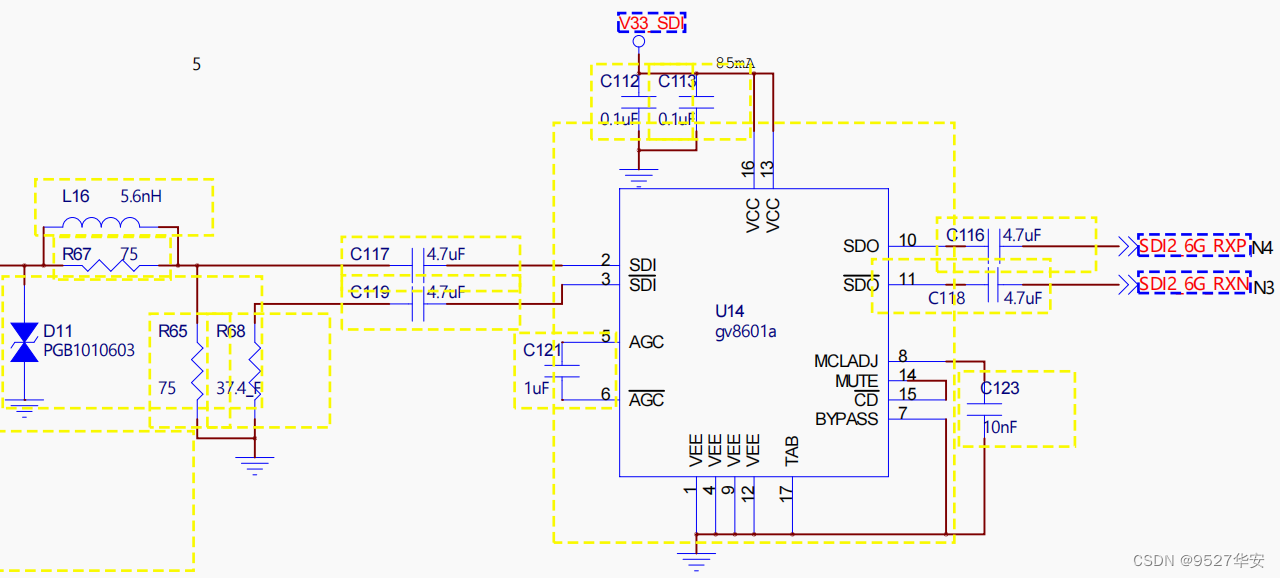

Il chip Gv8601a realizza le funzioni di conversione single-ended in equalizzatore differenziale e bilanciato. Il Gv8601a è stato scelto qui perché si basa sulla soluzione ufficiale Xilinx. Naturalmente possono essere utilizzati anche altri tipi di dispositivi. Il diagramma schematico dell'equalizzatore Gv8601a è il seguente:

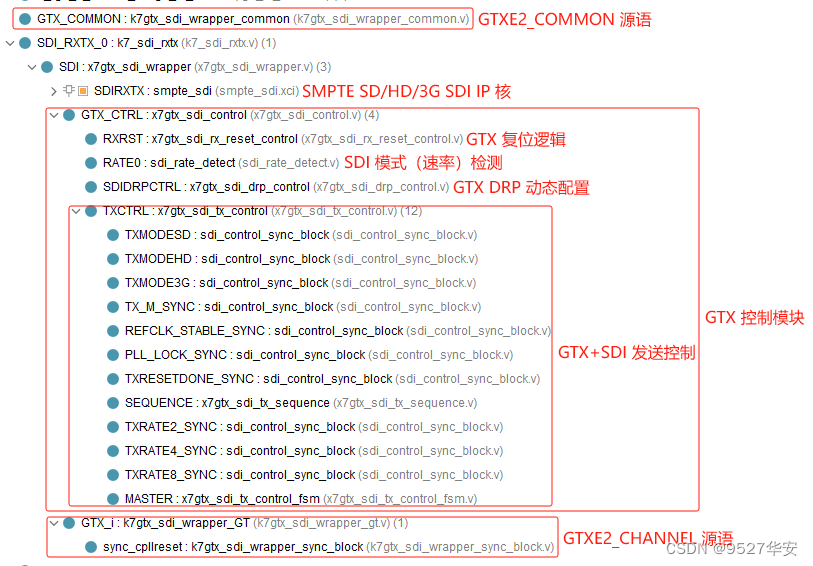

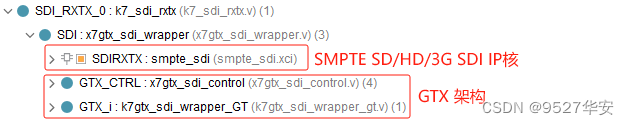

Questo progetto utilizza le esclusive risorse di elaborazione del segnale ad alta velocità GTX di Xilinx per ottenere la deserializzazione e la serializzazione dei segnali video differenziali SDI. Per la ricezione video SDI, GTX svolge il ruolo di deserializzazione, ovvero decodifica i segnali differenziali seriali ad alta velocità di ingresso in digitali paralleli. segnale; per la trasmissione video SDI, GTX svolge il ruolo di serializzazione, ovvero serializza il segnale digitale parallelo in ingresso in un segnale differenziale seriale ad alta velocità; l'uso di GTX generalmente richiede l'istanziazione del core GTX IP, tramite vivado Configura l'interfaccia utente interfaccia, ma questo design richiede il riconoscimento automatico e l'elaborazione adattiva dei video SD-SDI, HD-SDI e 3G-SDI, quindi GTX deve avere la funzione di modificare dinamicamente la velocità di linea. Questa funzione può essere configurata tramite l'interfaccia DRP. Può anche essere configurato tramite l'interfaccia di velocità di GTX, quindi non è possibile utilizzare l'interfaccia utente di vivado per la configurazione. Invece, è possibile istanziare direttamente i linguaggi di origine GTXE2_CHANNEL e GTXE2_COMMON di GTX e utilizzare direttamente le risorse GTX. per configurare dinamicamente la velocità di linea GTX, è necessario anche un modulo di controllo GTX, questo modulo si riferisce al piano di progettazione ufficiale di Xilinx e ha le funzioni di monitoraggio dinamico della modalità SDI, configurazione dinamica di DRP, ecc.; il piano si riferisce al progetto ufficiale di Xilinx; la struttura del codice del modulo di deserializzazione e serializzazione GTX è la seguente:

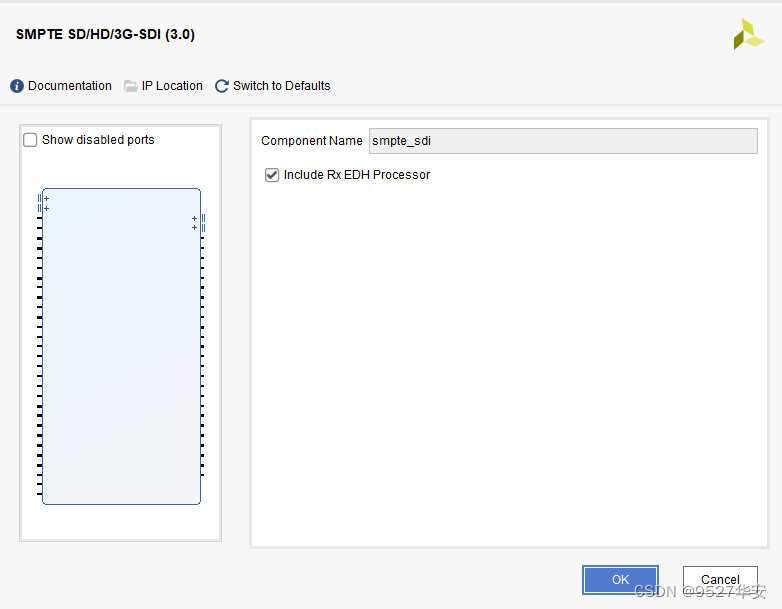

Il core IP SMPTE SD/HD/3G SDI è un IP unico per la codifica e decodifica video SDI degli FPGA della serie Xilinx. La configurazione IP è molto semplice da usare. L'interfaccia utente di vivado è la seguente:

Il core IP SMPTE SD/HD/3G SDI deve essere utilizzato con GTX Per la ricezione video SDI, l'IP riceve i dati da GTX, quindi decodifica il video SDI nell'uscita video BT1120. Per la trasmissione video SDI, l'IP L'IP riceve BT1120 dati video dal lato utente, quindi codifica il video BT1120 nell'uscita video SDI; questa soluzione si riferisce al design ufficiale Xilinx, la struttura del codice core IP SMPTE SD/HD/3G è la seguente:

La funzione del modulo da BT1120 a RGB è quella di convertire l'uscita video BT1120 tramite decodifica core IP SMPTE SD/HD/3G SDI in video RGB888. È composto da tre moduli: modulo da BT1120 a CEA861, modulo da YUV422 a YUV444 e modulo da YUV444 a RGB888. Questa soluzione si riferisce al design ufficiale Xilinx adottato, la struttura del codice del modulo da BT1120 a RGB è la seguente:

La soluzione di cache video di questo progetto adotta l'architettura di cache delle immagini VDMA ufficiale Xilinx a 2 canali; il supporto della cache è DDR3 lato PS; il primo video SDI viene scritto in DDR tramite VDMA e quindi letto e inviato al modulo di sovrapposizione di fusione video Il secondo video SDI Dopo essere stato scritto su DDR tramite VDMA, non viene letto, ma viene letto da DDR3 tramite il modulo di sovrapposizione di fusione video. Prendendo come esempio il codice sorgente del progetto 1, VDMA è progettato utilizzando il Block Design di Xilinx vivado, come mostrato di seguito:

Per ridurre la latenza, VDMA è impostato per memorizzare nella cache 1 frame, come segue:

Il diagramma a blocchi del progetto di sovrapposizione della fusione video multicanale è il seguente:

La fusione e la sovrapposizione video multicanale sono formate dalla fusione e sovrapposizione del video sottostante e del video sovrapposto. Il video sottostante è il video di input del primo canale e il video sovrapposto è il video scalato del secondo canale i video vengono fusi insieme e l'output può essere Il software SDK configura dinamicamente la trasparenza della fusione video a 2 canali, la dimensione dello zoom del video in sovrapposizione, la posizione di visualizzazione del video in sovrapposizione e altre informazioni; il design viene implementato utilizzando il Codice C++ della soluzione HLS, sintetizzato in RTL e incapsulato in IP, che può essere utilizzato in vivado Call the IP. Per dettagli su questa soluzione, fare riferimento al mio blog precedente. Il collegamento al blog è il seguente:

Fare clic per andare direttamente

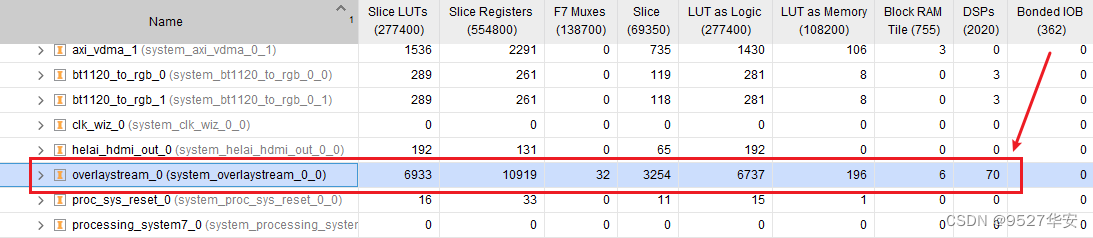

L'utilizzo completo delle risorse di questo IP in vivado è il seguente:

L'overlay di fusione video multicanale HLS deve eseguire il driver e il programma utente nell'SDK per funzionare correttamente. Ho fornito un programma in linguaggio C nel progetto, fai riferimento al codice sorgente del progetto per i dettagli; La chiamata in sovrapposizione della fusione video del canale è la seguente:

L'architettura dell'uscita video HDMI è la seguente:

Facendo riferimento al design ufficiale Xilinx, utilizzare l'architettura VTC+AXI4-Stream To Video Out per convertire il video in uscita da AXI4-Stream al formato nativo; quindi utilizzare il modulo da RGB888 a HDMI implementato in puro codice Verilog per convertire RGB888 in HDMI e infine visualizzare attraverso il monitor, la struttura del codice del modulo da RGB888 a HDMI è la seguente:

Per quanto riguarda il modulo da RGB888 a HDMI, fare riferimento al mio blog precedente, indirizzo del blog:Fare clic per andare direttamente

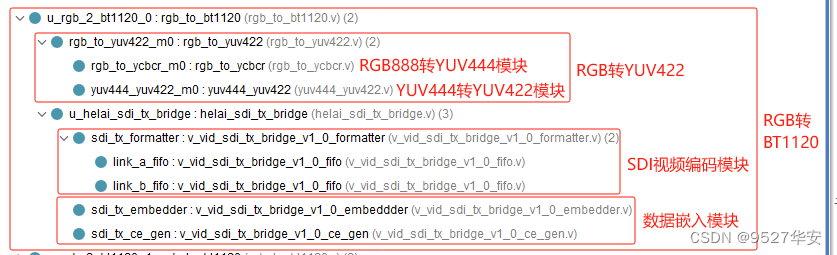

L'architettura dell'uscita video SDI deve prima convertire il flusso AXI4 letto da VDMA nel formato nativo. Dopo aver ottenuto il video RGB888, può quindi convertire il video RGB in BT1120 in BT1120. L'architettura è la seguente:

Nella modalità di uscita SDI, il clock dei pixel del modulo di temporizzazione VGA è fornito dall'orologio dell'utente mittente del core IP SMPTE SD/HD/3G SDI. Il clock dei pixel è diverso nelle diverse modalità SDI , il pixel clock è 148,5 M. Nella modalità HD-SDI 720P@60Hz, il pixel clock è 74,25 M;

Nella modalità di uscita SDI, è necessario utilizzare il modulo da RGB a BT1120; la funzione del modulo da RGB a BT1200 è convertire il video RGB sul lato utente in video BT1200 e trasmetterlo all'IP SMPTE SD/HD/3G SDI. core; il modulo da RGB a BT1120 è costituito da un modulo da RGB888 a YUV444, un modulo da YUV444 a YUV422, un modulo di codifica video SDI e un modulo di incorporamento dei dati. Questa soluzione si riferisce al design ufficiale di Xilinx; come segue:

Queste due parti condividono con il processo ricevente i corrispondenti moduli, che sono funzionalmente il processo inverso del processo ricevente e non verranno nuovamente descritti;

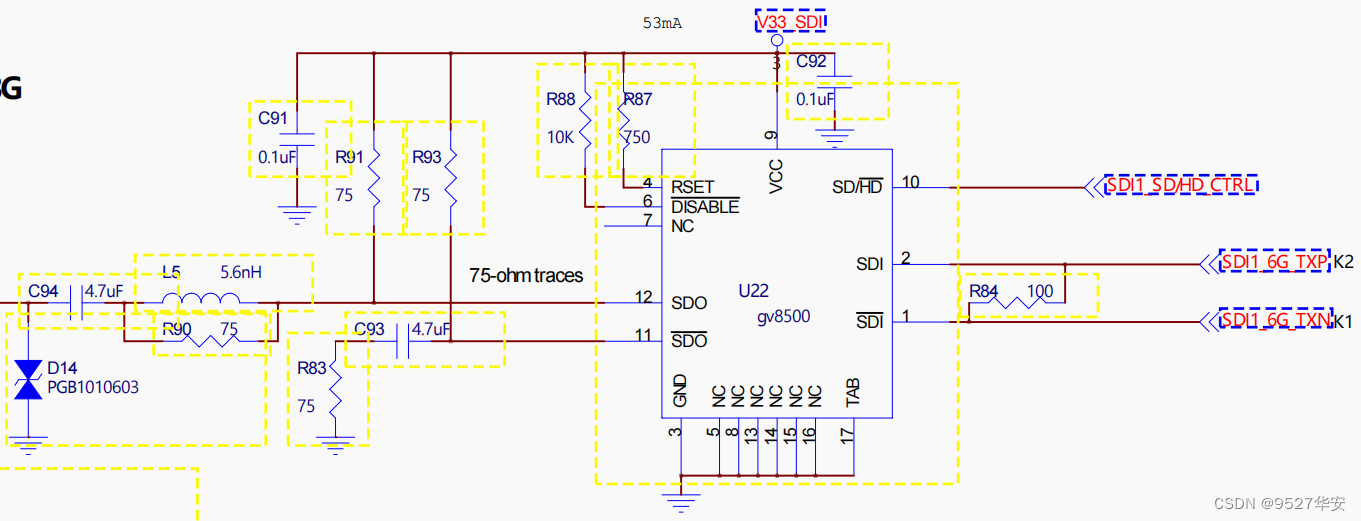

Il chip Gv8500 realizza le funzioni di conversione differenziale in driver single-ended e potenziato. Il Gv8500 è stato scelto qui perché si basa sulla soluzione ufficiale Xilinx. Naturalmente è possibile utilizzare anche altri tipi di dispositivi. Il diagramma schematico del driver Gv8500 è il seguente:

Nella modalità di uscita SDI, è necessario utilizzare un box SDI-HDMI, perché il monitor che ho in mano non ha un'interfaccia SDI, solo un'interfaccia HDMI. Per visualizzare video SDI, questo può essere fatto solo se il tuo monitor ha un'interfaccia SDI, puoi farlo direttamente La connessione mostra che il mio box SDI-HDMI è stato acquistato in un determinato negozio per meno di 100 yuan;

Questo blog fornisce 2 set di codici sorgente del progetto. Prendendo come esempio il codice sorgente del progetto 1, il design di vivado Block Design è il seguente. Altri progetti sono simili.

Prendendo come esempio il codice sorgente del progetto 1, la struttura del codice sorgente del progetto è la seguente. Altri progetti sono simili:

L'orologio laterale PL del codice sorgente del progetto è fornito dal soft core Zynq, quindi è necessario eseguire l'SDK per avviare Zynq. Inoltre, i core IP come l'overlay di fusione video e VDMA devono eseguire i driver software per funzionare correttamente La struttura del codice software SDK è la seguente:

La configurazione nel codice SDK è la seguente, gli utenti possono modificarla arbitrariamente in base alle proprie esigenze;

Il primo video è il video del livello inferiore con una risoluzione di 1920x1080;

Il video del secondo canale è il video in sovrapposizione con una risoluzione di 1920x1080. Prendi un'area 1000x800 dalle coordinate del video in sovrapposizione (400, 200) come origine del video di fusione in sovrapposizione.

Ridimensiona il video di fusione sovrapposto 600x600 ottenuto nel passaggio precedente a 960x540;

Sovrapponi il video di fusione sovrapposto 960x540 nel passaggio precedente a partire dalla coordinata (0,0) del video sottostante e imposta la trasparenza dei livelli sottostanti e di sovrapposizione su 80;

Modello FPGA della scheda di sviluppo: Xilinx-Zynq7100–xc7z100ffg900-2;

Ambiente di sviluppo: Vivado2019.1;

Ingresso: fotocamera 3G-SDI o box HDMI-SDI, risoluzione 1920x1080 a 60 Hz;

Uscita: HDMI, risoluzione 1920x1080@60Hz;

Soluzione di caching: soluzione VDMA ufficiale Xilinx;

Supporto cache: DDR3 lato PS;

Soluzione di fusione e sovrapposizione video: fusione e sovrapposizione video multicanale auto-sviluppate basate su HLS;

Ruolo del progetto: lo scopo di questo progetto è consentire ai lettori di padroneggiare le capacità di progettazione degli FPGA della serie Zynq per implementare SDI su HDMI, in modo che possano trapiantare e progettare i propri progetti;

Per la progettazione a blocchi del progetto e l'architettura del codice del progetto, fare riferimento alla sezione "Architettura del codice sorgente del progetto" nel capitolo 3;

Il consumo di risorse e il consumo energetico del progetto sono i seguenti:

Modello FPGA della scheda di sviluppo: Xilinx-Zynq7100–xc7z100ffg900-2;

Ambiente di sviluppo: Vivado2019.1;

Ingresso: fotocamera 3G-SDI o box HDMI-SDI, risoluzione 1920x1080 a 60 Hz;

Uscita: 3G-SDI, risoluzione 1920x1080@60Hz;

Soluzione di caching: soluzione VDMA ufficiale Xilinx;

Supporto cache: DDR3 lato PS;

Soluzione di fusione e sovrapposizione video: fusione e sovrapposizione video multicanale auto-sviluppate basate su HLS;

Ruolo del progetto: lo scopo di questo progetto è consentire ai lettori di padroneggiare le capacità di progettazione degli FPGA della serie Zynq per implementare SDI su HDMI, in modo che possano trapiantare e progettare i propri progetti;

Per la progettazione a blocchi del progetto e l'architettura del codice del progetto, fare riferimento alla sezione "Architettura del codice sorgente del progetto" nel capitolo 3;

Il consumo di risorse e il consumo energetico del progetto sono i seguenti:

1: Se la tua versione di vivado è coerente con la versione di vivado di questo progetto, apri direttamente il progetto;

2: Se la tua versione di vivado è inferiore alla versione di vivado di questo progetto, devi aprire il progetto e fare clic su File -> Salva con nome; tuttavia, questo metodo non è sicuro è aggiornare la tua versione di vivado a vivado di questo progetto. versione o successiva;

3: Se la tua versione di vivado è superiore alla versione di vivado di questo progetto, la soluzione è la seguente:

Dopo aver aperto il progetto, scoprirai che gli IP sono bloccati, come segue:

A questo punto, è necessario aggiornare l'IP. I passaggi sono i seguenti:

Se il tuo modello FPGA non è coerente con il mio, devi modificare il modello FPGA come segue:

Dopo aver modificato il modello FPGA, è necessario aggiornare l'IP. Il metodo di aggiornamento dell'IP è stato descritto in precedenza;

1: Poiché il DDR di ciascuna scheda non è necessariamente esattamente lo stesso, l'IP MIG deve essere configurato secondo il proprio diagramma schematico. Puoi anche eliminare direttamente il MIG del mio progetto originale e aggiungere nuovamente l'IP e riconfigurarlo;

2: Modifica i vincoli dei pin in base al tuo diagramma schematico e modificalo nel file xdc;

3: Per trapiantare FPGA puro su Zynq, è necessario aggiungere il soft core zynq al progetto;

L'attrezzatura da preparare è la seguente:

scheda di sviluppo FPGA;

Fotocamera SDI o box HDMI-SDI;

Scatola da SDI a HDMI;

Visualizzazione HDMI;

La mia scheda di sviluppo è collegata come segue:

Prendendo come esempio il codice sorgente del progetto 1, l'output è il seguente:

Sovrapposizione di fusione video Zynq-SDI

Bonus: acquisizione del codice di ingegneria

Il codice è troppo grande e non può essere inviato tramite e-mail. Verrà inviato tramite un determinato collegamento al disco di rete.

Come ottenere informazioni: in privato, oppure con il biglietto da visita V a fine articolo.

Le informazioni sul disco di rete sono le seguenti:

Inoltre, molti amici hanno fornito a questo blogger molte opinioni e suggerimenti, sperando di arricchire il contenuto e le opzioni del servizio. Poiché amici diversi hanno esigenze diverse, questo blogger fornisce anche i seguenti servizi: